插播:英诺赛科、能华半导体、致能科技、京东方华灿光电、镓奥科技等已确认参编《2024-2025氮化镓(GaN)产业调研白皮书》,演讲或摊位咨询请联系许若冰(hangjiashuo999)。

插播:英诺赛科、能华半导体、致能科技、京东方华灿光电、镓奥科技等已确认参编《2024-2025氮化镓(GaN)产业调研白皮书》,演讲或摊位咨询请联系许若冰(hangjiashuo999)。

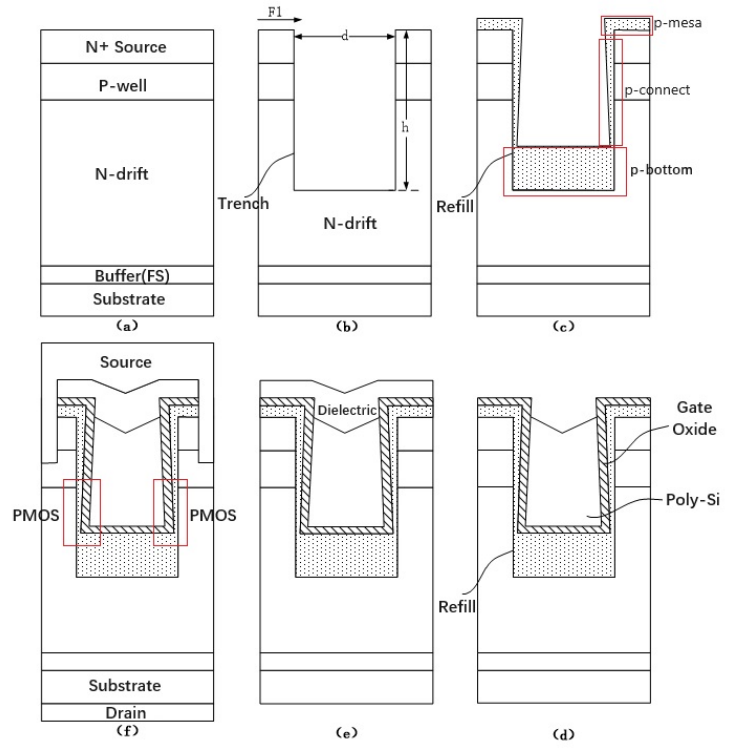

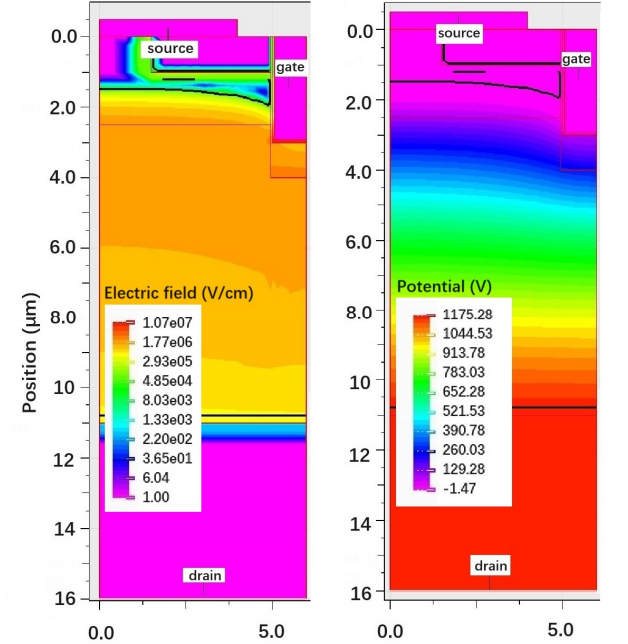

目前,车规级SiC MOSFET有两种电压等级:650V和1200V。其中,1200V SiC MOSFET的比导通电阻范围约为3-4 mΩ·cm²,其中沟道电阻对导通电阻的贡献很大,约为0.5mΩ·cm²,这增加了总传导损耗。沟槽栅SiCMOSFET在降低沟道电阻方面比较有优势,透过沟槽刻蚀,它利用 (11–20) 或 (1–100) 晶面,与 (0001) 和 (000–1) 晶面相比,这两个晶面的沟道迁移率高出2-3倍。不过,与平面栅SiC MOSFET 相比,沟槽栅SiC MOSFET的工艺更复杂,需要沟槽蚀刻和高能离子注入等,这增加了制造成本。而且,沟槽栅SiC MOSFET的沟槽底部栅极氧化层的可靠性也需要改进。为了进一步改善沟槽栅SiCMOSFET的比导通电阻,大大节省制造成本,近日深圳平湖实验室团队发表了一篇题为《SiC沟槽MOSFET的新结构及工艺方法》的文献(获取文献请加微信:hangjiashuo999),介绍了一种新型沟槽栅SiC MOSFET 器件,该器件主要有几个特点:一是加入了 p 底部区域来保护沟槽结构底部的栅极氧化层,器件的沟道位于沟槽侧壁的两侧。二是通过利用控制氯化氢 (HCl) 气体流速的沟槽再填充工艺,使得器件制造工艺无需使用离子注入。根据TCAD模拟结果,该器件的p连接层的横向厚度保持在 400Å 以下。所开发的沟槽SiC MOSFET展示了阻断1174V反向偏置电压的能力,而且n型漂移层在p底部区域下方的最小厚度为 7μm。技术开发背景:

沟槽SiC MOSFET需要解决3个问题

传统的沟槽SiC MOSFET主要存在几个难题需要解决:一是用于保护栅氧化层底部的深p阱占据了器件有源区的很大一部分,这增加了比导通电阻。二是分布在栅极结构两侧的深p阱对栅氧化层的保护不足,导致沟槽栅器件底部栅氧化层拐角处的电场强度仍然相对较高,这可能导致栅氧化层TDDB失效,损害器件的长期可靠性。三是使用离子注入会造成损伤和陷阱,从而降低反向传导期间少数载流子的注入效率。

为了解决上述问题,平湖实验室参考了SiC超结器件结构的新制备方法。此前,日本AIST团队在2019年提出了4H-SiC沟槽回填工艺,并成功制备了6500 k 4H-SiC超结 (SJ) MOSFET。这种工艺是将p型外延层回填到n型沟槽中,从而可以在n型沟槽的侧壁上形成非常薄的外延层(<0.1μm)。平湖实验室团队多次外延生长实现沟槽SiC MOSFET结构,如下图所示,从下到上依次为n+衬底、n-buffer层、n-epi(漂移)层、p-well层、n+source层。该器件采用干法刻蚀在晶圆表面刻蚀出深沟槽(图1(b)),然后用p型SiC外延层重新填充沟槽内部(图1(c))。然后,再采用 LPCVD 方法在沟槽内沉积栅氧化层,沉积了 50~100nm 厚的栅氧化层。紧接着采用LPCVD方法沉积多晶硅层,并用回蚀工艺确保多晶硅层仅在沟槽区域内(图1(d))。下一步工艺是在器件表面沉积一层 IMD 氧化层(二氧化硅),作为栅极和源极之间的钝化隔离,IMD 层下面的多晶硅与多晶硅条相连,并最终与栅极焊盘相连以实现外部连接(图1(e))。最后采用干法刻蚀的方法去除 IMD 层、栅氧化层和 SiC 外延层,然后沉积表面金属层并进行欧姆退火,随后在衬底背面进行CMP减薄、背面金属化和激光退火,形成器件的漏极欧姆接触,器件最终的单元结构如图1(f)所示。可以看出平湖实验室的工艺流程相当简单,不需要离子注入即可实现沟槽SiC MOSFET,一方面通过可控氯化氢 (HCl) 气体流速的沟槽再填充工艺,可以实现较薄的 p 连接层厚度,另一方面,借助 p 连接层和通过寄生PMOS导通钳位的 p 底部区域,有效地保护了栅极氧化物的角落。TCAD模拟结果显示,该SiC沟槽 MOSFET可以阻挡1174V反向偏置,p底部区域下方的n 漂移层的最小厚度为7μm。本文发自【行家说三代半】,专注第三代半导体(碳化硅和氮化镓)行业观察。

插播:英诺赛科、能华半导体、致能科技、京东方华灿光电、镓奥科技等已确认参编《2024-2025氮化镓(GaN)产业调研白皮书》,演讲或摊位咨询请联系许若冰(hangjiashuo999)。

插播:英诺赛科、能华半导体、致能科技、京东方华灿光电、镓奥科技等已确认参编《2024-2025氮化镓(GaN)产业调研白皮书》,演讲或摊位咨询请联系许若冰(hangjiashuo999)。