今天给大侠带来的是一周掌握FPGA Verilog HDL 语法,今天开启第七天,也就是最后一天。

最后两天推出思考题(附参考答案),大侠可以自行思考,检测一下自己这一周的语法学习效果,结合实例理解理论语法,会让你理解运用的更加透彻。下面咱们废话就不多说了,一起来看看吧。

reg [3:0] A;reg V ,W;integer K;....A=4'b1010;for(K=2;K>=0;K=K-1)beginV=V^A[k];W=A[K]^A[K+1];end

always @( )if(!Nreset)Q<=0;else if(!Nset)Q<=1;elseQ<=D;

always @(posedge Clock)beginA<=B;if(C)A<=1'b0;end

always @( A or B)case(A)1'b0: F=B;1'b1: G=B;endcase

always @( posedge A or posedge B )if(A)C<=1'b0;elseC<=D;

always @(posedge Clk or negedge Rst)if(Rst)A<=1'b0;elseA<=B;

always @(posedge Clk)begin: Blkreg B, C;C = B;D <= C;B = A;end

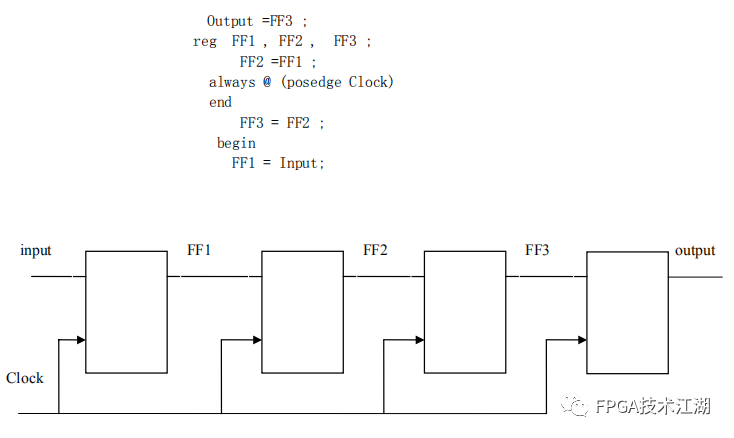

reg FF1,FF2,FF3;always @(posedge Clock)beginOutput= FF3;FF3 = FF2;FF2 = FF1;FF1 = Input;end

integerI;reg[3:0]A;reg[7:0]B;initialbeginI=-1;A=I;B=A;$display("%b",B);( )A=A/2;$display("%b",A);( )B=A+14$diaplay("%d",B);( )A=A+14;$display("%d",A);( )A=-2;I=A/2;$display("%d",I);( )end

I=-1;A=I;B=A;$display("%b",B);(00001111)A=A/2;$display("%b",A);(0111)B=A+14$diaplay("%d",B);(21)A=A+14;$display("%d",A);(5)(A为4位,所以21被截为5)A=-2;I=A/2;$display("%d",I);(7)(A=-2,则是1110)

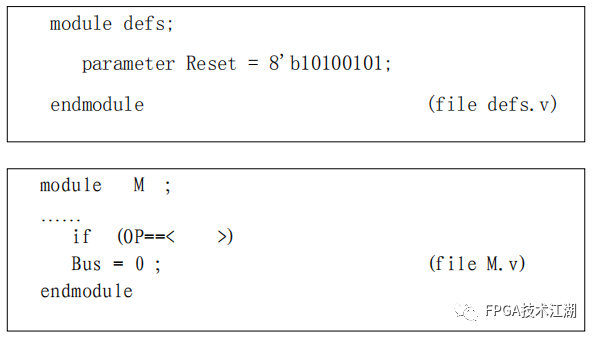

module M'include "defs.v"....if(OP==) Bus=0;endmodule

parameter Reset=8'b10100101; (File defs.v)module M'include "defs.v"....if(OP==Bus=0;endmodule

Module Pipe(IP,OP)parameter Option=1;parameter Depth=1;...endmodulePipe( ) P1(IP1,OP1);

参考答案:#(1,8) (其中1对应参数Option,8对应参数Depth.)

26)若想使P1中的Depth的值变为16,则应向空括号中填入哪个选项。

module Pipe (IP ,OP);parameter Option =1;parameter Depth = 1;…………endmodule

modulePipe P1(IP1 ,OP1);( );endmodule

1.defparam P1.Depth=16;

2.parameter P1.Depth=16;

3.parameter Pipe.Depth=16;

4.defparam Pipe.Depth=16;

参考答案:1

(用后缀改变引用模块的参数要用defparam及用本模块名作为引用参数的前缀,如p1.Depth。)

27)如果我们想在Test的monitor语句中观察Count的值,则在空括号中应填入什么?

Module TestTop T();initial$monitor( )endmodule

module Top;Block B1();Block B2();endmodule

module Block;Counter C();endmodule

module Counter;reg [3:0] Count;....endmodule

答案:T.B1.C.Countor Test.T.B1.C.Count

28) 下题中用initial块给reg[7:0]V符值,请指明每种情况下V的8位都是什值。这道题说明在数的表示时,已标明字宽的数若用XZ表示某些位,只有在最左边的X或Z具有扩展性。

Reg [ 7 :0 ] VinitialbeginV = 8’b0;V = 8’b1;V = 8’bX;V = 8’BZX;V = 8’BXXZZ;V = 8’b1X;end

参考答案:

8’b00000000

8’b00000001

8’bXXXXXXXX

8’bZZZZZZZX

8’BXXXXXXZZ

8’b0000001X

最后一天 Day 7 到这里就结束了,也代表这一周学Verilog HDL 语法到这里就结束了,熟练透彻的使用语法也是做研发设计进阶的不可缺的部分,大侠可以自行思考练习,愿修炼的炉火纯青,大侠保重,告辞。

END

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+学校/公司+专业/岗位进群

FPGA技术江湖QQ交流群

备注姓名+学校/公司+专业/岗位进群