(本文编译自Semiconductor Engineering)

3D-IC和小芯片的概念让整个行业都为之兴奋。这可能标志着IP行业发展的下一个阶段,但到目前为止,技术难题和成本问题限制了它的应用范围,只有少数几家公司在使用。即使在这些公司中,他们似乎也没有从异构集成或复用中获得明显的益处。

尝试实现这一目标并不是什么新鲜事。“十年前,我们就试图创建一种用于构建小芯片的架构,”Marvell技术副总裁兼定制解决方案首席技术官Mark Kuemerle表示,“我们的目标是能够定义一种架构,让人们可以将多个小芯片组合在一起,以实现特定功能。神奇的是,通过将这些较小的芯片组合起来,我们可以使用耗电低得多的接口。我们可以将过去庞大、耗电、复杂且昂贵的系统,改造成一个基于小芯片的系统,从而提高整体效率。更重要的是,这将节省大量的开发成本,并大幅降低芯片的总体成本。但结果并非如此。最终的情况是,只有屈指可数的公司有能力开发小芯片。”

那么,为什么要这么做呢?其中一个主要的驱动因素是,有越来越多的内容虽然至关重要,但并不能体现差异化。西门子EDA中央工程解决方案总监Pratyush Kamal表示:“大众市场距离采用3D-IC还需要几年时间,但有些应用则非常适合它。市场上正在涌现出很多模块化的趋势。人们开始关注新的架构,相应的,他们也在思考如何让这项技术走向大众市场。”

过去,推动新技术发展的公司会投入必要的研发资金,然后这些技术会逐渐普及到大众市场。Ansys产品营销总监Marc Swinnen表示:“行业领导者会率先采用这项先进的新技术,人们普遍认为整个行业会纷纷效仿。但两者之间的差距正在越来越大。领跑者已经超越了同行,并领先于主流水平。这令人担忧,因为人们仍然普遍认为,随着系统规模越来越大,特别是如果小芯片市场开始腾飞,3D-IC或2.5D将成为标准配置。但随着这些差距的扩大,就有可能出现竞争替代的情况。”

简而言之,那些为了保持竞争力而必须采用小芯片技术的公司,与那些希望采用小芯片技术的公司之间存在着更大的差距。“小芯片使我们能够做更多前沿的工作,并使我们能够在一个封装上集成更多芯片,这有助于提升我们的性能,”Marvell的Kuemerle表示。

然而,这并不是追求3D-IC的唯一原因。“3D-IC技术具有许多优势,包括性能提升、功耗降低以及小型化,”Rapidus设计解决方案现场首席技术官Rozalia Beica表示,“其应用范围涵盖从移动设备到人工智能、超级计算机和数据中心等高端领域。该技术能够实现紧凑设计并提升性能。”

尽管如此,仍然存在重大挑战。“大多数使用3D-IC的公司都是垂直整合型的,”Ansys的Swinnen表示,“他们是规模较大的公司,有足够的资金和能力来设计芯片、设计中介层、对整个系统进行模拟、考虑封装问题,并且要在众多必须做出的架构选择中进行考量。”

大芯片还是小PCB?

3D-IC不仅仅是缩小PCB上的所有东西。“为了获得不同的益处,人们往往会改变比较的基准,”Swinnen表示,“这其实不太公平。PCB走向更小的系统,那就是SoC。如果你想要比PCB有更好的性能,那你就会选择SoC。这是自然的演变。这也是我们40年来一直在做的事情。将其分解为多个小芯片,并不是因为你试图把PCB做得更紧凑。而是因为要把原本的单芯片结构进行分解。比较的基准应该是单芯片,而不是PCB。”

但也并非总是如此。像高带宽存储(HBM)这样早期成功的案例,会将更多的外部组件集成到一个封装中。“随着在封装中引入更多功能的需求不断增加,使用单片SoC类型结构来实现这一点变得越来越困难,”Rapidus的Beica表示,“并非所有功能都需要最先进的设计。虽然先进设计优先考虑最高性能目标和最小外形尺寸,但当异构性很重要,并且系统内需要更多功能时,这种方法可能并不是最有效的方法。”

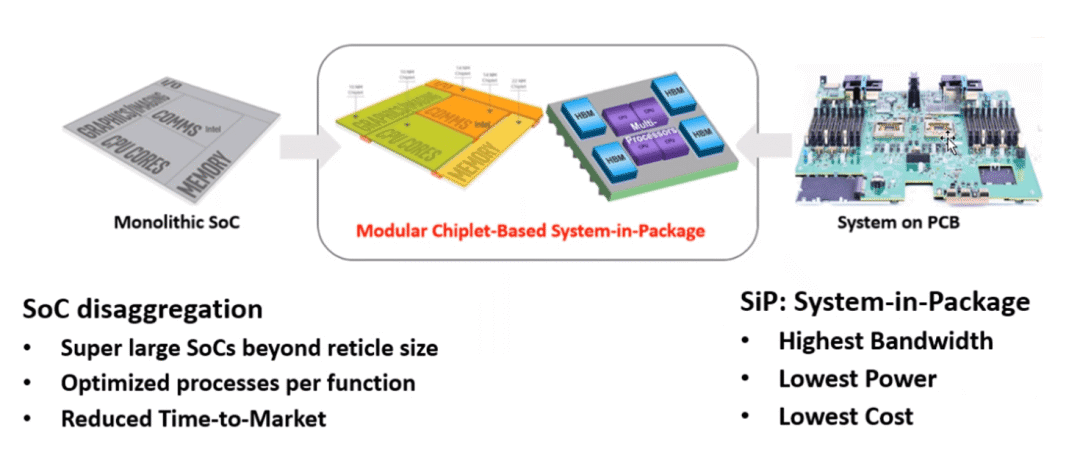

此外,如果小芯片随时可用,则3D-IC可被视为封装内的PCB。“PCB实际上限制了芯片之间相互通信的带宽量,”Eliyan首席执行官兼联合创始人Ramin Farjadrad表示,“过去20年,PCB的带宽提升幅度不到两个数量级,而芯片的带宽提升幅度达到了五个数量级。这是造成内存和I/O瓶颈的主要原因。通过将相当于一块PCB的东西移到封装内部(见图1),我们称之为凸点或微凸点的焊球密度会显著提高。芯片之间的距离也会显著缩短。这些芯片裸片之间就能以更低的功率获得更高的带宽。”

图1:小芯片是半导体的未来。

图源:Eliyan

单片芯片工艺的持续发展受到良率的制约。Cadence SSG产品营销总监Mayank Bhatnagar 表示:“人们正面临光罩极限的问题。如果你想制造一块大型的硅芯片,那么在远未达到光罩极限之前,就会开始出现良率问题。如果无法实现盈利性生产,那么制造它实际上就毫无意义。而这正是非常大的单片芯片的发展困境。它们变得太大了。良率下降,而且降幅大到使其变得不经济。”

并非所有的芯片都需要使用最先进的工艺节点。西门子的Kamal表示:“AI要求芯片上有更多的SRAM,而SRAM的规模并没有响应缩小。从理论上讲,5nm工艺下的SRAM位单元是最小的,之后其尺寸就开始增大。但如果你看一下每个存储单元的成本,就会发现早在5纳米工艺之前,成本的缩减就已经停止了。尽管我们从7纳米工艺发展到了5纳米工艺,存储单元的每位成本却变得更高了。现在有两件事同时发生。一是需要更多的SRAM,另一方面SRAM更贵了。3D技术由于其芯片间的紧密连接,几乎可以实现两个芯片之间的零延迟接口,这使得我们可以尝试不同的层级结构和缓存结构。”

理想情况下,每个组件都会采用最佳的技术。“我们可以用尖端技术制造巨大的芯片,而小芯片则成为了帮助我们实现这一点的手段,”Kuemerle表示,“我们将芯片分割成更多的部分,这样就能突破限制,获得比在一次集成流片中更多的硅芯片面积。我们可以将I/O技术与核心芯片技术相结合,这样就能突破极限,使用最好的可用技术,而这些技术往往也是最昂贵的。”

技术和开发成本的结合正推动更多公司朝这个方向发展。Cadence的Bhatnagar表示:“随着最新工艺节点的发展,每个晶体管的成本正在上升。将设计的每个部分都转移到新工艺节点是没有意义的,因为大多数设计可能不会从中受益。如果你有一个射频收发器或模拟模块,它并不会因为每个晶体管成本的降低而受益。另一方面,你还必须为新的工艺节点重新设计它。当你进行芯片拆分时,就只能转移那些能从新工艺节点中受益的部分。”

这听起来很诱人,但在新设计中重复使用以前设计好的小芯片却充满了风险。

成本效益

数据中心似乎对价格不太敏感。“AI非常看重高性能、非常复杂且规模庞大的硅芯片系统,以至于对他们来说,投入巨额资金来追逐这个市场是值得的,”Swinnen表示,“他们有理由需要这些巨大的3D芯片。”

其余行业仍在观望。Kamal表示:“当我与我们的移动客户交谈时,我感觉他们还没有为3D-IC做好准备,因为从经济角度来看,这对他们来说还不合理。但与此同时,他们也明白自己正面临芯片尺寸微缩的极限。从5nm到3nm再到2nm,他们获得的性能提升微乎其微,而且这种微小的提升是以高昂的成本为代价的。他们采用这些节点的唯一原因是为了从晶体管中获得最大性能,尤其是在GAA这种新晶体管架构的推动下。但GAA是一个非常复杂的工艺,良率很低。”

问题有两个方面。首先,他们需要采用全新的设计和封装方法。其次,他们需要从单次流片转向多次流片。Blue Cheetah首席执行官Elad Alon表示:“对于一家公司来说,采用小芯片设计风格可能是有意义的。这意味着他们需要多套掩模版,可能需要多次流片,与在先进工艺节点上制造更大的单片芯片相比,初始的非经常性工程费用(NRE)高得让人难以接受。如果坚持使用单片芯片解决方案,那么推出产品所需的NRE可能会更低。”

目前仍有几项技术挑战需要解决。“当我想到3D技术时,我首先会想到混合键合技术,因为这是真正物有所值的技术,”Kuemerle表示。“它有助于解决一些散热方面的挑战,提供非常高的连接性和非常低的功耗。这涉及将硅片减薄到极小的厚度,并以非常细的间距集成铜对铜键合。”

HBM仍在努力实现这一目标。“3D内存目前仍然只使用微凸点将内存连接到主芯片,”他表示,“内存供应商正在研究混合键合方法,我们都希望这种方法能在不久的将来投入生产。”

去除PHY可能会大幅提升性能。Kamal表示:“当采用几乎无PHY的架构时,我们所说的是一种非常精细的3D互连结构,互连尺寸非常小,而这只能通过晶圆级堆叠才能实现。如果采用晶圆级堆叠,互连间距会更长,这就是我划定的界限。那样的话,就需要特殊的缓冲器,而且想要实现无PHY架构可能有些勉强。这是任何3D堆叠都面临的挑战——至少有一个芯片的背面有金属层。一旦将两个芯片融合在一起,仍然需要将I/O信号引出,电源通过基板引出。”

功率密度和散热方面的挑战正成为众所周知的问题,但还有其他问题需要考虑。“假设你有前端制程,即晶体管层,以及具有背面金属层的芯片,以便将I/O信号引出芯片,”Kamal解释道,“现在晶体管堆栈的两侧都有金属。这样一来,计量工作就变得极具挑战性。如果需要对某些东西进行检测,你会想使用X射线成像技术或某种视觉扫描技术,但这会非常困难。此外,聚焦离子束技术使用硅片的背面进入芯片内部并进行修改。当我们试图调试某些东西并为芯片故障建立假设时,我们称之为对IC进行聚焦离子束(FIB)处理。你进行一些聚焦离子束处理操作,然后根据这些实验对芯片进行重新设计,接着重新制作掩膜版并重新制作设计。现在,你失去了从背面进行聚焦离子束处理的能力。如果你设计了一个芯片,但它在实际应用中无法正常工作,那么在调试芯片方面就存在很大的困难。”

异构堆叠增加了复杂性。“异构集成需要将不同的技术,包括新旧技术结合起来,”Fraunhofer IIS自适应系统工程部高效电子负责人Andy Heinig表示,“一个显著的区别在于旧技术节点的信号电平。新节点需要低得多的信号电平,而旧节点需要更高的信号电平。在这方面实现兼容性是一个挑战。通常情况下,只需要轻量级的芯片间接口,因为在较旧的技术中,数字IP的集成在空间方面受到很大限制。”

重复使用又增加了更多复杂性。“对于3D技术而言,最大的限制是希望两个芯片的尺寸相匹配,”Kamal表示,“否则,就会浪费芯片面积。你可以进行晶圆上芯片的集成,其中一个芯片的尺寸与另一个芯片不完全相同,但这样在晶圆级封装或集成过程中,可处理的芯片数量就会减少。这存在一个生产效率的挑战。但作为架构师,一个优势是不必追求同构,异构也是可行的。一个芯片可以采用5纳米工艺,另一个采用3纳米工艺。

结论

3D-IC有可能改变IP和半导体行业,但它仍然是一个非常昂贵的选择,目前仅适用于数据中心,而且即便在数据中心得以应用也只是因为人工智能AI的需求。还有许多挑战尚未克服,而且看来3D-IC的概念对于大众来说仍然是未来的事情。

在3D-IC能够超越IDM公司的应用范畴之前,还需要在接口、标准、工具和方法等方面做大量工作。

END