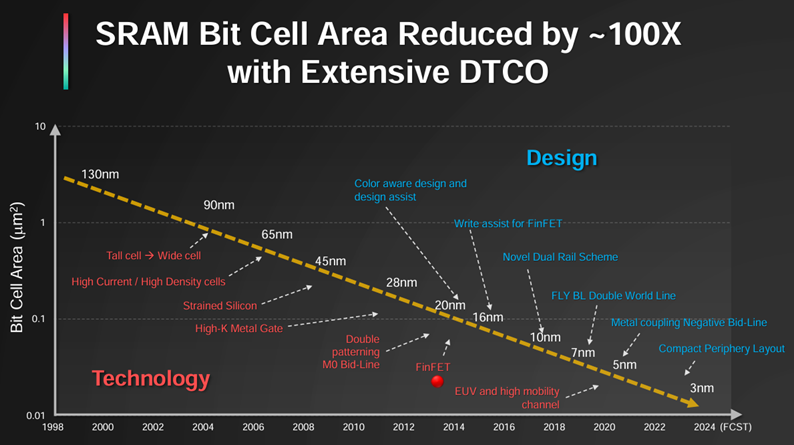

AMD首席技术官Mark Papermaster在DAC2022做的主旨报告《Advancing EDA Through the Power of AI and High performance Computing》中指出,随着工艺技术的发展,DTCO对于芯片集成度和能效带来的极限重要性越来越高了,他认为在3纳米的时候,晶体管尺寸微缩本身带来的收益已经不到50%,其他的都要靠DTCO。(注:在DAC2000会议上,台积电首席科学家、斯坦福大学教授黄汉森(Philip Wong)就指出,为密度提高做出主要贡献的是DTCO技术,并强调这种晶体管数量趋势将持续相当长的一段时间。有些来自持续扩展,有些来自集成,有些来自DTCO。)

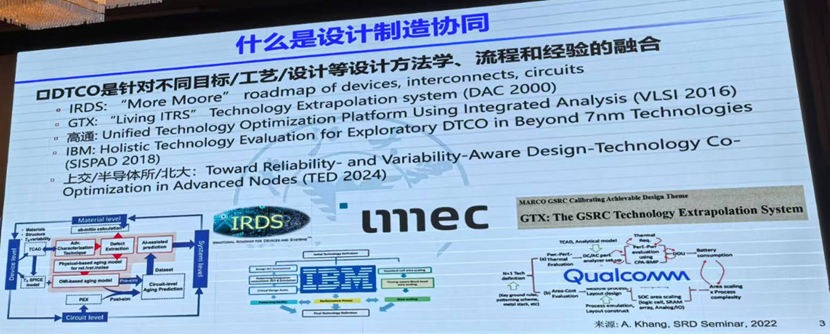

那么DTCO到底是什么。DTCO是Design Technology Co-Optimization的缩写,中文翻译是:设计与制程协同优化。实际上DTCO是针对不同目标、工艺、设计等设计方法学、流程和经验的融合,强调了设计、制造和材料等多个领域之间的合作和协调。行业普遍认为,DTCO是一种支持快速高效技术探索、设计PPA评估和设计收敛的方法。通过DTCO方法,设计团队和制造团队能够在设计阶段就考虑到制造的限制和要求,从而提前解决潜在的制造问题,并确保设计在实际制造中的可行性和可靠性。

事实上,从上图可以看出,没有一个公司或一个科研机构给出一个有关DTCO明晰的概念。

DTCO的历史由来已久,不是一个新鲜的名词。早期的模拟芯片大厂会根据电路的需求去调整半导体器件和工艺的设计,评估新一代工艺中的各种选项,从而决定最佳方案,以强化自身的竞争力。但是在摩尔定律的黄金时代,DTCO流程能调整的参数并不多。此外,从Fabless的角度来看,因为每过一年多都会有新一代的半导体工艺出现导致性能大幅提升,花大量时间和资源去帮助本代工艺做DTCO优化的收益并不大。另外,晶圆代工模式的一个重要假设就是平台化标准化的工艺设计,因此Foundry更倾向于去提供一两套标准的工艺(例如低功耗,高性能等等),而并没有很强的根据客户设计公司的反馈去定制化工艺的意愿。总体来说,在摩尔定律的黄金时代,DTCO更多的是评估和验证作用。

然而,随着摩尔定律的延续越来越有挑战性,开发和使用新一代半导体工艺的成本都越来越高,同时新一代半导体工艺带来的性能提升却越来越小,今天我们看到借助DTCO来尽可能多地优化半导体工艺以及电路设计正在变得越来越热门,并且系统级别的DTCO(system-technology co-optimization,STCO),材料级DTCO(Materials to Systems Co-Optimization,MSCO)的概念正在兴起。

台积电副总裁张晓强在ISSCC2024主旨报告PPT截图

从台积电副总裁张晓强在ISSCC2024主旨报告PPT截图中可以看出,DTCO在不同工艺节点中可以有不同的方法。

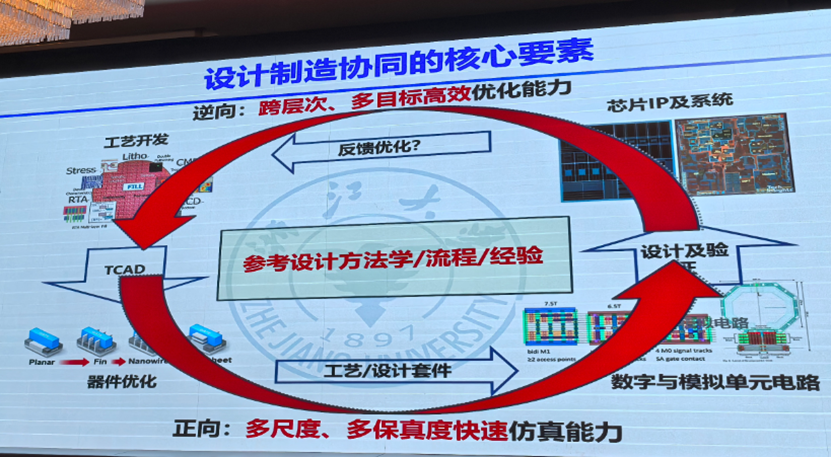

所以要从涉及到协同的一个本质上去理解DTCO。先来看DTCO的三大核心要素:多尺度、多保真度的快速仿真能力,跨层次、多目标的高效优化能力,参考设计方法学/流程/经验。

但事实上,要让设计与制造协同起来,找到最优方案,是一个非常复杂的过程。这就回到了文章的主题,AI for DTCO。

目前的SoC芯片中晶体管数量非常庞大,基本上做芯片前端后端设计的话可能要9个月到18个月;另外一方面工艺研发很可能要2年到4年。比如说一个先进工艺制程,再加上封装测试,可能需要1~4年的时间。苹果采用5纳米工艺制程的A14芯片的研发成本高达5亿美元,一次性流片成本约5000万美元,可以说研发成本远超物料成本。

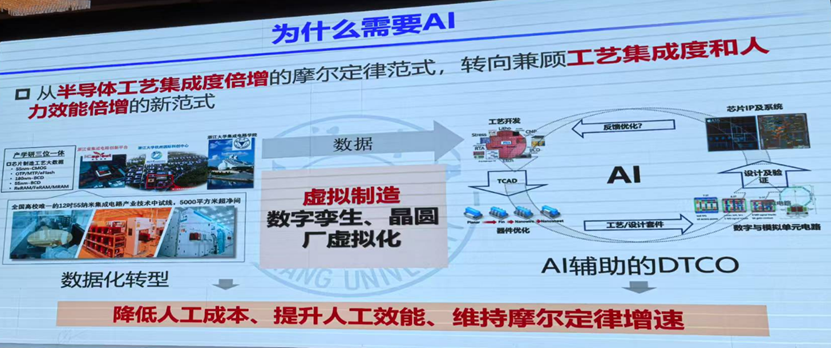

后摩尔时代,如何去降本增效,那就是要兼顾工艺制程的先进性和人力效能的倍增。中国工程院院士、浙江大学集成电路学院院长吴汉明提出了虚拟制造概念,把整个晶圆厂给虚拟化,通过数字孪生去做硬件。吴汉明院士认为,在流片需要降本增效的当下,数字化技术、人工智能是未来集成电路发展的新思路。中国在AI Accelerators领域与世界先进水平没有太大差距,可能会成为未来发展的抓手。通过智能制造的工艺优化技术和更智能的决策支持,可以缩短研发周期,提升制程良率,实现降本增效。

值得强调的是,虚拟制造的有效实现需要以垂直模型整合为基础,而这一整合依赖于公共大数据平台与深厚的专业知识体系。只有在强大数据支撑和领域知识沉淀的基础上,才能构建高精度、高可靠性的虚拟制造系统。同时,随着市场对“小批量、多品种、定制化”生产模式需求的日益增长,集成电路制造亟需从传统的大规模标准化转向灵活应变的数字化智能模式。这一转变不仅呼应了产业技术发展的新趋势,也为虚拟制造技术的落地提供了广阔空间。在此基础上,AI与DTCO技术的融合,将为虚拟制造体系的完善与普及带来巨大推动力,助力集成电路产业在后摩尔时代实现可持续、高质量发展。

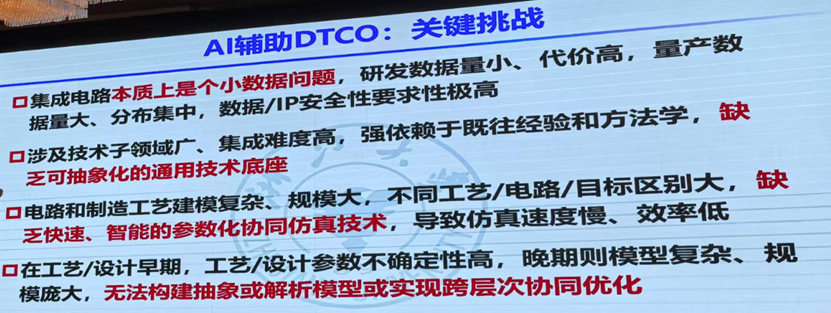

卓成教授在报告中指出AI for DCTO的4大关键挑战的同时,也介绍了浙江大学集成电路智能设计与先进制造自动化(IDEA)实验室为此做的一些工作。

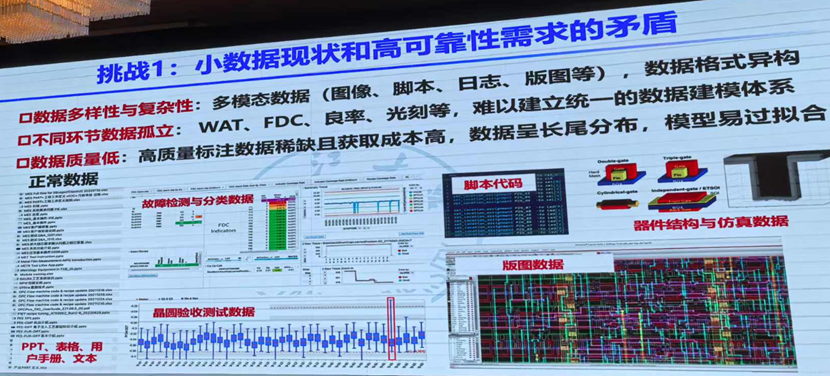

一是数据的问题。数据是AI的源动力。集成电路领域的数据是个很有趣的现象。研究时数据量小,采集数据的代价成本很高;成熟的量产线要保持稳定,数据/IP安全性要求性极高,尽管数据量大但是分布集中,所以说我们要处理的始终是一个小数据问题。如何解决小数据现状和高可靠性需求的矛盾成为关键。

卓成老师指出,集成电路小数据现状包括:数据多样性与复杂性,多模态数据(图像、脚本日志、版图等),数据格式异构;不同环节数据孤立,WAT、FDC、良率、光刻等,难以建立统一的数据建模体系;数据质量低,高质量标注数据稀缺或错误,且获取成本高,数据呈长尾分布,模型易过拟合正常数据。

实验室为此提出了一种用于纳米级晶圆表面缺陷检测的少样本学习方法——SEM-CLIP。相较于现有工作,SEM-CLIP在缺陷分类和分割上实现了显著的性能提升,为少样本工业应用场景提供了有效解决方案。并在ICCAD2024发文《SEM-CLIP: Precise Few-Shot Learning for Nanoscale Defect Detection in Scanning Electron Microscope Image》。

在集成电路制造产线上,晶圆表面缺陷的检测与分类对产线良率的提升至关重要,现有方法通常受限于经验不足、数据不足、标注成本过高等问题以及复杂的缺陷纹理和背景干扰。SEM-CLIP通过定制化的CLIP架构结合专家知识的文本提示,仅使用少量样本进行微调实现了少样本学习功能。该方法利用领域专家知识,结合目标缺陷区域的先验信息设计文本提示;同时引入V-V自注意力机制,从多个层级进行特征提取,以达到对缺陷区域更好的关注效果并减少背景信息的干扰。实验基于浙大集成电路公共创新中心成套工艺研发平台的产线数据,结果表明SEM-CLIP在各种少样本条件设置下均展示出了卓越的性能,在只使用10张样本的情况下,分别在iAUROC, pAUROC, F1-max分数上相比于目前最先进的方法提升了2.0%、1.3%、21.1%,并能精准分割出缺陷与复杂背景间的模糊边界。

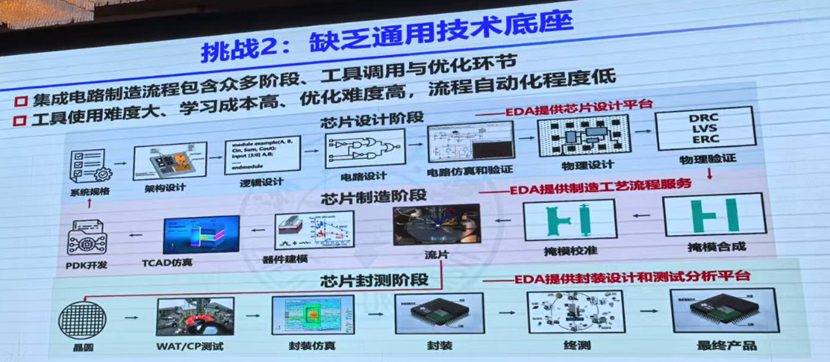

二、集成电路涉及的技术子领域广(如高可靠性、低功耗或BCD)、集成难度高,强依赖于既往经验和方法学,缺乏可抽象化的通用技术底座,很难传承。集成电路整个流程非常长,设计、制造、封装各个环节有非常大量的工具,然后每个工具又有大量的参数,很多时候仿真不准不是因为工具不行,而是因为设置运行条件不对。

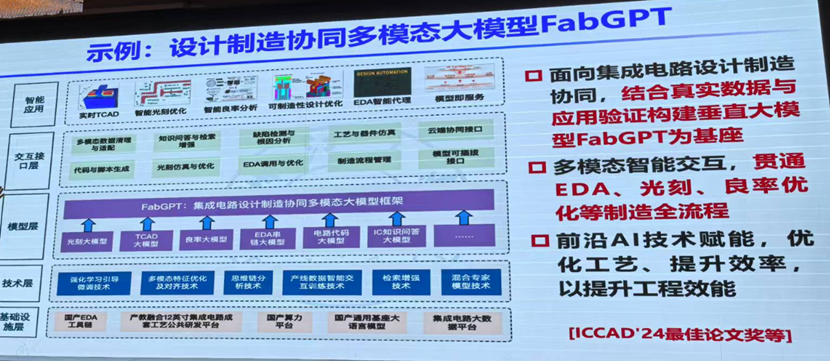

实验室为此提出了一种用于检测、定位、分割和查询晶圆缺陷知识的多模态大模型- FabGPT,不仅可以有效地检测复杂晶圆背景中的微小缺陷,并且能够对相关的缺陷知识进行问答分析,并在ICCAD2024发表《FabGPT: An Efficient Large Multimodal Model for Complex Wafer Defect Knowledge Queries》、《An Agile Framework for Efficient LLM Accelerator Development and Model Inference》等多篇论文,获得前端最佳论文奖,这是中国内地高校首次以第一单位身份获该奖项。

大模型极大地推动了人工智能的革命性发展和集成电路制造向智能化的转型。然而,目前的(多模态)大模型对专业领域的知识缺乏敏感性和判断力,这不仅限制了模型对晶圆缺陷区域查询的效率,还导致了模型存在严重的“模态偏差”问题,即模型无法理解图文内容之间的联系从而产生错误的响应。

为了能够对晶圆缺陷区域进行精准的检测、定位、分割并准确解答晶圆缺陷的相关知识,FabGPT模型采用了三阶段策略:模态增强、检测和问答阶段,来逐步将高质量的提示指令嵌入到预训练模型中,使其能够在复杂的晶圆背景下自动识别微小缺陷。此外,所提出的交互式语料库训练策略监督了晶圆缺陷知识与固有知识的更新和交互,有效地平衡了知识的问答查询、缓解了“模态偏差”问题。

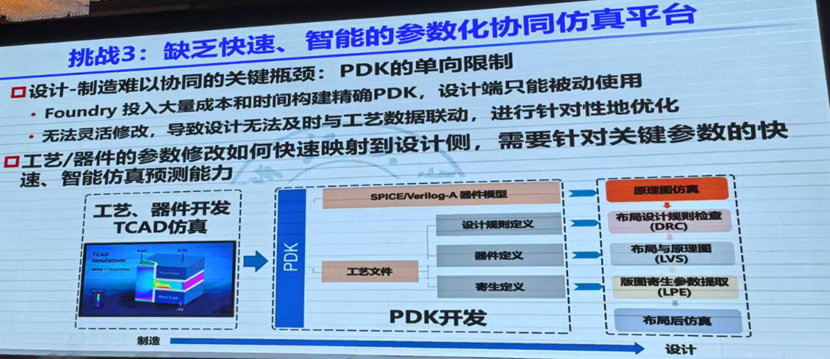

三、电路和制造工艺建模复杂、规模大,不同工艺/电路/目标区别大,缺乏快速、智能的参数化协同仿真技术,导致仿真速度慢、效率低。

仿真速度慢,但是在DTCO时是否需要精准的仿真呢?卓教授指出,我们只需要知道关键参数通过PDK对PPA的影响,然后去优化这些关键参数。

基于此,实验室提出了工艺感知参数化仿真平台,深度结合工艺模拟、版图生成、器件结构与寄生提取,快速评估关键工艺/设计参数变化对寄生、功耗、性能、可靠性的影响,打通工艺步骤、器件生成、寄生提取等关键环节,构建可重用与可扩展的仿真框架,支持多维度工艺与设计参数的调优,快速迭代、协同优化,使仿真性能飞跃。相关工作论文发表于DAC2024,进一步的工作也入选了DAC2025。

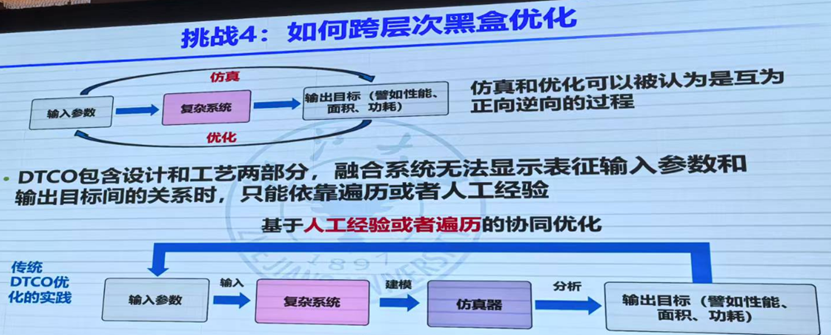

四、在工艺/设计早期,工艺/设计参数不确定性高,晚期则模型复杂、规模庞大,无法构建抽象或解析模型或实现跨层次协同优化。

所以要确定选择一些相对于下一阶段比较敏感的布局参数,同时忽略其他参数,从而让仿真效率大大飞跃。

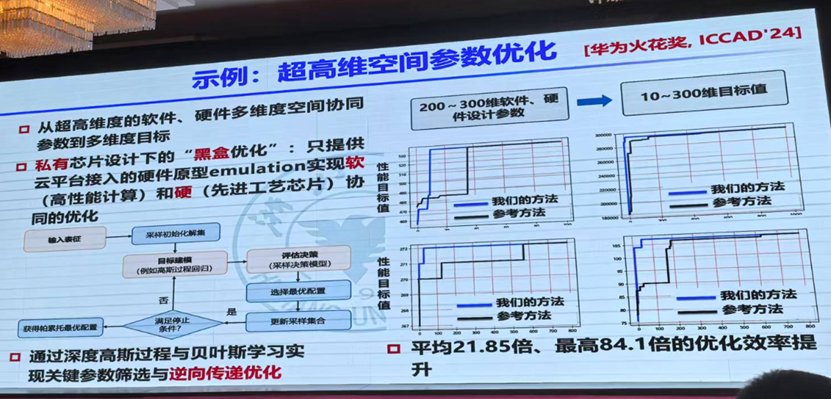

人工智能的迅速发展,对神经网络计算加速的定制硬件架构提出了非常大的需求。尽管许多工具简化了微架构设计并将其转变为设置参数的过程,但从指数级广阔的设计空间中识别最佳参数组合仍然是一项重大挑战。尤其是对于具有高维参数的硬件设计,设计空间愈加复杂,现有的方法难以对其进行有效探索。

基于此,实验室提出了一种基于蒙特卡洛树搜索的微架构设计空间探索框架-MCT-Explorer,相关工作发表于ICCAD2024 《Is Vanilla Bayesian Optimization Enough for High-Dimensional Architecture Design Optimization?》。

相较于现有方法,MCT-Explorer系统能够有效解决高维参数设计空间的探索困境,并能在有限优化次数内提供具有可解释性的高质量结果。MCT-Explorer框架利用了蒙特卡洛树搜索的特性,动态地从所有可配置参数中选取出相对重要的参数来进行贝叶斯优化,缓解了高维贝叶斯优化中的拟合不准确问题。通过计算每个参数在历次贝叶斯优化中得到的新的参数组合的PPA的超体积的平均贡献,MCT-Explorer对每个参数的重要性进行评估。此外,MCT-Explorer引入了联合熵搜索作为贝叶斯优化中的获取函数,利用其信息引导的特性对未知的设计空间进行更广泛地探索。相比于现有方法,MCT-Explorer能够有效探索超过60个可调参数,O(10^30)的高维微架构设计空间,得到的结果在ADRS指标上能达到31%的提升,并且仅花费33%的时间开销。

总结

对于集成电路产业发展,设计制造协同是必须手段,尤其在工艺受限的情况下,我们更要依靠协同去挖掘其中可能的一个能量。

AI深度融合的话,是可以帮助集成电路产业就是迈向兼顾工艺集成度和人力效能倍增的一个新范式,因为人力效能倍增是实现电子产业的一个很大的支撑。

但是不能单纯去套用大模型或深度学习,因为会带来训练成本高企和泛化性的问题。

传统机器学习依然有很好的应用性,尤其是适合深度嵌入现有的一些EDA工具

生成式AI具有强思维能力和强不确定性,但有助于可以打通节点,去构建一个通用的基座。

关于浙江大学集成电路智能设计与先进制造自动化(IDEA)实验室

实验室专注于集成电路设计、电子设计自动化技术及其在先进制造领域的应用与创新。在ICCAD、DAC、IEDM、ASPDAC、DATE等会议发表论文多篇;先后获得ICCAD2024前端最佳论文奖(中国内地高校首次以第一单位身份获该奖项)和ASPDAC2024前端最佳论文奖等多个奖项。

关于浙大集成电路公共创新中心成套工艺研发平台

CMOS集成电路成套工艺与设计技术创新中心成立于2022年,在中国工程院吴汉明院士、国家集成电路专家组成员严晓浪教授的带领下,聚焦具有紧迫战略需求的集成电路领域和有望引领未来发展的战略制高点,以全国唯一12英寸CMOS成套工艺产教融合公共平台为载体,围绕成套工艺基础技术、BCD技术、混合信号芯片技术、12英寸生产线良率提升以及先进芯片设计等5大方向,重点攻关高性能CMOS工艺、MCU设计与制造、电源管理芯片设计与制造、12英寸生产线CIM整体解决方案和良率提升等关键核心技术;为集成电路企业提供按需定制的技术创新服务和整体解决方案,打造“技术供给+验证服务+中试流片”的技术创新公共服务体系;围绕打造集成电路高层次人才发展重要首选地,优化人才引培环境,加快汇聚国际顶尖人才、青年科技人才以及高端产业创新人才,全面建设具有全球影响力的高端人才蓄水池。