AMD Vivado™ Design Suite 实现突破性优化,可显著加快 Versal™ 自适应 SoC 硬件设计工作,与此同时大大简化了从旧架构到新架构的迁移。全新 Vivado Design Suite 带来更全面的性能优化、更快的编译速度和灵活的 RTL 设计流程,助您以更快速度实现设计成果。

Vivado Design Suite 优化改进

更快实现 FMAX 目标,更加智能的布线和时钟设置

更快的编译速度,布局布线速度提升最高可达 2 倍1,2,显著缩短设计周期

灵活的处理器启动方式,充分满足多样化的配置需求

适用于 NoC 和 SerDes 的 RTL 流程,带来熟悉的 FPGA 设计体验

新增资源

教程视频 – 渐进式的功能介绍

技术阐述 – 深度探讨(可下载)

培训课程 – 了解 AMD Versal 架构以及迁移方式

1. 基于 AMD 于 2024 年 12 月进行的一项测试,该测试分别使用 Vivado Design Suite 2024.2 和 Vivado Design Suite 2024.1 处理 124 个 Versal 堆叠芯片互联 (SSI) 技术器件的设计工作,以衡量平均编译时间(小时/分钟)。测出的编译时间因器件、设计、配置和其他因素而异 (VIV-011)。

2. 基于 AMD 于 2024 年 12 月进行的一项测试,该测试分别使用 Vivado Design Suite 2024.2 和 Vivado Design Suite 2024.1 处理 151 个 Versal 单片器件的设计工作,以衡量平均编译时间(小时/分钟)。测出的编译时间因器件、设计、配置和其他因素而异。(VIV-010)。

请点击阅读原文了解更多详情。

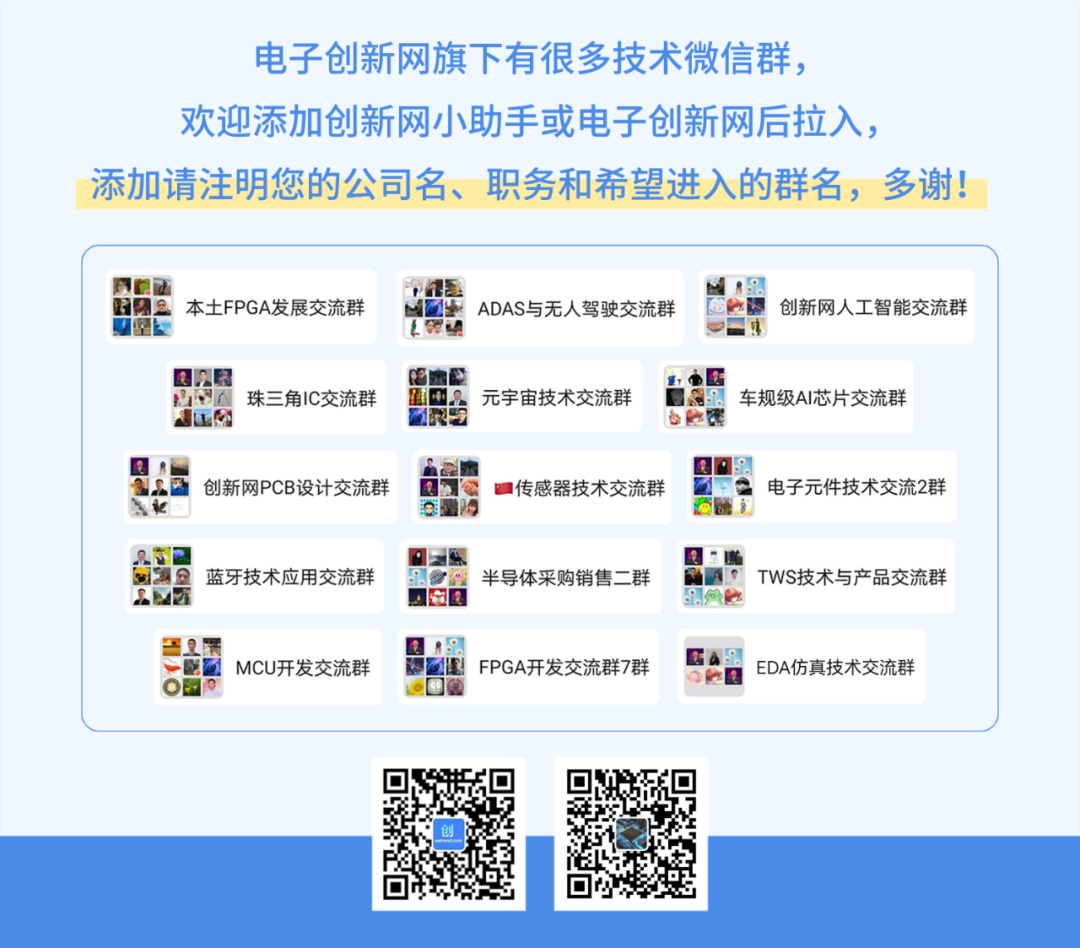

请扫码关注我们