网站:bbs.21ic.com

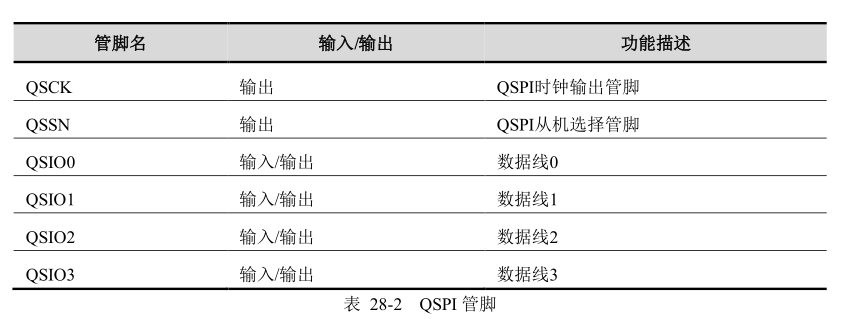

/* QSPCK Port/Pin definition *//* QSNSS Port/Pin definition *//* QSIO0 Port/Pin definition *//* QSIO1 Port/Pin definition *//* QSIO2 Port/Pin definition *//* QSIO3 Port/Pin definition */

static void QspiFlash_Init(void){stc_qspi_init_t stcQspiInit;/* configuration structure initialization */MEM_ZERO_STRUCT(stcQspiInit);/* Configuration peripheral clock */PWC_Fcg1PeriphClockCmd(PWC_FCG1_PERIPH_QSPI, Enable);/* Configuration QSPI pin */PORT_SetFunc(QSPCK_PORT, QSPCK_PIN, Func_Qspi, Disable);PORT_SetFunc(QSNSS_PORT, QSNSS_PIN, Func_Qspi, Disable);PORT_SetFunc(QSIO0_PORT, QSIO0_PIN, Func_Qspi, Disable);PORT_SetFunc(QSIO1_PORT, QSIO1_PIN, Func_Qspi, Disable);PORT_SetFunc(QSIO2_PORT, QSIO2_PIN, Func_Qspi, Disable);PORT_SetFunc(QSIO3_PORT, QSIO3_PIN, Func_Qspi, Disable);/* Configuration QSPI structure */stcQspiInit.enClkDiv = QspiHclkDiv3;stcQspiInit.enSpiMode = QspiSpiMode3;stcQspiInit.enBusCommMode = QspiBusModeRomAccess;stcQspiInit.enPrefetchMode = QspiPrefetchStopComplete;stcQspiInit.enPrefetchFuncEn = Disable;stcQspiInit.enQssnValidExtendTime = QspiQssnValidExtendSck32;stcQspiInit.enQssnIntervalTime = QspiQssnIntervalQsck8;stcQspiInit.enQsckDutyCorr = QspiQsckDutyCorrHalfHclk;stcQspiInit.enVirtualPeriod = QspiVirtualPeriodQsck8;stcQspiInit.enWpPinLevel = QspiWpPinOutputHigh;stcQspiInit.enQssnSetupDelayTime = QspiQssnSetupDelay1Dot5Qsck;stcQspiInit.enQssnHoldDelayTime = QspiQssnHoldDelay1Dot5Qsck;stcQspiInit.enFourByteAddrReadEn = Disable;stcQspiInit.enAddrWidth = QspiAddressByteThree;stcQspiInit.stcCommProtocol.enReadMode = QspiReadModeFourWiresOutput;stcQspiInit.stcCommProtocol.enTransInstrProtocol = QspiProtocolExtendSpi;stcQspiInit.stcCommProtocol.enTransAddrProtocol = QspiProtocolExtendSpi;stcQspiInit.stcCommProtocol.enReceProtocol = QspiProtocolExtendSpi;stcQspiInit.u8RomAccessInstr = QSPI_3BINSTR_FOUR_WIRES_OUTPUT_READ;QSPI_Init(&stcQspiInit);}

/*********************************************************************************** \brief De-Initialize QSPI unit**** \param [in] None**** \retval Ok Process successfully done********************************************************************************/en_result_t QSPI_DeInit(void)

/*********************************************************************************** \brief Initialize QSPI unit**** \param [in] pstcQspiInitCfg Pointer to qspi configuration** \arg See the struct #stc_qspi_init_t**** \retval Ok Process successfully done** \retval Error Parameter error********************************************************************************/en_result_t QSPI_Init(const stc_qspi_init_t *pstcQspiInitCfg)

/*********************************************************************************** \brief Config communication protocol structure**** \param [in] pstcCommProtocol Pointer to qspi communication protocol configuration** \arg See the struct #stc_qspi_comm_protocol_t**** \retval Ok Process successfully done** \retval Error Parameter error********************************************************************************/en_result_t QSPI_CommProtocolConfig(const stc_qspi_comm_protocol_t *pstcCommProtocol)

/*********************************************************************************** \brief Enable or disable prefetch function**** \param [in] enNewSta The function new state** \arg Disable Disable prefetch function** \arg Enable Enable prefetch function**** \retval Ok Process successfully done********************************************************************************/en_result_t QSPI_PrefetchCmd(en_functional_state_t enNewSta)

/*********************************************************************************** \brief Set clock division**** \param [in] enClkDiv Clock division** \arg QspiHclkDiv2 Clock source: HCLK/2** \arg QspiHclkDiv3 Clock source: HCLK/3** \arg QspiHclkDiv4 Clock source: HCLK/4** \arg QspiHclkDiv5 Clock source: HCLK/5** \arg QspiHclkDiv6 Clock source: HCLK/6** \arg QspiHclkDiv7 Clock source: HCLK/7** \arg QspiHclkDiv8 Clock source: HCLK/8** \arg QspiHclkDiv9 Clock source: HCLK/9** \arg QspiHclkDiv10 Clock source: HCLK/10** \arg QspiHclkDiv11 Clock source: HCLK/11** \arg QspiHclkDiv12 Clock source: HCLK/12** \arg QspiHclkDiv13 Clock source: HCLK/13** \arg QspiHclkDiv14 Clock source: HCLK/14** \arg QspiHclkDiv15 Clock source: HCLK/15** \arg QspiHclkDiv16 Clock source: HCLK/16** \arg QspiHclkDiv17 Clock source: HCLK/17** \arg QspiHclkDiv18 Clock source: HCLK/18** \arg QspiHclkDiv19 Clock source: HCLK/19** \arg QspiHclkDiv20 Clock source: HCLK/20** \arg QspiHclkDiv21 Clock source: HCLK/21** \arg QspiHclkDiv22 Clock source: HCLK/22** \arg QspiHclkDiv23 Clock source: HCLK/23** \arg QspiHclkDiv24 Clock source: HCLK/24** \arg QspiHclkDiv25 Clock source: HCLK/25** \arg QspiHclkDiv26 Clock source: HCLK/26** \arg QspiHclkDiv27 Clock source: HCLK/27** \arg QspiHclkDiv28 Clock source: HCLK/28** \arg QspiHclkDiv29 Clock source: HCLK/29** \arg QspiHclkDiv30 Clock source: HCLK/30** \arg QspiHclkDiv31 Clock source: HCLK/31** \arg QspiHclkDiv32 Clock source: HCLK/32** \arg QspiHclkDiv33 Clock source: HCLK/33** \arg QspiHclkDiv34 Clock source: HCLK/34** \arg QspiHclkDiv35 Clock source: HCLK/35** \arg QspiHclkDiv36 Clock source: HCLK/36** \arg QspiHclkDiv37 Clock source: HCLK/37** \arg QspiHclkDiv38 Clock source: HCLK/38** \arg QspiHclkDiv39 Clock source: HCLK/39** \arg QspiHclkDiv40 Clock source: HCLK/40** \arg QspiHclkDiv41 Clock source: HCLK/41** \arg QspiHclkDiv42 Clock source: HCLK/42** \arg QspiHclkDiv43 Clock source: HCLK/43** \arg QspiHclkDiv44 Clock source: HCLK/44** \arg QspiHclkDiv45 Clock source: HCLK/45** \arg QspiHclkDiv46 Clock source: HCLK/46** \arg QspiHclkDiv47 Clock source: HCLK/47** \arg QspiHclkDiv48 Clock source: HCLK/48** \arg QspiHclkDiv49 Clock source: HCLK/49** \arg QspiHclkDiv50 Clock source: HCLK/50** \arg QspiHclkDiv51 Clock source: HCLK/51** \arg QspiHclkDiv52 Clock source: HCLK/52** \arg QspiHclkDiv53 Clock source: HCLK/53** \arg QspiHclkDiv54 Clock source: HCLK/54** \arg QspiHclkDiv55 Clock source: HCLK/55** \arg QspiHclkDiv56 Clock source: HCLK/56** \arg QspiHclkDiv57 Clock source: HCLK/57** \arg QspiHclkDiv58 Clock source: HCLK/58** \arg QspiHclkDiv59 Clock source: HCLK/59** \arg QspiHclkDiv60 Clock source: HCLK/60** \arg QspiHclkDiv61 Clock source: HCLK/61** \arg QspiHclkDiv62 Clock source: HCLK/62** \arg QspiHclkDiv63 Clock source: HCLK/63** \arg QspiHclkDiv64 Clock source: HCLK/64**** \retval Ok Process successfully done********************************************************************************/en_result_t QSPI_SetClockDiv(en_qspi_clk_div_t enClkDiv)

/*********************************************************************************** \brief Set WP Pin level**** \param [in] enWpLevel WP pin level** \arg QspiWpPinOutputLow WP pin(QIO2) output low level** \arg QspiWpPinOutputHigh WP pin(QIO2) output high level**** \retval Ok Process successfully done********************************************************************************/en_result_t QSPI_SetWPPinLevel(en_qspi_wp_pin_level_t enWpLevel)

/*********************************************************************************** \brief Set communication address width**** \param [in] enAddrWidth Communication address width** \arg QspiAddressByteOne One byte address** \arg QspiAddressByteTwo Two byte address** \arg QspiAddressByteThree Three byte address** \arg QspiAddressByteFour Four byte address**** \retval Ok Process successfully done********************************************************************************/en_result_t QSPI_SetAddrWidth(en_qspi_addr_width_t enAddrWidth)

/*********************************************************************************** \brief Set extend address value**** \param [in] u8Addr Extend address value** \arg 0~0x3F**** \retval Ok Process successfully done********************************************************************************/en_result_t QSPI_SetExtendAddress(uint8_t u8Addr)

/*********************************************************************************** \brief Set rom access instruction**** \param [in] u8Instr Rom access instruction** \arg 0~0xFF**** \retval Ok Process successfully done********************************************************************************/en_result_t QSPI_SetRomAccessInstruct(uint8_t u8Instr)

/*********************************************************************************** \brief Read direct communication value**** \param [in] None**** \retval uint8_t Direct communication read value********************************************************************************/uint8_t QSPI_ReadDirectCommValue(void)

/*********************************************************************************** \brief Enable or disable xip mode**** \param [in] u8Instr Enable or disable xip mode instruction** \arg 0~0xFF**** \param [in] enNewSta The function new state** \arg Disable Disable xip mode** \arg Enable Enable xip mode**** \retval Ok Process successfully done********************************************************************************/en_result_t QSPI_XipModeCmd(uint8_t u8Instr, en_functional_state_t enNewSta)

/*********************************************************************************** \brief Enter direct communication mode**** \param [in] None**** \retval Ok Process successfully done**** \note If you are in XIP mode, you need to exit XIP mode and then start direct communication mode.********************************************************************************/en_result_t QSPI_EnterDirectCommMode(void)

/*********************************************************************************** \brief Exit direct communication mode**** \param [in] None**** \retval Ok Process successfully done********************************************************************************/en_result_t QSPI_ExitDirectCommMode(void)

/*********************************************************************************** \brief Get prefetch buffer current byte number**** \param [in] None**** \retval uint8_t Current buffer byte number********************************************************************************/uint8_t QSPI_GetPrefetchBufferNum(void)

/*********************************************************************************** \brief Get flag status**** \param [in] enFlag Choose need get status's flag** \arg QspiFlagBusBusy QSPI bus work status flag in direct communication mode** \arg QspiFlagXipMode XIP mode status signal** \arg QspiFlagRomAccessError Trigger rom access error flag in direct communication mode** \arg QspiFlagPrefetchBufferFull Prefetch buffer area status signal** \arg QspiFlagPrefetchStop Prefetch action status signal**** \retval Set Flag is set** \retval Reset Flag is reset********************************************************************************/en_flag_status_t QSPI_GetFlag(en_qspi_flag_type_t enFlag)

/*********************************************************************************** \brief Clear flag status**** \param [in] enFlag Choose need get status's flag** \arg QspiFlagRomAccessError Trigger rom access error flag in direct communication mode**** \retval Ok Process successfully done** \retval ErrorInvalidParameter Parameter error********************************************************************************/en_result_t QSPI_ClearFlag(en_qspi_flag_type_t enFlag)