超低损耗氮化硅薄膜光学数据

OMeda(上海奥麦达微)

超低损耗氮化硅薄膜光波导晶圆加工工艺:

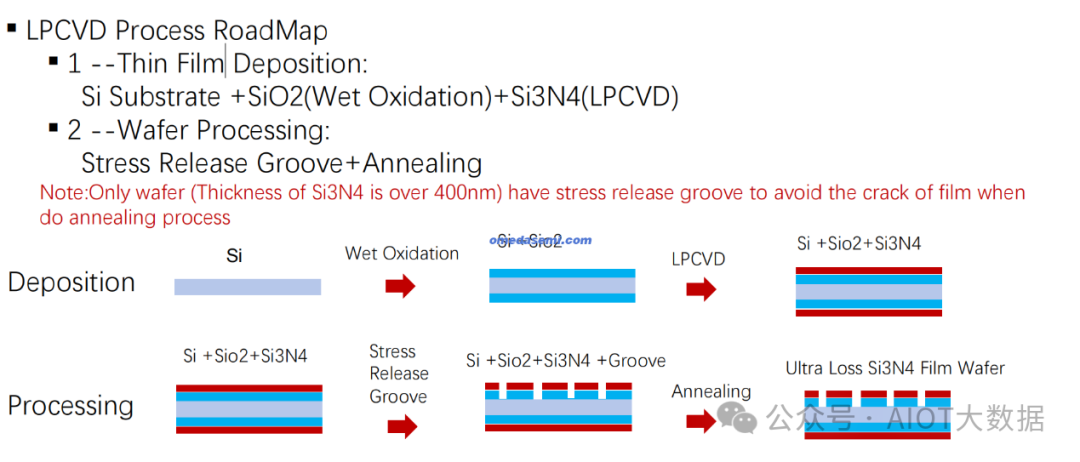

LPCVD工艺

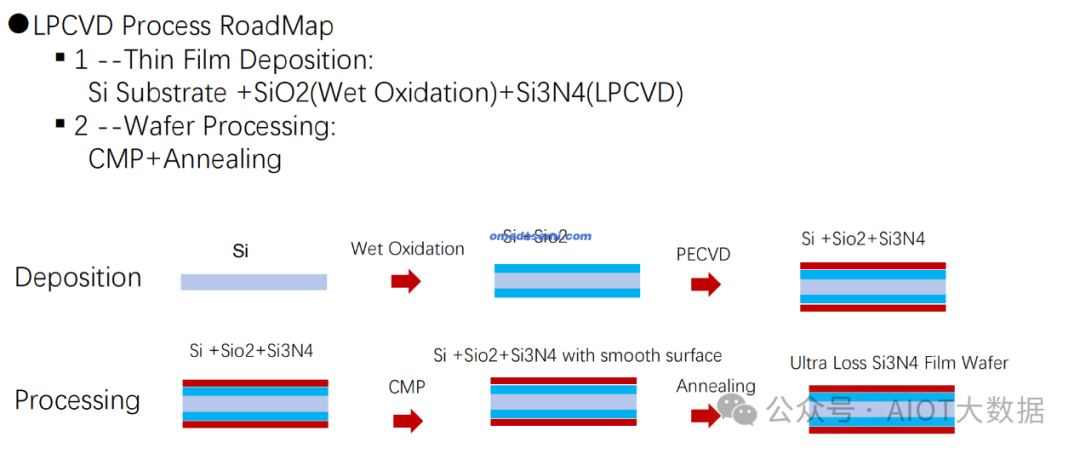

PECVD 工艺:

超低损耗氮化硅薄膜光波导晶圆加工是一种高精度微纳加工技术,特别适合用于光电子器件如传感器、滤波器和集成光学电路。氮化硅(Si3N4)因其高折射率和低损耗特性,广泛用于光波导制造。研究表明,通过优化沉积和蚀刻工艺,可实现传播损耗低至0.1 dB/cm,满足高性能光子集成电路的需求。

超低损耗氮化硅薄膜光波导晶圆加工是一种高精度微纳加工技术,特别适合用于光电子器件如传感器、滤波器和集成光学电路。氮化硅(Si3N4)因其高折射率和低损耗特性,广泛用于光波导制造。研究表明,通过优化沉积和蚀刻工艺,可实现传播损耗低至0.1 dB/cm,满足高性能光子集成电路的需求。

工艺流程

以下是超低损耗氮化硅薄膜光波导晶圆加工的详细步骤,适合小批量生产和研究环境。

1. 晶圆准备

·使用清洁硅晶圆,确保表面无污染物,可通过溶剂清洗或超声波清洗实现。

·生长下覆层SiO2:

o方法:热氧化

o厚度:1-2微米

o温度:1000°C

o时间:根据氧化速率调整以达到所需厚度。

2. 氮化硅核心层沉积

·方法:使用ICP-PECVD,采用氘化硅(SiD4)和氮气(N2)作为前驱体。

·参数:

o温度:250°C

o气流:优化SiD4和N2的比例以获得理想折射率和膜质

o压力:1-10 Torr

oRF功率:根据系统优化

·膜厚:根据设计需求,通常为100-500纳米。

·研究表明,使用SiD4可显著降低氢相关吸收损耗,适合超低损耗应用。

3. 波导图案化

·光刻:

o使用合适的光刻胶和掩模设计波导图案。

·干法蚀刻:

o方法:ICP-RIE,使用CHF3/O2混合气。

o参数:

§气流:CHF3 20-50 sccm,O2 5-10 sccm

§压力:5-10 mTorr

§ICP功率:200-500 W

§RIE功率:50-100 W

§温度:室温

o优化蚀刻参数以确保侧壁光滑和垂直轮廓,减少散射损耗 。

4. 上覆层沉积

·方法:PECVD SiO2

·参数:

o温度:250-300°C

o前驱体:硅烷(SiH4)和氧气(O2)或氧化亚氮(N2O)

o气流:优化以确保低损耗和均匀厚度

o压力:1-10 Torr

oRF功率:50-100 W

·厚度:足够覆盖波导结构,通常为1-2微米。

5. 退火(可选)

·温度:1000-1200°C

·时间:数小时

·目的:减少任何剩余的氢相关吸收或稳定膜性能。

6. 后处理

·清洗晶圆,移除任何残留物。

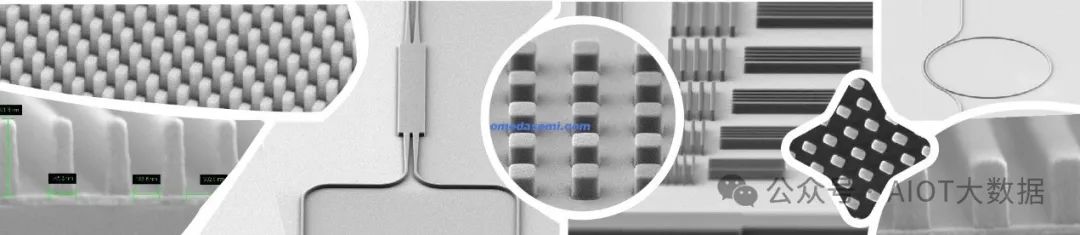

·使用扫描电子显微镜(SEM)或原子力显微镜(AFM)检查结构质量,验证波导尺寸和光滑度。

·进行光学性能测试,如使用光谱仪测试耦合效率和波长选择特性。

氮化硅薄膜在光子集成电路中的应用分析

氮化硅(Si3N4)在光子集成电路(PIC)领域中的应用广泛,主要得益于其独特的物理特性和技术优势:

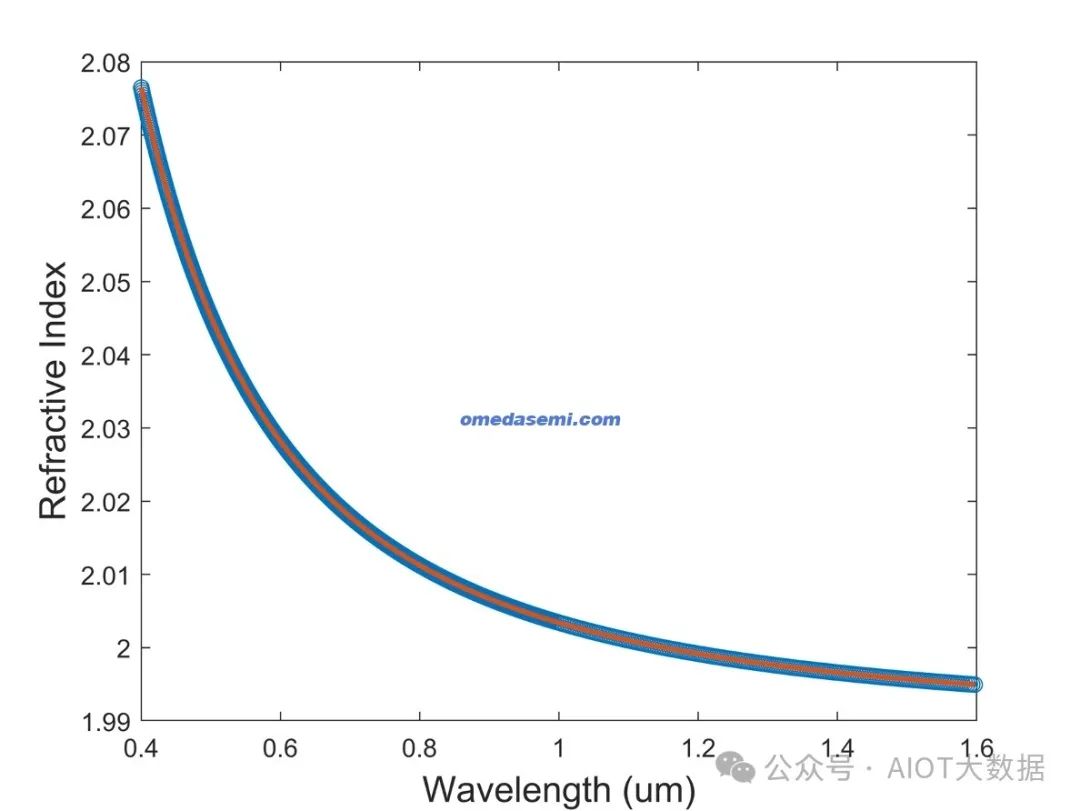

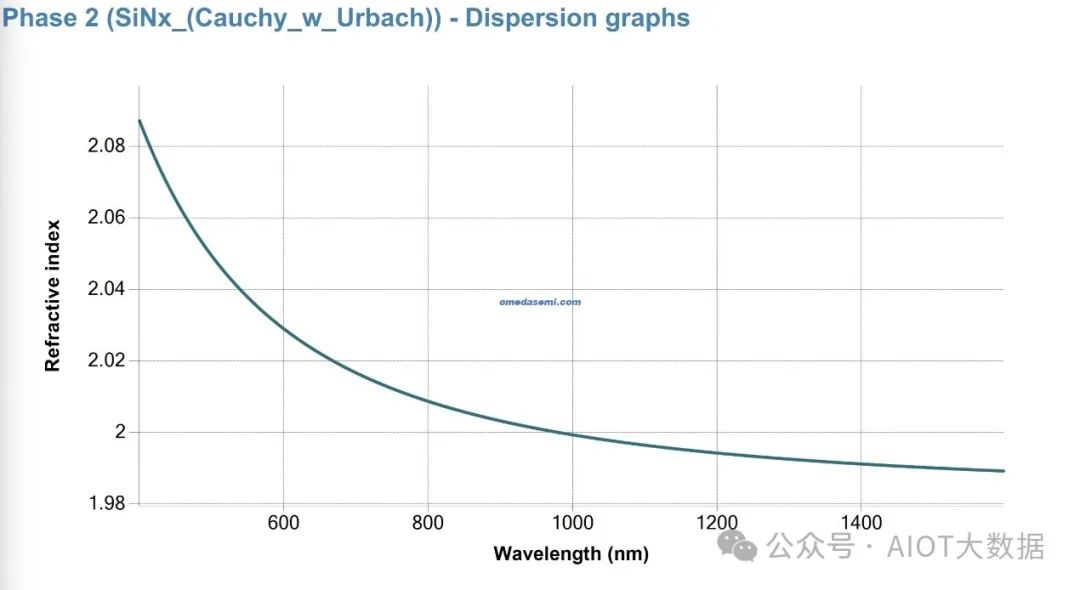

极低的光学损耗:Si3N4材料在从可见光至中红外(MIR)波段展现出极低的光学损耗(≤1 dB/m),这一特性对于实现高效光信号传输至关重要,适用于多种光学元件和系统。

超宽带光谱透明性:氮化硅在波长范围从400纳米至2350纳米的区域内保持透明,从而支持在极宽的光谱范围内操作,适用于多种跨波长光学应用。

CMOS工艺兼容性:Si3N4与互补金属氧化物半导体工艺的高度兼容性,使其能够无缝集成到现有的半导体制造流程中,简化了生产流程并推动了集成光子技术的进步。

高功率光学系统适用性:氮化硅卓越的热稳定性和机械强度使其能够承受高功率光学的应用环境,对于涉及高功率光源或光放大的场景至关重要。

多样化的器件制造:Si3N4适用于制造多种光子器件,包括波导、谐振器、滤波器、光调制器和光探测器等,其设计灵活性和制造能力满足了光子学领域的多样化需求。

材料集成能力:氮化硅能够与其他材料(如硅Si和III-V族半导体)有效集成,为开发具有复合功能的混合光子器件提供了可能性。

综上所述,氮化硅薄膜因其低光学损耗、宽带透明性、CMOS工艺兼容性、高功率耐受性、器件制造的多样性以及与其他材料的集成潜力,成为光子学领域,包括电信、传感、光谱分析、成像和量子技术等多个应用领域的理想选择。

氮化硅薄膜基片全球供应的现状

氮化硅、铌酸锂和硅光是目前光波导技术的三大主流平台。在光子集成电路领域,铌酸锂和硅光技术分别采用薄膜铌酸锂晶圆和绝缘体上硅(SOI)晶圆。这些产品市场已经形成了稳定的商业化格局,并拥有可靠的供应链。

具体来说,SOI晶圆的主要供应商包括上海新傲科技股份有限公司和法国的SOITEC公司。而薄膜铌酸锂晶圆的供应则由济南晶正新材料有限公司等企业负责。这些企业为市场提供了稳定的产品供应,满足了行业的需求。

然而,对于氮化硅(Si3N4)光波导基片的获取,国内情况则相对不利。目前,国内科研机构和科学家主要依赖国外流片平台获取Si3N4光波导基片,而国内尚缺乏成熟的技术和企业来提供商业化的氮化硅光波导基片。这种情况带来了以下几方面的不利影响:

成本高昂:国外企业提供的氮化硅光波导基片价格昂贵,增加了国内研发和生产成本。

交货周期长:由于依赖进口,氮化硅光波导基片的交货周期往往较长,影响了项目的进度。

服务不便:国外供应商的售后服务存在时差等问题,为国内用户带来了不便。

这种现状严重制约了国内氮化硅光子集成电路技术的发展和应用,同时也降低了研发效率。通常,从基片采购到成品器件的完成,整个过程可能需要数月时间,这在一定程度上延缓了技术进步和市场推广。

为解决这一问题,国内有必要加快氮化硅光波导基片的生产技术研发,培育具有国际竞争力的本土企业,以促进国内光子集成电路技术的快速发展。

以下详细介绍一下各种光波导光栅的三种光刻工艺:DUV\电子束\激光直写

150nmDUV步进式光刻工艺

技术背景

在半导体制造中,光刻胶图案化的关键技术包括接触式曝光(极限线宽2微米)、激光直写(500纳米)、步进式曝光(Krf光源150纳米,ArF光源90纳米)、纳米压印技术和电子束光刻(均可达数十纳米)。我国在电子束光刻、激光直写、接触式光刻和纳米压印设备方面已达到较高水平,但电子束光刻成本高、产量低,纳米压印需制备高成本的1:1复制母版,工艺复杂。

国内步进式曝光设备多用于科研院所和高校,DUV光源线宽通常在350nm、450nm、500nm以上。随着AR衍射光波导、超透镜和光子集成电路等行业快速发展,市场对线宽要求已提升至250nm以下,150nm DUV步进式光刻成为重要解决方案。

工艺流程

以下是150nm DUV步进式光刻的详细工艺流程,旨在确保一致性和可重复性,适合大规模生产环境。

1. 掩模设计与制作

·设计图案需按掩模缩放比5:1缩放。例如,晶圆上150nm的特征,对应掩模上的特征为750nm。

·使用铬-石英掩模,适合DUV曝光,确保图案精度。

2. 晶圆准备

·使用6英寸晶圆,厚度1mm。

·清洗晶圆以去除污染物,常用RCA清洗或Piranha清洗,随后用去离子水冲洗并干燥。

3. 光刻胶涂覆

·使用适合KrF光源的化学放大光刻胶(如基于聚对羟基苯乙烯的正胶)。

·典型厚度为200-500nm,通过旋涂施加。

·软烘以去除溶剂,参数依光刻胶制造商推荐。

4. 曝光

·使用步进式曝光系统,KrF光源(248nm),掩模缩放比5:1。

·优化曝光剂量、聚焦和对准参数。

·设备支持最大DIE尺寸22x22mm,每小时处理20片6英寸晶圆。

5. 曝光后烘烤(PEB)

·对化学放大光刻胶进行PEB,激活光化学反应。

·温度和时间依光刻胶规格调整。

6. 显影

·使用碱性显影液(如TMAH溶液)显影正胶。

·优化显影时间和浓度,确保图案清晰。

7. 图案转移

·根据应用选择干法刻蚀(如RIE)或湿法刻蚀,将图案转移至底层。

·刻蚀参数依材料(如氮化硅、铌酸锂)调整。

8. 光刻胶去除

·使用等离子体灰化或湿法剥离去除残留光刻胶。

设备规格

以下是设备的关键参数,适合高精度、高效率生产:

参数 | 规格 |

晶圆尺寸 | 6英寸 |

单颗DIE最大尺寸 | 22x22毫米 |

最小线宽 | 150纳米 |

掩模缩放比 | 5:1 |

对准精度 | ≤40纳米 |

对焦精度 | ≤100纳米 |

步进精度 | ≤20纳米 |

套刻精度 | 30-50纳米 |

支持晶圆厚度 | 1毫米 |

处理量 | 每小时20片6英寸晶圆 |

应用领域

该工艺适用于150nm线宽以上的微纳结构制造,包括但不限于:

·衍射光波导

·超结构

·氮化硅波导

·铌酸锂光波导

·硅光波导

·其他微机电系统(MEMS)结构

质量控制与检查

·光刻胶涂覆后: 检查厚度均匀性。

·显影后: 使用光学显微镜或扫描电子显微镜(SEM)检查图案保真度和特征尺寸。

·刻蚀后: 测量刻蚀深度和侧壁形貌,确保符合规格。

安全注意事项

·处理化学品时需佩戴适当的个人防护装备(PPE)。

·确保通风良好,遵循危险废物处置程序。

·曝光设备涉及高电压和激光,需遵守制造商的安全指南。

电子束光刻(EBL)工艺加工光波导光栅

电子束光刻(EBL)是一种高分辨率的光刻技术,利用聚焦电子束在涂有电子敏感薄膜(即抗蚀剂或光刻胶)的基底上绘制自定义图案。该技术特别适合需要亚纳米级分辨率的领域,如半导体小批量生产、光掩模制造和纳米技术研究。EBL通过电子束改变光刻胶的溶解性,通过显影选择性地去除曝光或未曝光区域,最终通过刻蚀将图案转移到基底材料上。其主要优点包括高分辨率(可达亚10纳米)、无需掩模的直接写入能力和高精度定位,适合精密加工。然而,由于其串行处理特性,产量低,限制了其在光掩模制造、半导体小批量生产以及研究与开发中的应用。

设备与材料

电子束写入系统

常见的电子束写入系统包括JEOL、Raith等品牌的设备,这些系统通常配备:

·热场发射电子枪,提供高亮度和稳定性。

·高加速电压(10-100 kV),用于控制分辨率和电子穿透深度。

·精密舞台控制,确保图案放置准确。

多束系统(如2022年状态的先进多束写入器,可实现约20纳米分辨率)正在开发中,以提高写入速度,适合更高效率的小批量生产。

抗蚀剂(光刻胶)

EBL抗蚀剂分为正胶和负胶:

·正胶:曝光后溶解性增加,被显影液去除。常见种类包括PMMA(聚甲基丙烯酸甲酯)、ZEP和PBS。PMMA是行业标准,易于处理,适用于高分辨率特征和剥离工艺。

·负胶:曝光后溶解性降低,未曝光区域被去除。常见种类包括SU-8和某些酚醛树脂基抗蚀剂。

选择标准包括分辨率需求、电子束敏感度(所需剂量)、基底附着力和后续工艺兼容性(如刻蚀或剥离)。

基底

常见基底包括硅片、玻璃和金属膜,选择取决于应用和最终器件性能要求。

基底准备

基底准备是确保图案质量的关键步骤,常用清洗方法包括:

·溶剂清洗:使用丙酮和异丙醇去除有机残留。

·Piranha清洗:硫酸和过氧化氢混合液,用于更彻底去除有机物。

·RCA清洗:一系列步骤去除有机、金属和氧化物污染物,适用于高洁净度需求。

根据具体应用,选择合适的清洗方法。例如,对于硅片,小批量生产中溶剂清洗通常足够,而研究中可能需要RCA清洗。

工艺步骤

以下是EBL的详细工艺流程,旨在确保一致性和可重复性,适合小批量生产环境。

1. 基底准备

·清洗:首先使用溶剂(如丙酮和异丙醇)清洗硅片,去除有机残留,随后用去离子水冲洗。必要时,可使用Piranha清洗或RCA清洗以提高洁净度。

·干燥:确保基底表面干燥,避免水分影响光刻胶附着力。

2. 光刻胶涂覆

·旋转涂覆:将光刻胶(如PMMA)滴在基底上,通过高速旋转(通常2000-4000 rpm,持续60秒)形成均匀薄膜。例如,对于4% PMMA溶液,2000 rpm可得约250 nm厚度。

·烘烤:烘烤去除溶剂并增强附着力,PMMA通常在160-180°C下烘烤30-60分钟。

3. 电子束曝光

·参数设置:加速电压通常为10-100 kV,束流电流影响曝光时间和点大小,曝光剂量(如PMMA为100-300 μC/cm²)需根据图案密度和特征尺寸优化。

·图案设计:使用CAD软件设计图案,转换为电子束写入系统兼容的格式(如GDSII)。

·邻近效应校正:对于高密度图案,需进行邻近效应校正,以补偿电子散射影响,确保特征尺寸一致。

4. 显影

·正胶(如PMMA):常用显影液为MIBK:IPA混合液(如1:3高对比度,1:1高敏感度),显影时间和温度需优化,具体取决于图案和厚度。

·负胶:使用水性显影液去除未曝光区域。

5. 图案转移

·刻蚀:根据基底材料选择干法刻蚀(如RIE、ICP-RIE)或湿法刻蚀,参数包括气体流量、压力、功率和时间。例如,硅基底可使用HF刻蚀氧化物,或RIE实现各向异性刻蚀。

·剥离:对于金属沉积,图案作为模板,沉积后去除光刻胶,剥离未覆盖区域的金属。

6. 光刻胶去除

·溶剂去除:正胶可用丙酮去除,负胶可能需等离子体灰化或专用剥离剂。

质量控制与检查

·扫描电子显微镜(SEM):检查图案保真度和特征尺寸。

·原子力显微镜(AFM):测量表面形貌和粗糙度。

·光学显微镜:初步检查较大特征。

故障排除

常见问题及其解决方法:

·附着力差:确保清洗彻底,烘烤条件适当。

·图案失真:检查曝光剂量和邻近效应校正。

·显影问题:优化显影液浓度、时间和温度。

·刻蚀问题:验证刻蚀参数,监控过程。

安全注意事项

·化学品处理:使用适当的个人防护装备(PPE),遵循危险废物处置程序。

·电子束安全:高电压系统存在电击和X射线生成风险,遵循制造商安全指南和培训协议。

优化产量

尽管EBL产量低,但可通过以下策略优化:

·多束系统:使用多电子束系统并行写入,提高速度,如2022年状态的先进多束写入器可达20纳米分辨率。

·图案优化:设计图案减少写入时间,如使用较大形状,减少束流偏转。

·抗蚀剂选择:选用高敏感度抗蚀剂,降低所需曝光剂量。

·过程自动化:尽可能自动化过程,提高一致性和效率。

表格:常见抗蚀剂参数

抗蚀剂类型 | 例子 | 敏感度(μC/cm²) | 典型厚度(nm) | 应用场景 |

正胶 | PMMA | 100-300 | 100-500 | 高分辨率特征,剥离 |

正胶 | ZEP | 10-50 | 50-300 | 掩模制造 |

负胶 | SU-8 | 50-200 | 500-2000 | MEMS结构 |

飞秒激光直写光刻工艺

飞秒激光直写光刻(Femtosecond Laser Direct Writing, FLDW)是一种基于飞秒激光技术的高精度微纳加工方法,特别适合在氮化硅薄膜晶圆上制作光波导光栅。

飞秒激光直写光刻利用飞秒激光的极短脉冲(通常在10^-15秒量级)和高峰值功率,直接在材料表面或内部写入图案,实现高分辨率的微纳结构。氮化硅(Si3N4)薄膜因其良好的机械和光学性能,常用于集成光学中的光波导,飞秒激光加工可用于创建光波导和光栅结构,用于光电子器件如传感器和滤波器。

技术背景

飞秒激光直写的基本原理依赖于非线性吸收效应,如多光子吸收或非线性离子化,极短脉冲宽度减少热扩散和热损伤。研究表明,飞秒激光可通过折射率修改或烧蚀在氮化硅薄膜上创建结构,但具体方法存在争议,需根据薄膜厚度和应用场景选择。

工艺流程

以下是飞秒激光加工光波导光栅的详细步骤,适合小批量生产和研究环境。

1. 样品准备

·使用氮化硅薄膜晶圆,厚度通常为500纳米至1微米,沉积在硅衬底上。

·确保样品清洁,使用溶剂清洗或超声波清洗去除污染物。

·将样品固定在激光加工系统的三维扫描平台上。

2. 激光系统设置

·使用飞秒激光器,参数包括:

o波长:800纳米(近红外,适合氮化硅的非线性吸收)。

o脉宽:小于100飞秒。

o重复频率:100千赫兹。

·使用高数值孔径(NA=0.8)物镜聚焦激光束,聚焦光斑尺寸约为1微米。

·设置激光功率和扫描速度,初步建议:

o光波导折射率修改:功率5毫瓦,扫描速度10微米/秒。

o光栅烧蚀:功率10毫瓦,扫描速度1毫米/秒。

·根据初步实验优化参数,确保达到所需结构深度和精度。

3. 图案设计

·设计光波导路径,通常为直线或弯曲通道,宽度根据应用需求(如1微米)。

·设计光栅部分,确定周期和长度,例如周期500纳米,用于特定工作波长。

·使用CAD软件设计图案,转换为激光控制系统兼容格式。

4. 激光写入

·对准激光束,确保聚焦在氮化硅薄膜内或表面。

·首先写入光波导路径,通过扫描系统沿设计路径移动激光束。

·随后写入光栅图案,若为折射率修改,在波导内创建周期性指数变化;若为烧蚀,在表面创建周期性结构。

·监控过程,确保一致性,避免热损伤。

5. 后处理

·清洗样品,移除烧蚀过程中可能产生的碎片,使用超声波清洗或溶剂。

·使用扫描电子显微镜(SEM)或原子力显微镜(AFM)检查结构质量,验证光波导和光栅的尺寸和周期。

·若需要,可进行退火处理以稳定结构。

设备规格

以下是典型飞秒激光加工系统的参数,适合高精度加工:

参数 | 规格 |

激光波长 | 800纳米 |

脉宽 | < 100飞秒 |

重复频率 | 100千赫兹 |

平均功率 | 可调,5-50毫瓦 |

聚焦物镜NA | 0.8 |

聚焦光斑尺寸 | ~1微米 |

扫描系统精度 | 子微米级 |

应用场景

飞秒激光加工光波导光栅广泛应用于以下领域:

·光电子器件:制作光子晶体、光波导和集成光学器件。

·传感器:用于光纤传感器或平面波导传感器。

·滤波器:光栅可用于波长选择和光信号处理。

·研究与开发:探索新材料和结构的微纳加工特性。

质量控制与检查

·光波导检查:使用光学显微镜验证路径连续性,SEM测量宽度。

·光栅检查:AFM测量周期和深度,SEM验证结构均匀性。

·光学性能测试:使用光谱仪测试光栅的耦合效率和波长选择特性。

安全注意事项

·处理激光设备时需佩戴适当的个人防护装备(PPE),包括激光防护眼镜。

·确保通风良好,处理化学清洗剂时遵循危险废物处置程序。

·高功率激光可能产生热效应,需监控样品避免过热。

优化产量

尽管飞秒激光加工适合小批量生产,可通过以下策略提高效率:

·优化激光参数,减少单次写入时间。

·使用高重复频率激光器,加快扫描速度。

·设计图案减少复杂扫描路径。

争议与不确定性

研究表明,飞秒激光可通过折射率修改或烧蚀创建光波导光栅,但具体方法存在争议。折射率修改适合三维结构,但氮化硅薄膜厚度有限可能限制其应用;烧蚀方法更直观,但可能引入表面粗糙度影响光学性能。建议根据应用需求和初步实验选择最佳方法。

(END)

文章来源:AIOT大数据 公众号