近日,在2025年IEEE国际固态电路会议(ISSCC 2025)上,英特尔分享了数项研究进展,涵盖协议级集成、集成电源和热管理、硅光集成等多个前沿技术领域。这是全球固态电路和系统芯片领域最重要的论坛,汇聚了行业顶尖专家和前沿技术成果。

英特尔代工技术开发高级副总裁Navid Shahriari在大会上发表了题为《AI时代的创新矩阵》的主题演讲。他表示,AI的强大潜力,既提高了人类快速、精准解决复杂问题的能力,也帮助我们开拓了视野,能够更好地理解事物与探索创新。随着数据处理需求的增长,需要在更小的芯片面积上实现更高计算能力和更低能耗。此外,并行AI工作负载的指数级增长对互连带宽密度、延迟和功耗提出了更高的要求。AI系统的扩展需求正在推动制程、封装、架构和软件领域的前沿创新。

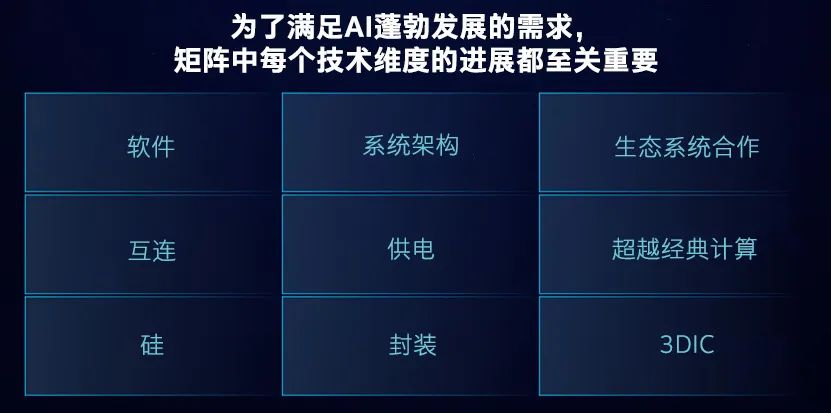

从芯片到整个系统,英特尔正在围绕一个技术矩阵进行创新,以满足AI时代的算力需求。“从软件和系统架构到硅和先进封装,每个领域的进展都是必要的,但整个系统必须共同优化,以最大限度地提高性能和功耗,并降低成本。此外,强大的生态系统合作伙伴和新颖的设计方法论对于有效的协同优化和产品上市速度的加快也至关重要。” Shahriari在演讲中强调。

AI的成长需要技术“叠叠乐”:

🔥 本届大会英特尔一口气展示了多篇重磅研究,完整论文内容目前仅限ISSCC 2025现场参会者获取。不过别急!小编马上放送论文摘要的英文原文,带您快速解锁半导体圈前沿技术风向👇

A 0.021μm2 High-Density SRAM in Intel 18A RibbonFET Technology with PowerVia Backside Power Delivery

Session 29 – SRAM

A 0.9pJ/b 108Gb/s PAM-4 VCSEL-Based Direct-Drive Optical Engine

Session 36 – Ultra-High-Density D2D and High-Performance Optical Transceivers

A 300MB SRAM, 20Tb/s Bandwidth Scalable Heterogenous 2.5D System Inferencing Simultaneous Streams Across 20 Chiplets with Workload-Dependent Configurations

Session 2 – Processors

A Fully Integrated Multi-Phase Voltage Regulator with Enhanced Light-Load-Efficiency Peak of 86%, Featuring an Autonomous Mode Transition from Hard-Switching to Soft-Switching to Discontinuous Conduction Mode in 3nm FinFET CMOS

Session 21 – Compute and USB Power

Fine-Grained Spatial and Temporal Thermal Profiling of a 16nm CMOS Buck Converter and SOC Load-Current Emulator Using Low-Voltage Micron-Scale Thermal Sensors

Session 8 – Digital Techniques for System Adaptation, Power Management and Clocking

©英特尔公司,英特尔、英特尔logo及其它英特尔标识,是英特尔公司或其分支机构的商标。文中涉及的其它名称及品牌属于各自所有者资产。

相关资讯

/转载请注明出处/