大侠好,欢迎来到FPGA技术江湖。本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。本次带来Vivado系列,Vivado逻辑分析仪使用教程。话不多说,上货。

Vivado 逻辑分析仪使用教程

作者:李西锐 校对:陆辉

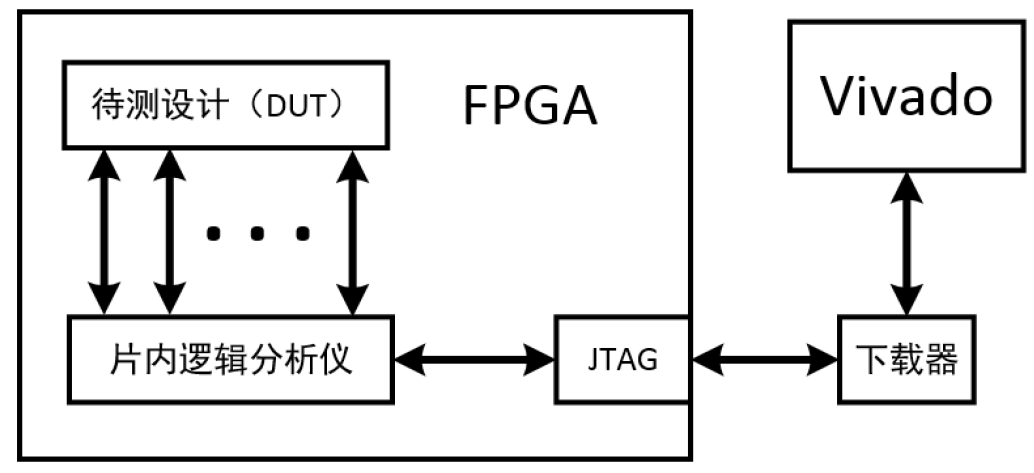

传统的逻辑分析仪在使用时,我们需要将所要观察的信号连接到FPGA的IO管脚上,然后观察信号。当信号比较多时,我们操作起来会比较繁琐。在线逻辑分析仪就比较好的解决了这个问题,我们可以将这些功能加到FPGA设计当中。

其中待测设计就是我们整个的逻辑设计模块,在线逻辑分析仪也同样是在FPGA设计中。通过一个或多个探针来采集希望观察的信号。然后通过JTAG接口,将捕获到的数据通过下载器回传给我们的用户界面,以便我们进行观察。

在逻辑分析仪使用的过程中,我们一般常用的调用方法有两种:

1、IP核

2、mark debug标记信号

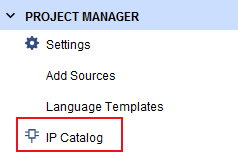

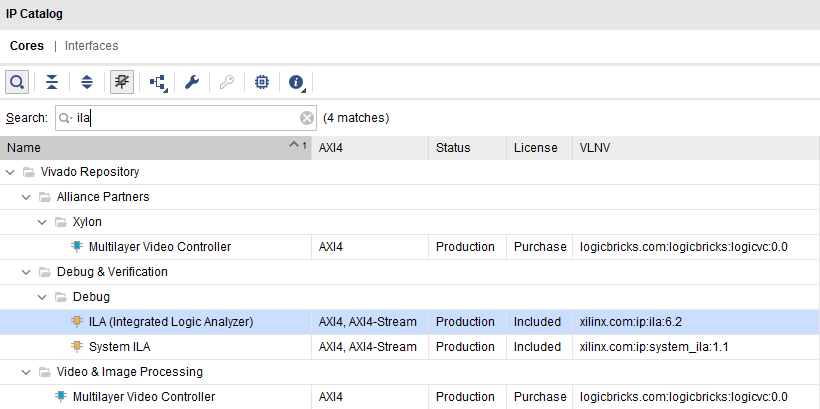

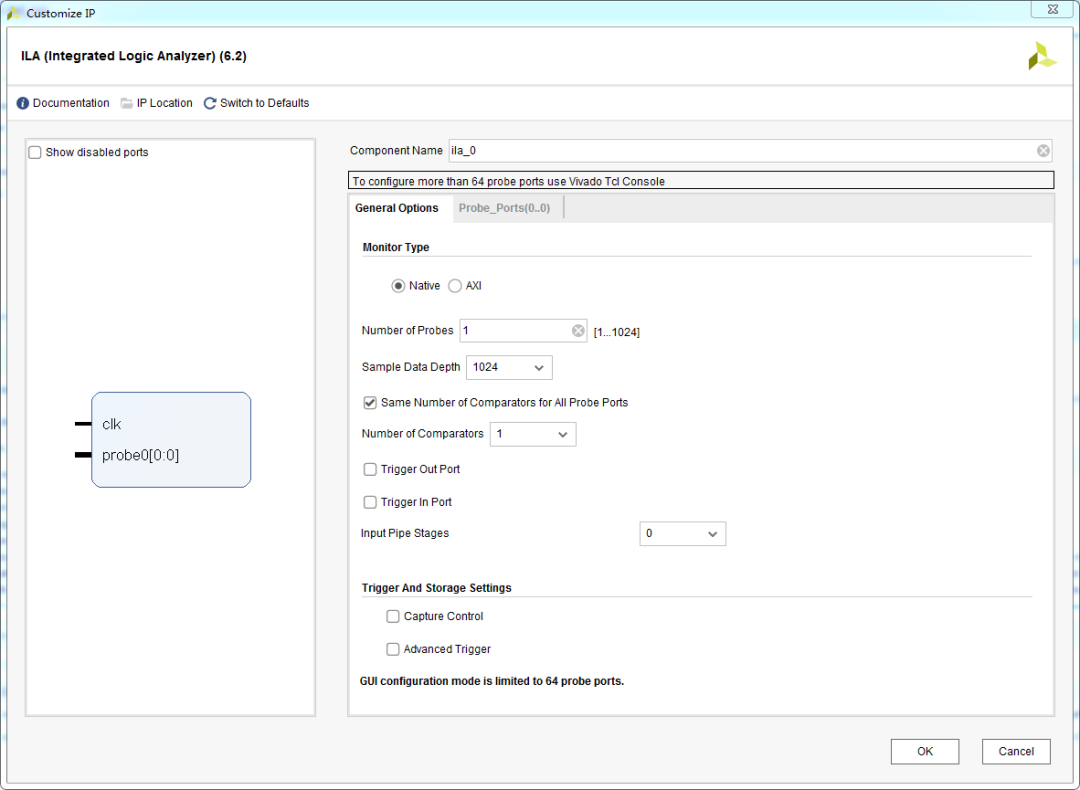

接下来我们先说一下第一种方法。这种方法需要我们打开IP核管理器,在程序设计中例化ILA。首先我们打开IP核管理器,搜索ILA,双击打开。

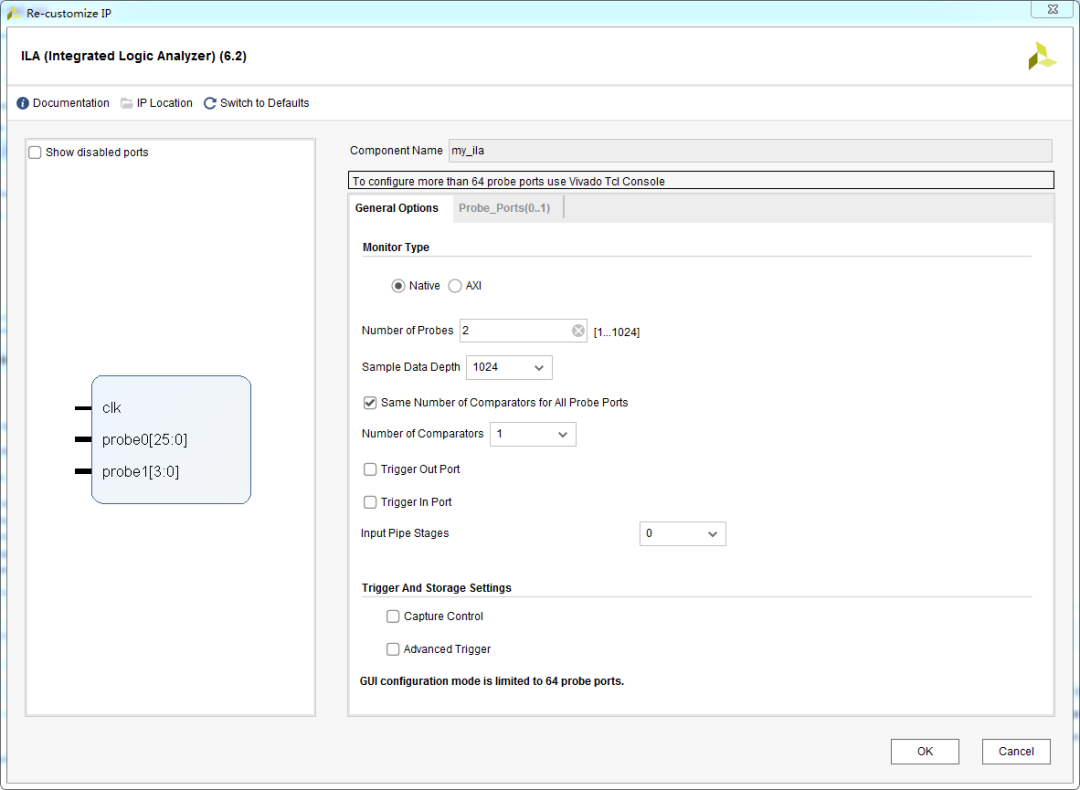

在此配置界面,我们配置几项内容。首先是Component Name,我们可以给我们的逻辑分析仪起一个名字,比如我在此改为my_ila。

在number of probes选项选择我们需要观察的信号个数,我们以流水灯为例,我们可以观察一下代码设计当中的计数器cnt以及输出led。所以我们在此项设置为2。Sample data depth为采样深度,采样深度影响到了我们可以观察的信号长度,大家可以根据自己的需要进行设置,在此我选择深度为1024。

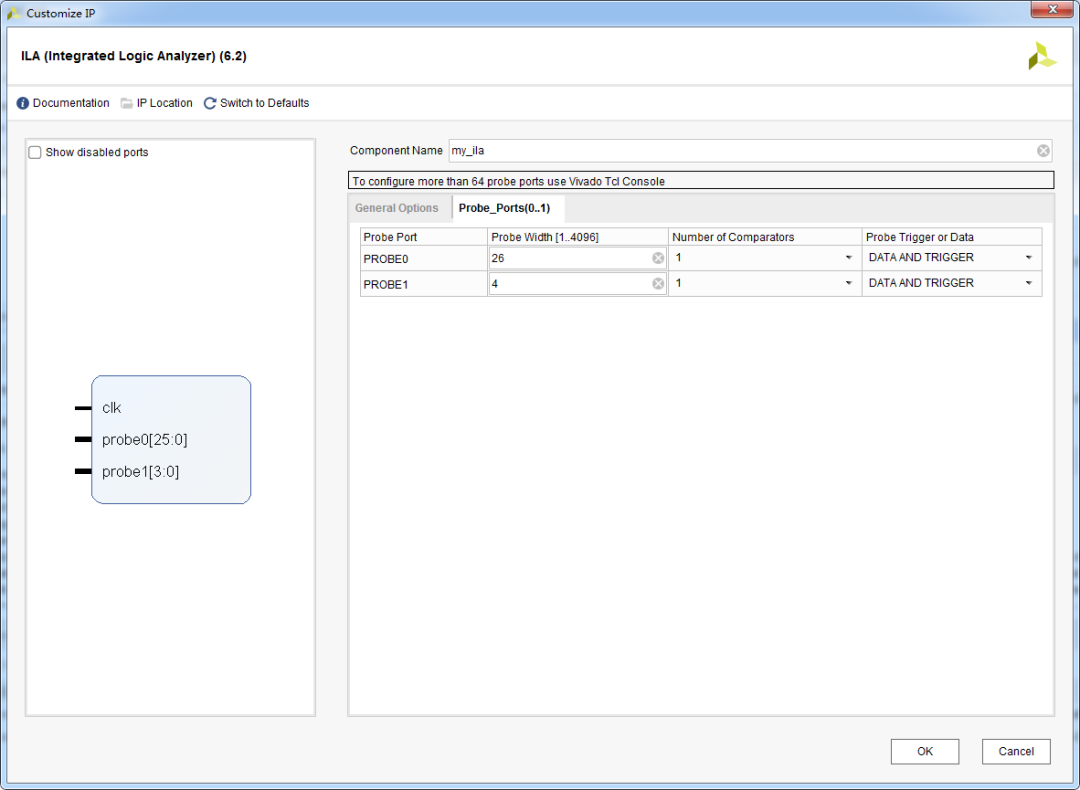

然后在Probe ports里面设置被观察信号的位宽。计数器为26位,led输出为4位,那么我们将位宽设置好,点击OK生成IP核。

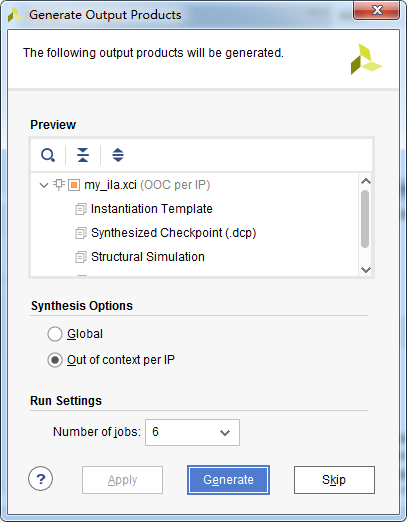

在这里,我们简要介绍一下Vivado的OOC(Out-of-Context)综合的概念。对于顶层设计,Vivado使用自顶向下的全局(Global)综合方式,将顶层之下的所有逻辑模块都进行综合,但是设置为OOC方式的模块除外,它们独立于顶层设计而单独综合。通常,在整个设计周期中,顶层设计会被多次修改并综合。但有些子模块在创建完毕之后不会因为顶层设计的修改而被修改,如IP,它们被设置为OOC综合方式,OOC模块只会在综合顶层之前被综合一次。这样,在顶层的设计迭代过程中,OOC模块就不必跟随顶层模块,而进行一次次的会产生相同结果的多余的综合了。所以,OOC流程减少了设计周期时间,并消除了设计迭代,使大家可以保存和重用综合结果。

Out-of-Context(OOC) 综合是一种自底向上的设计流程,默认情况下,Vivado设计套件使用OOC的设计流程来综合OOC模块。OOC模块可以是来自IP catalog的IP、来自Vivado IP Integrator的block design或者顶层模块下手动设置为OOC方式的任何子模块。

来自IP catalog的IP就默认使用OOC综合的方式,例如上图中的“Synthesis Options”选项就设置为了“Out of Context Per IP”。这些IP会在顶层的全局综合之前,单独地进行OOC综合并生成输出产品(Generate Output Products),包括综合后的网表等各种文件。在对顶层进行综合时,OOC模块会被视为黑盒子,并且不会参与到顶层的综合中来。在综合之后的实现过程中,OOC模块的黑盒子才会被打开,这时其网表才是可见的并参与到全局设计的布局布线中来。

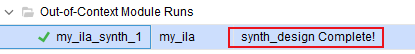

OOC综合完毕之后如下图所示:

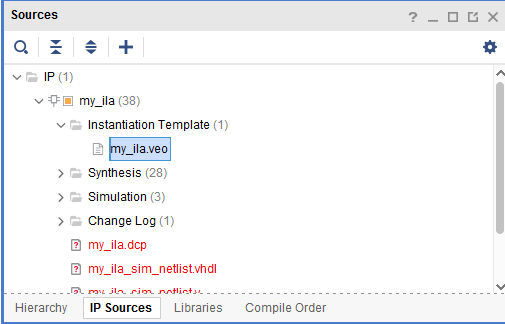

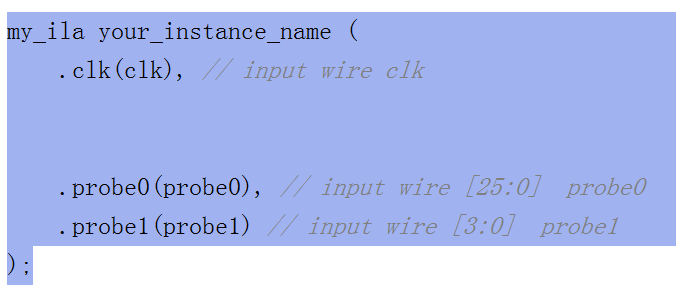

IP核调用完成之后,我们在IP sources窗口中打开IP核的instantiation template。my_ila.veo文件为例化的头文件,我们双击打开,将下图内容复制粘贴到顶层文件当中即可。

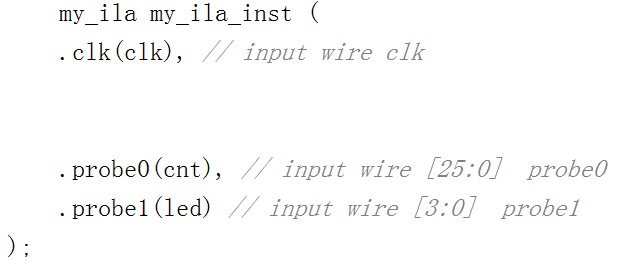

复制好之后,我们将信号做一下连线,改一下例化名。那么我们的逻辑分析仪调用就完成了。

调用完成之后,我们将文件保存,然后生成下板文件进行下板。

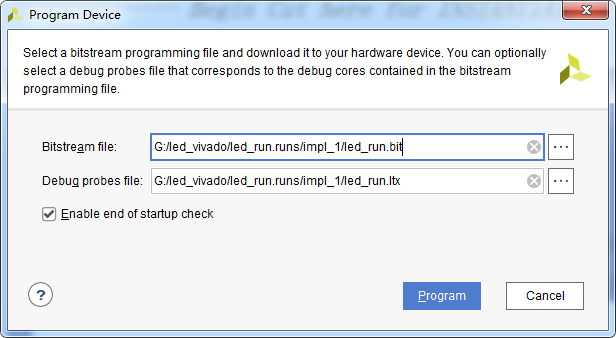

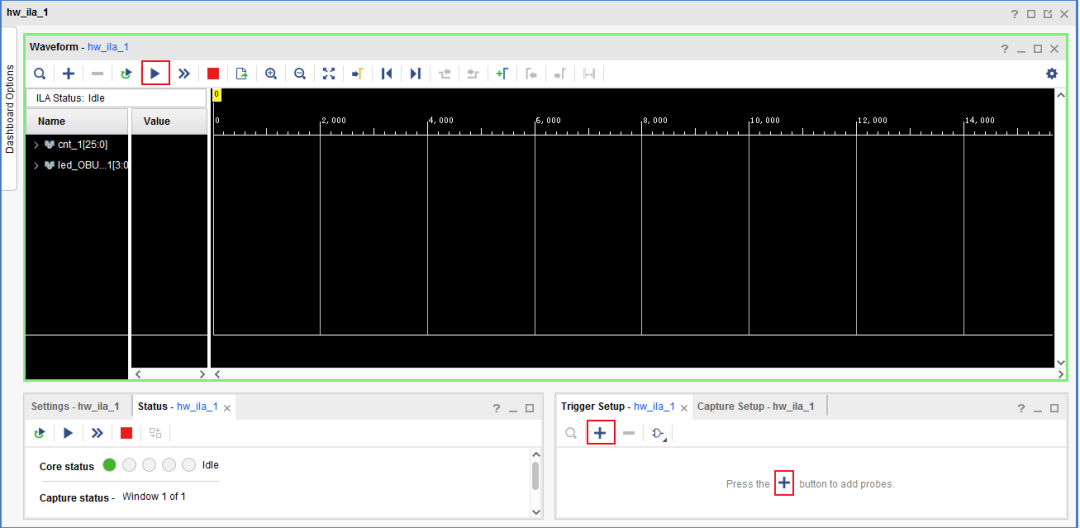

下板时,界面中出现两个文件。第一个文件为bit流文件。第二个为逻辑分析仪文件。直接点击program。下载完成之后会出现如下界面。

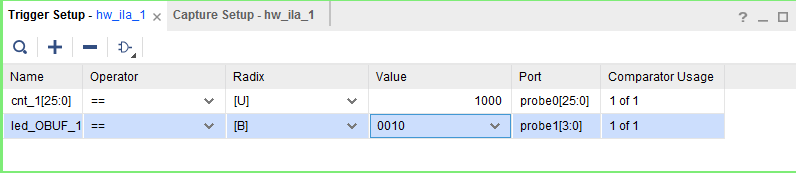

在开始观察波形之前,我们需要先在右下角小窗口里面设置触发信号。这个我们可以理解为我们想要观察的波形的位置。比如我们可以观察一下led为第二个灯亮,且计数器数到1000的位置,那么我们的设置如下图:

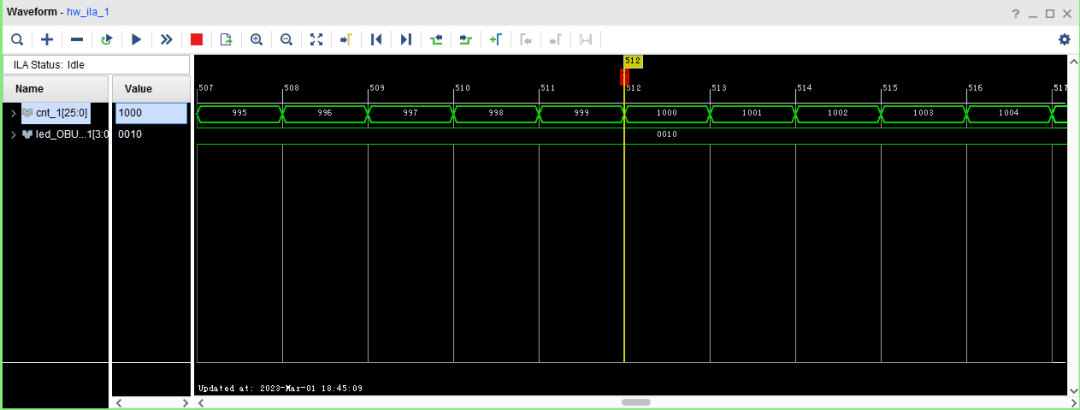

设置好之后,我们点击波形界面的三角形符号,进行触发,那么就可以观察到我们的波形了。

第二种方法:

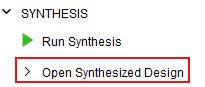

“网表插入调试探针流程”需要在综合后的网表中,将要进行调试观察的各个信号,标记“Mark_Debug”属性,然后通过“Setup Debug”向导来设置ILA IP核的参数,最后工具会根据参数来自动创建ILA IP核。我们点击“Flow Navigator”窗口中的“Open Synthesized Design”按钮,如下图所示:

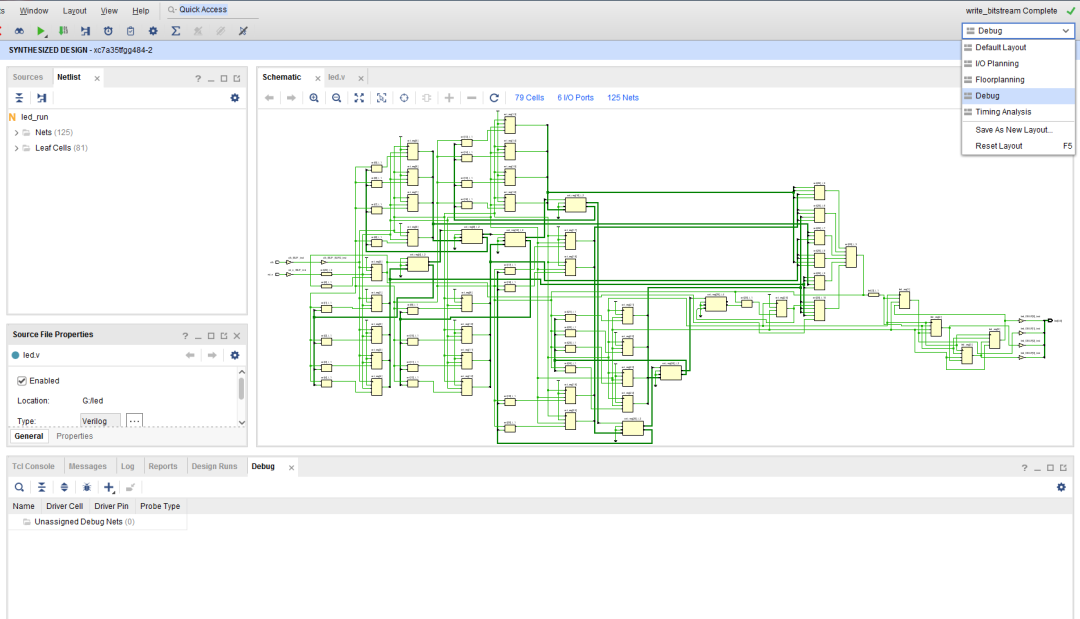

在综合后设计的窗口布局选择器中,我们选择“Debug”窗口布局,如下图所示:

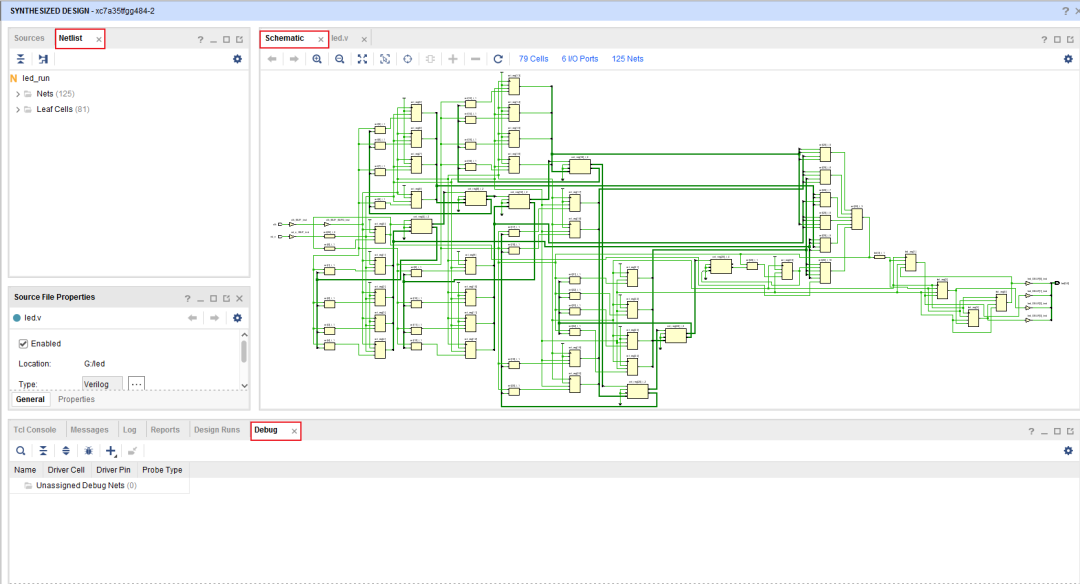

此时,Vivado打开了“Netlist”子窗口、“Schematic”子窗口以及“Debug”子窗口。其中,“Netlist”子窗口和“Schematic”子窗口都用于标记要进行观察的信号,“Debug”子窗口用于显示并设置ILA IP核的各个参数。如下图所示:

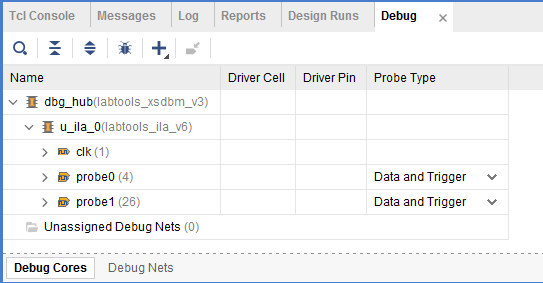

在“Debug”子窗口中,又包含两个选项卡“Debug Cores”和“Debug Nets”。这两个选项卡都用于显示所有的已标记为“Mark_Debug”的信号。不同之处在于,“Debug Cores”选项卡是一个更加以ILA IP核为中心的视图,所有已标记为“Mark_Debug”的信号并且已经被分配到ILA探针的信号都会被显示在各个ILA IP核的视图树下,已标记为“Mark_Debug”的信号但是还没有被分配到ILA探针的信号被显示在“Unassigned Debug Nets”下,当然也可以在其中查看和设置ILA IP核的各种属性和参数。“Debug Nets”选项卡仅显示已标记为“Mark_Debug”的信号,但不显示ILA IP核,所有已标记为“Mark_Debug”的信号并且已经被分配到ILA探针的信号都会被显示在“Assigned Debug Nets”下,已标记为“Mark_Debug”的信号但是还没有被分配到ILA探针的信号被显示在“Unassigned Debug Nets”下。

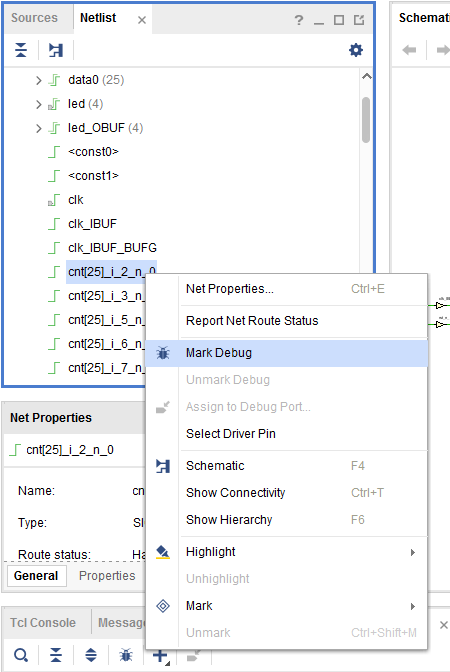

我们首先标记要进行观察的信号,以led信号为例,在“Netlist”子窗口中的“Nets”目录下,找到“led_OBUF”网络,右击该网络(此时右边的“Schematic”子窗口也会自动地高亮选择此网络,因为“Netlist”子窗口中的对象和“Schematic”子窗口中的对象,两者之间是交叉选择的),在弹出的菜单中心选择“Mark Debug”命令,如下图所示:

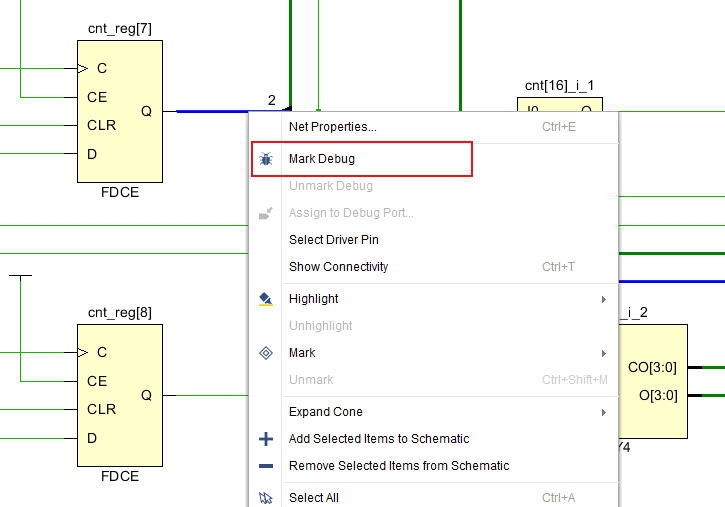

也可以在“Schematic”子窗口中选择网络,然后右键选择“Mark Debug”命令,如下图所示:

另外,也可以在HDL源代码中为想要观察的reg或wire信号添加“Mark Debug”属性,例如:(* mark_debug = “true” *)reg [25:0] cnt ; 其中“(* mark_debug = “true” *)”必须紧挨在变量声明的前面。这样,在综合完之后打开综合后的设计,counter信号就自动被标记了“Mark Debug”属性。此时在“Debug”子窗口的“Debug Nets”选项卡的“Unassigned Debug Nets”目录下就会出现我们刚刚标记的“led_OBUF”网络。

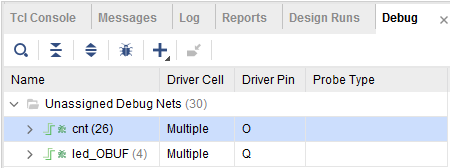

此时“Debug”子窗口的“Debug Nets”选项卡的“Unassigned Debug Nets”目录下就有了“led_OBUF”和“cnt”两个信号,如下图所示:

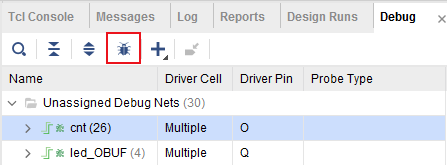

之后我们点击“Debug”子窗口中的“Setup Debug”按钮,如下图所示:

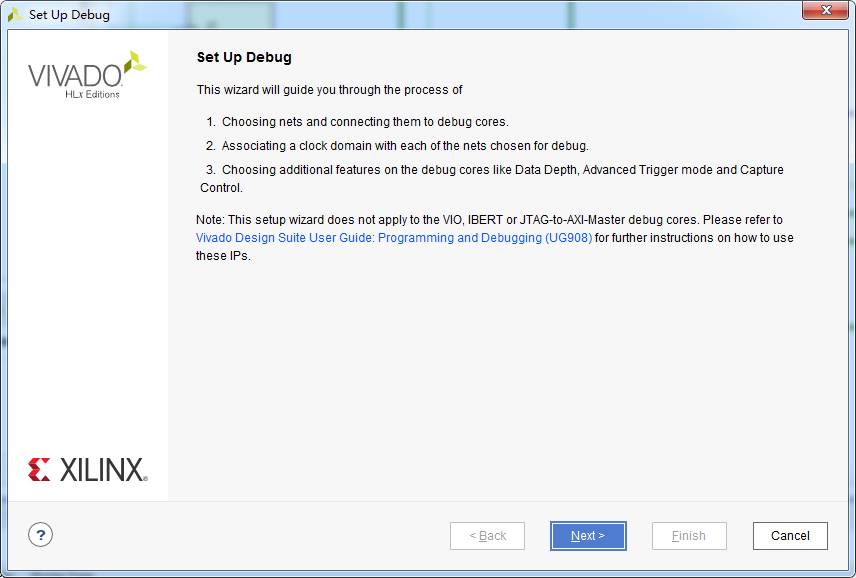

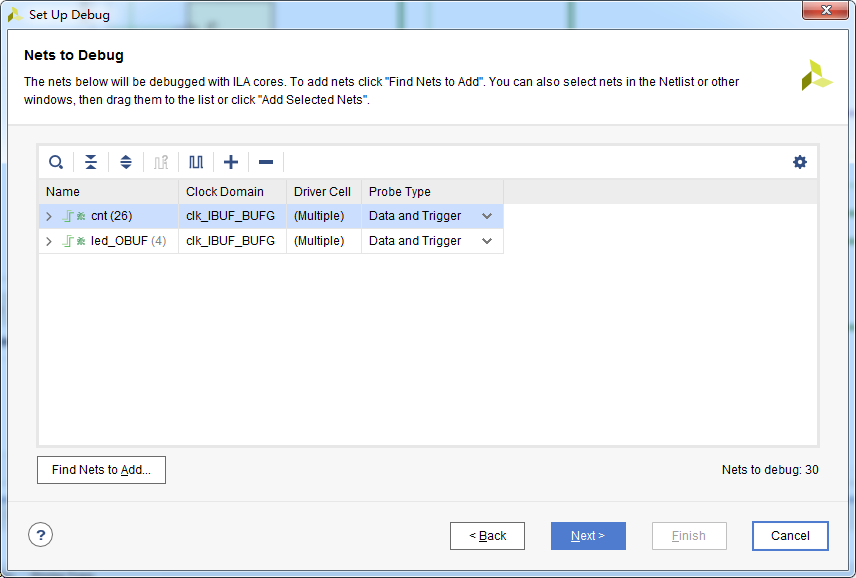

弹出“Setup Debug”向导,我们直接点击next,如下图所示:

接下来的页面是选择用于采样待测信号的时钟域,Vivado会自动识别出各个待测信号所属的时钟域并将其自动设定为其采样时钟,例如,我们刚刚添加的这“led_OBUF”和“cnt”两个信号就属于“sys_clk_IBUF”时钟域,并且Vivado也已经自动将“sys_clk_IBUF”时钟设置为了这两个信号的采样时钟,如下图所示:

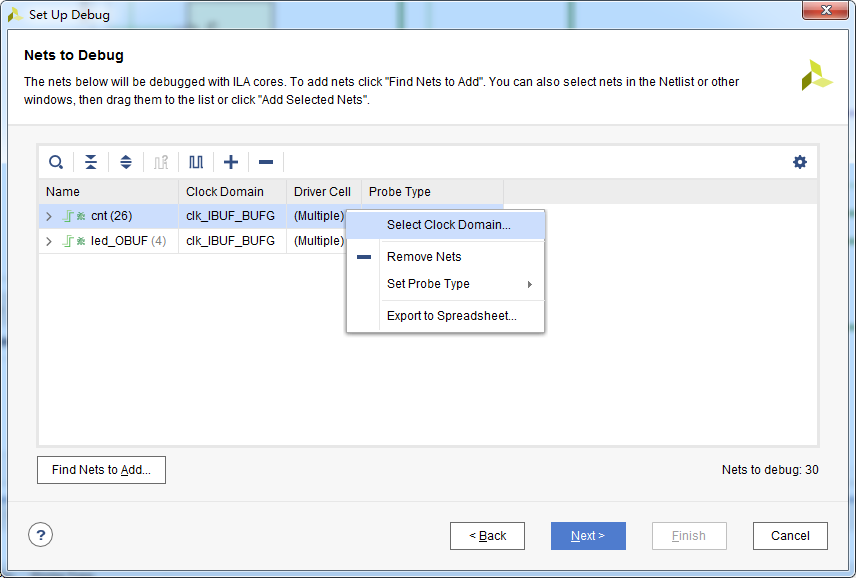

当然,用户也可以手动指定各个用于采样待测信号的时钟域,右击待测信号,选择“Select Clock Domain”,弹出“Select Clock Domain”窗口,如下面两个图所示:

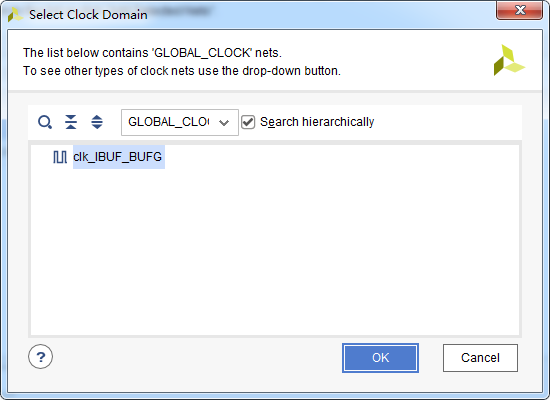

在“Select Clock Domain”窗口中就可以选择用于采样待测信号的时钟了。“Setup Debug”向导会为每个采样时钟生成一个单独的ILA IP核,由于本例程中只有一个时钟,所以这里最后只会生成一个ILA IP核。设置完采样时钟后,我们点击next,接下来的页面用于设置ILA IP核的全局设置,如下图所示:

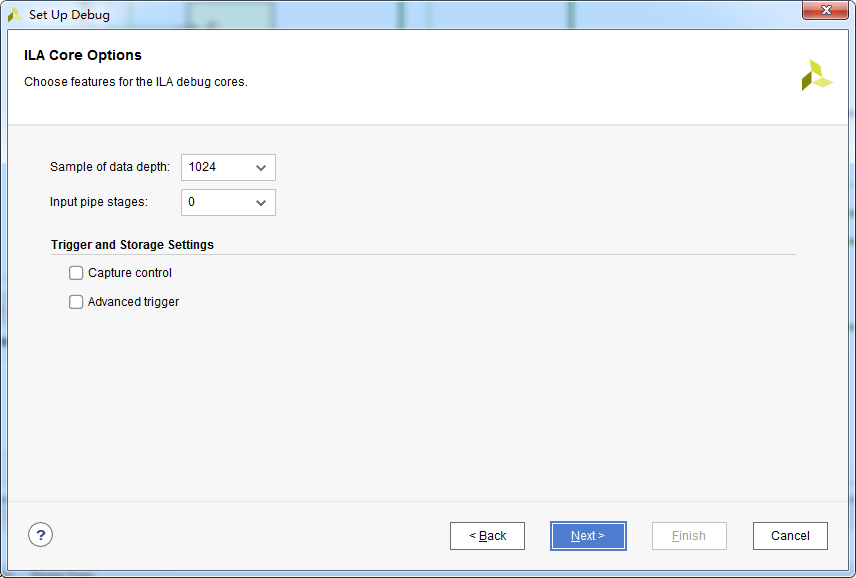

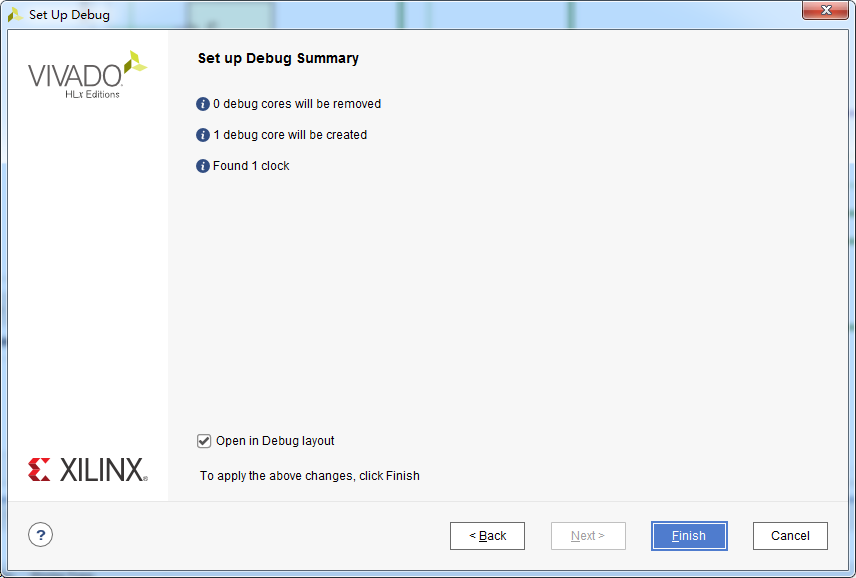

其中“Sample of data depth”用于设置采样深度,“Input pipe stages”用于设置待测信号和其采样时钟之间的同步级数。如果在上一个设置时钟域页面中,存在与其采样时钟之间是异步的待测信号,则为了避免亚稳态,此数值最好不要低于2。由于本例中的两个待测信号的其采样时钟是同步的,所以可以设置为0。我们点击next,就进入了最后的概览页面,确认无误后直接点击finish即可,如下图所示:

在“Debug”子窗口中的“Debug Cores”选项卡中,可以看到Vivado已经添加了ILA IP核,并且“Unassigned Debug Nets”目录下已经没有未被分配的信号了,如下图所示:

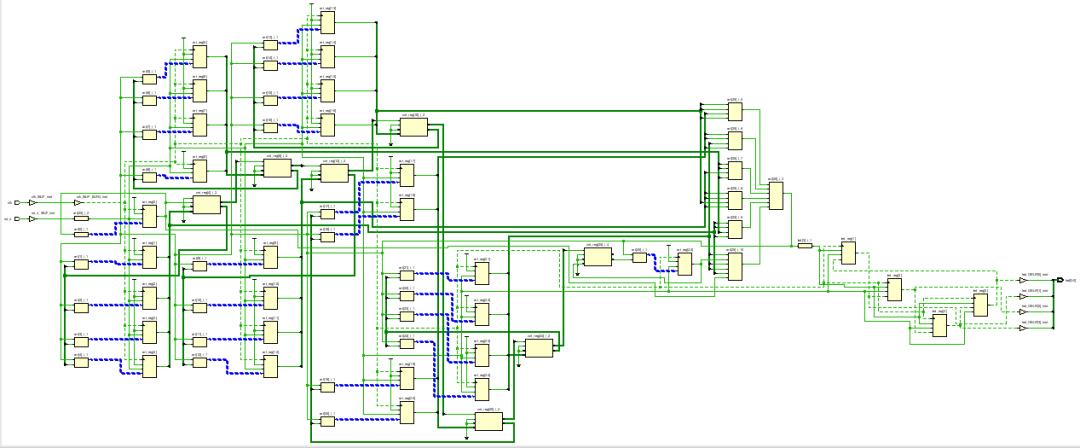

网表中被标记为Mark Debug的信号也变为了虚线,以表示其完成了ILA IP核的分配,如下图所示:

前面我们提到过,在“网表插入调试探针流程”中,用户设置的调试信息会以Tcl XDC调试命令的形式保存到XDC约束文件中,在实现阶段,Vivado会读取这些XDC调试命令,并在布局布线时加入这些ILA IP核。此时,我们所做出的所有的更改和设置,都还只是停留在电脑内存中,我们需要将其保存在硬盘的XDC约束文件中,点击工具栏中的保存按钮,如下图所示:

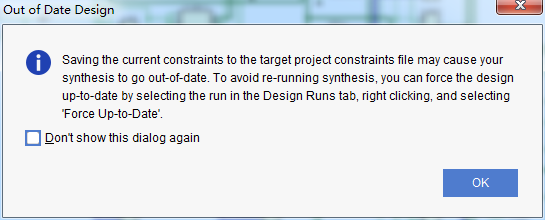

在出现的对话框中直接点击OK,如下图所示:

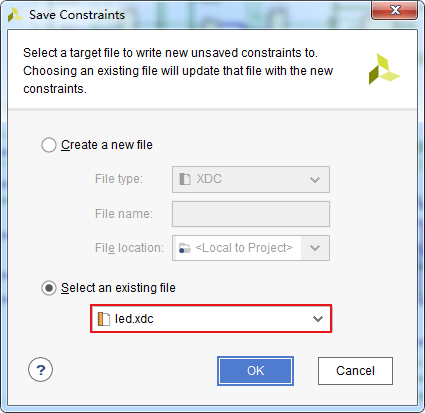

弹出的“Save Constraints”窗口中,用于询问用户将约束保存在哪个XDC约束文件中,本例的工程中只有一个XDC约束文件,如下图所示,我们直接点击OK即可:

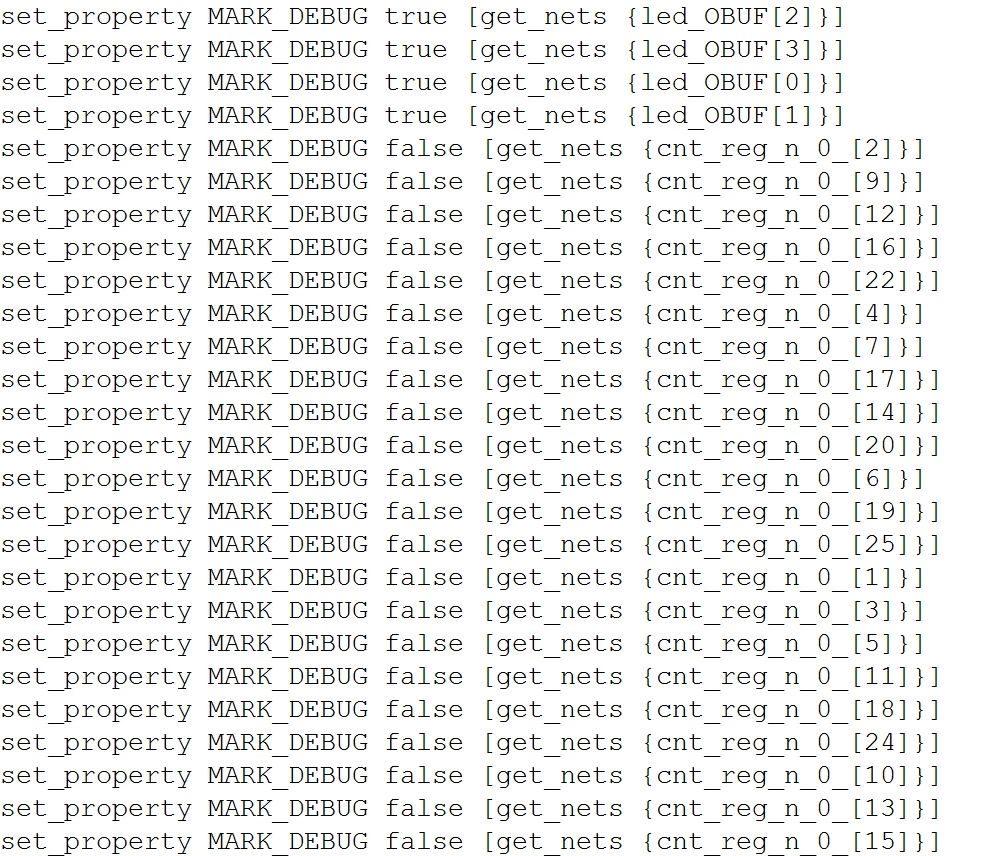

此时,我们打开led_twinkle.xdc,就会看到在用户约束的下面,Vivado自动写入了用于debug的约束,如下图所示:

在实现阶段,Vivado会读取这些约束,并按照这些命令的参数来自动地在布局布线时加入ILA IP核。至此,我们就成功地使用“网表插入调试探针流程”将ILA IP核添加到了设计中。接下来就可以将实现设计并生成比特流,最后将比特流下载到FPGA中,以对信号进行在线观察,这一部分内容在上面第一种方法里面已经介绍过了,在此不再重复介绍。

- End -

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+公司/学校+岗位/专业进群

FPGA技术江湖QQ交流群

备注姓名+公司/学校+岗位/专业进群