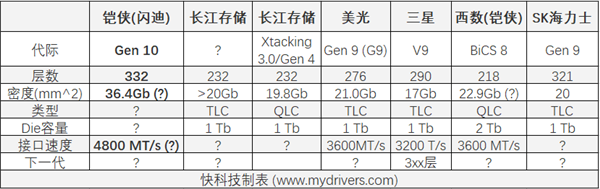

铠侠宣布了与闪迪联合开发的第10代BiCS 3D NAND闪存,无论堆叠层数、存储密度、接口速率性能,都达到了新的高度。

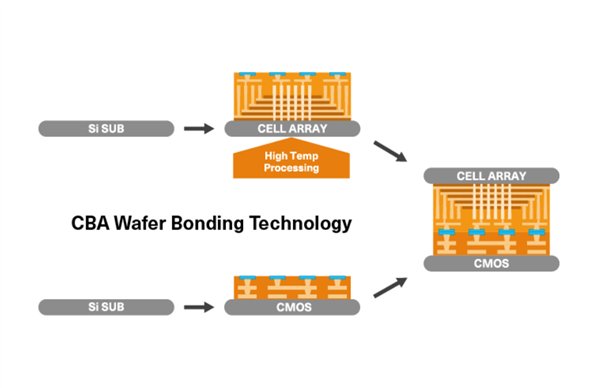

铠侠新闪存采用CBA双晶圆键合技术,分别制造CMOS控制电路、NAND存储阵列,然后键合在一起,其实就是学习的长江存储的Xtacking晶栈架构。

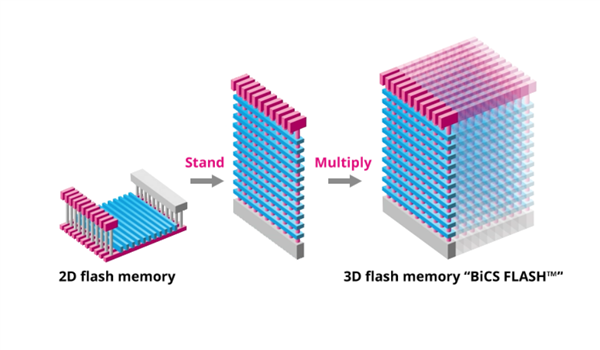

3D堆叠层数达到空前的332层,对比第8代的218层增加了多达38%,也超过了SK海力士的321层、三星的290层、美光的276层、西数的218层。

铠侠的目标,是在2027年造出1000层堆叠的3D闪存。

得益于更多层的堆叠,存储密度号称提升59%,算下来约为每平方毫米36.4Gb,同样远远领先友商,西数也只做到了每平方毫米22.9Gb,SK海力士更是不过每平方毫米20Gb。

不过,铠侠暂未公布具体的闪存类型(TLC/QLC),以及单Die容量。

新闪存同时支持Toggle DDR 6.0接口规范,传输速度高达4800MT/s,比前代提升33%,同样是新高,超过了美光、西数的3600MT/s。

此外,铠侠这次还加入了PI-LTT低功耗技术,输入功耗降低10%,输出功耗降低34%,可以更好地满足AI技术需求。

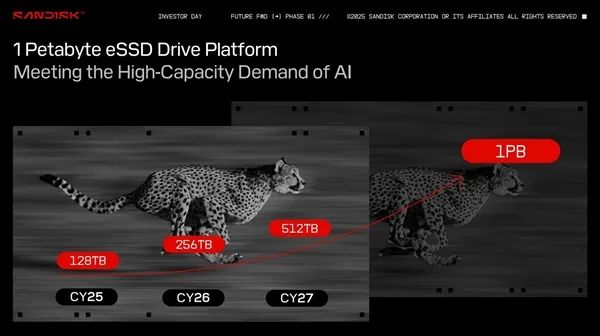

在近日的投资者日活动上,闪迪宣布了其开发容量高达PB级固态硬盘的计划,不过遗憾的是路线图中并未公布具体的时间。

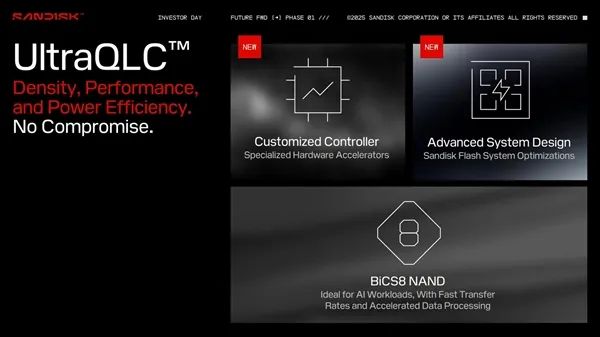

这一目标将通过其UltraQLC技术实现,UltraQLC并非一种新型内存,而是闪迪自家研发的BICS 8 QLC 3D NAND、一个高端专用控制器(支持64个NAND通道)和固件的结合体。

该平台的核心在于其定制的控制器,它融合了专用硬件加速器,将关键存储任务从固件中分担出去,从而降低延迟、提高带宽,并增强在超大规模存储环境中的可靠性。

此外,该控制器还会根据工作负载自动调整功耗,确保最佳的能效。

UltraQLC固态硬盘将采用2Tb NAND内存IC来实现128TB的存储容量,尽管64通道的控制器理论上能支持更高容量,但这样做会影响性能。

展望未来,闪迪预计将开发更高容量的NAND设备,这将使SSD的容量扩展到256TB、512TB,并在未来几年内达到1PB的目标。

闪迪的工程与产品管理负责人表示:“UltraQLC是基于我们几十年的经验和当前的学习,专门为现代数据基础设施打造的技术,完全没有在密度、性能和能效上作出妥协。”

传统数据存储一直依赖于在“开”、“关”状态之间切换,但存储这些二进制状态的元件物理大小,却限制了设备中能够容纳的信息量。

近日,芝加哥大学PME团队研究人员发表研究成果显示,他们成功在仅1毫米大小的晶体内储存了数TB的数据,为今后储存解决方案取得突破性的里程碑。

据悉,研究人员通过利用晶体内的单原子缺陷来表示数据存储的二进制1和0来实现这一目标。

这项研究发表于《纳米光子学》(Nanophotonics)期刊,探讨了原子尺度的晶体缺陷(crystal defect)如何起到个别储存单元的作用,以及如何将量子方法与传统计算原理相结合的过程。

研究人员认为,这项突破可能重新定义数据储存的极限,为传统计算领域带来超轻薄、超大容量的储存解决方案。

该研究论文第一作者、博士后研究员Leonardo Fran?a表示:“我们找到了能将应用于辐射剂量测定的固态物理学与专注于量子领域的研究团队相结合的方法。”

在助理教授Tian Zhong的领导下,研究团队透过将稀土离子引入晶体中,具体而言就是将镨(Praseodymium)离子掺杂到氧化钇(Yttrium Oxide)晶体内,从而开发出这种创新的储存方法。他们认为,由于稀土元素具备多样化的光学特性,这种方法可以扩展至其他材料。

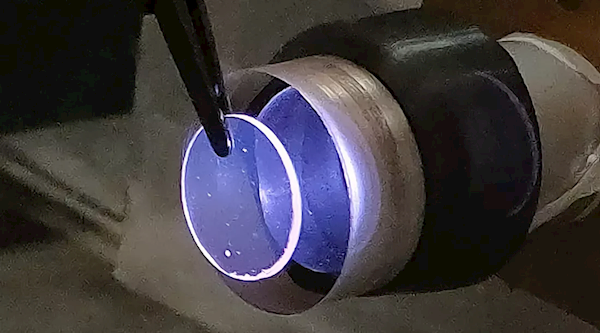

该记忆系统通过能让稀土离子通电以释放电子的紫外激光加以启动,这些电子随后被困在晶体内的天然缺陷中。

研究人员通过控制这些缺陷的电荷状态,有效地构建出一套二进制系统,其中带电缺陷代表1,不带电缺陷代表0。

过去,晶体缺陷曾在有关量子运算的探索性研究中做为潜在量子位(qubit)。如今,芝加哥大学PME团队更进一步发现如何将其运用在传统存储应用里。