点击上方名片关注了解更多

点击上方名片关注了解更多

大家好,我是王工。

最近想要自己鼓捣点东西出来,设想的是先做好方案,画好原理图和PCB,然后在嘉立创打样回来焊接调试,在做方案的时候才意识到,可能会被DDR给难住。因为平时只需要设计方案和原理图,公司有layout工程师负责画板,我们不用自己操作,最多参加一下评审。这玩意儿看着简单,但真要自己去动手的时候,可能才知道没有想象中那么容易。

DDR基础

DDR发展历程

DDR的PCB设计

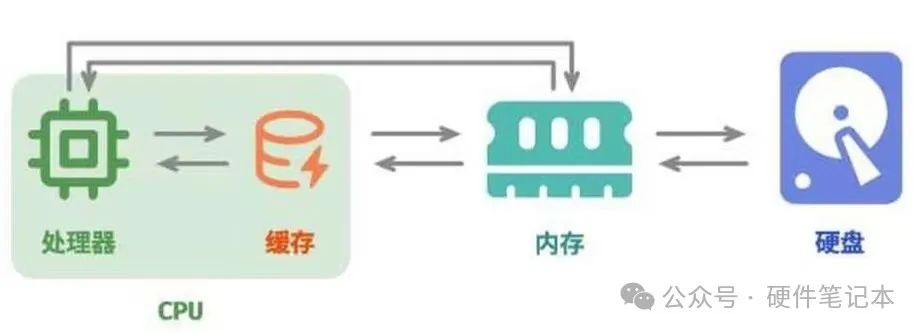

DDR主要起个什么作用呢?它是作为 CPU 和存储设备(如硬盘)之间的高速数据缓冲区。核心功能是临时存储正在运行的程序和数据,以便 CPU 能够快速访问和处理这些信息。

因为硬盘的读写速度较慢,无法直接与 CPU 高效通信。

DDR是存储器的一种,关于存储器的一些基础知识,大家看看如下链接:

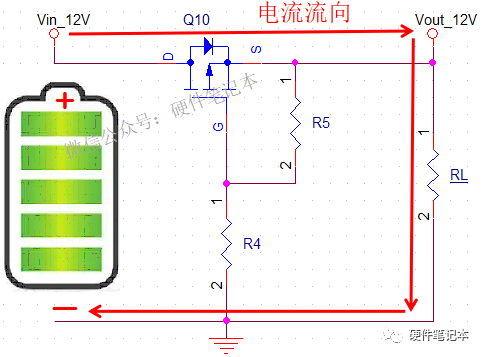

电源DDR硬件设计技巧

当然这都是很基础的知识,也只是关于DDR的冰山一角。

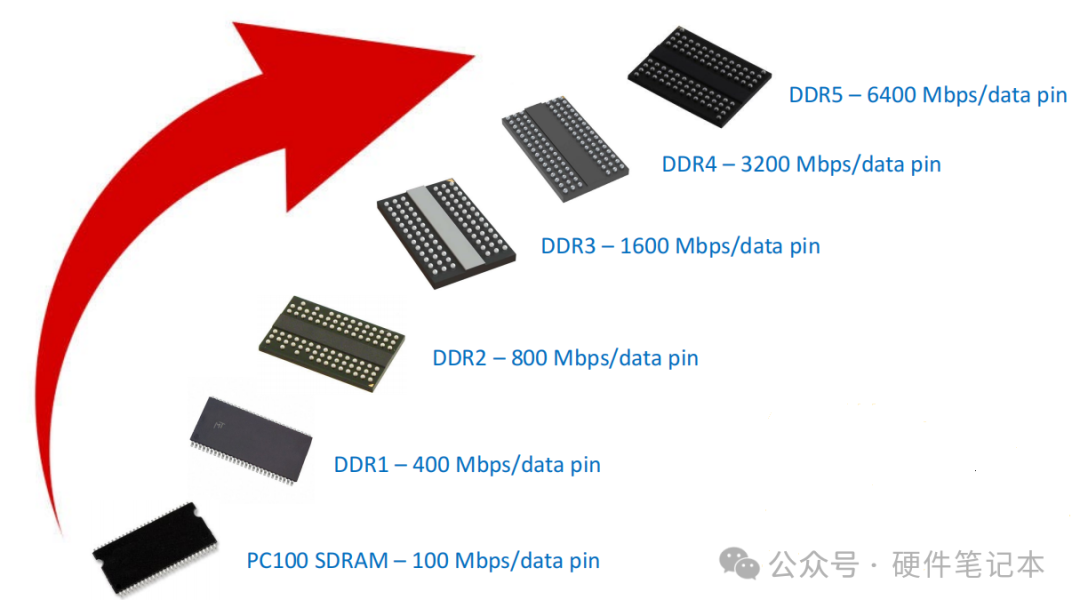

DDR的版本迭代经历过SDRAM、DDR1、DDR2、DDR3、DDR4和DDR5,预计DDR6将在2026年上市。

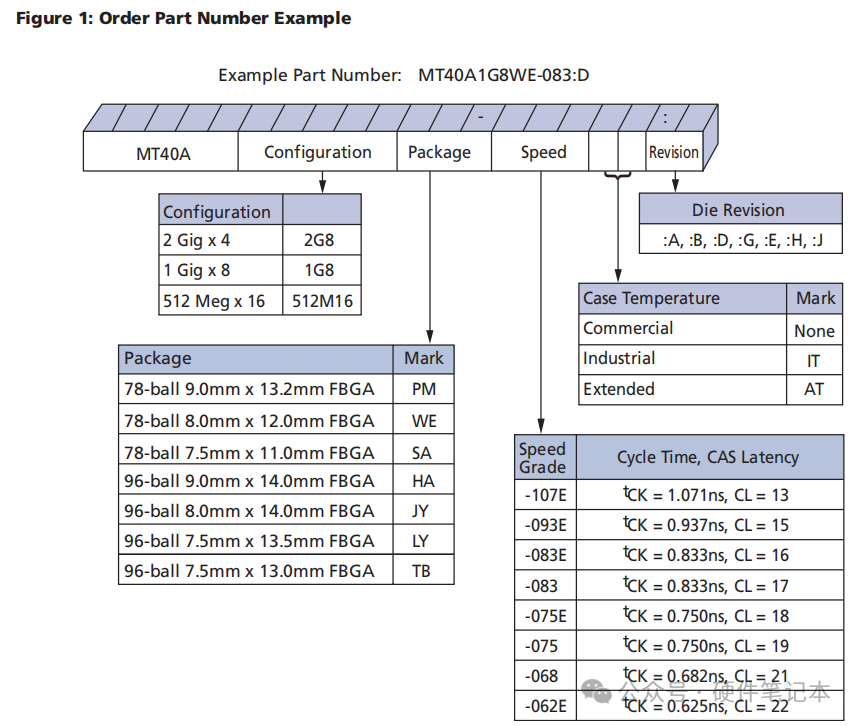

以镁光型号为MT40A1G8WE-083:D为例

MT:代表制造商 Micron Technology。

40A:表示产品系列或技术类型,指 DDR4 内存。

1G:表示内存容量为 1 Gigabit (Gb),即 128 Megabytes (MB)。

8:表示内存位宽为 8 bits。

WE:表示特定的封装类型。

083:表示速度等级为 833 MHz(等效于 DDR4-2666)。

:D :可能代表特定的温度范围或工业级应用。

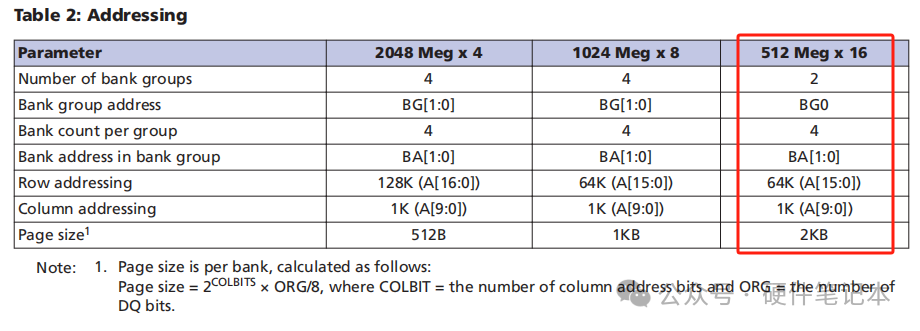

列地址线为10,A[9:0];

容量=16 x 2^(1bank选组线+2bank选择线+16行地址线+10行地址线)

容量=16 x 2^(1+2+16+10)

容量=16 x 2^29

容量=8,589,934,592b(单位换算b,Kb,Mb,Gb)

容量=8Gb(除以3次1024,注意b代表bit,而不是byte)

容量=1024MB(8Gb/8)

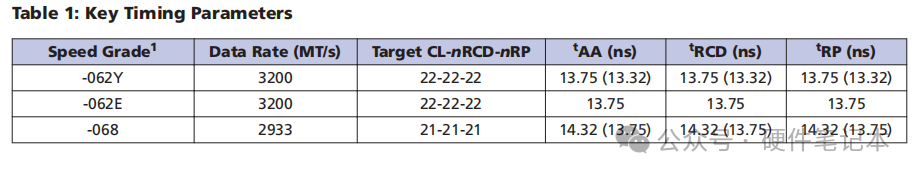

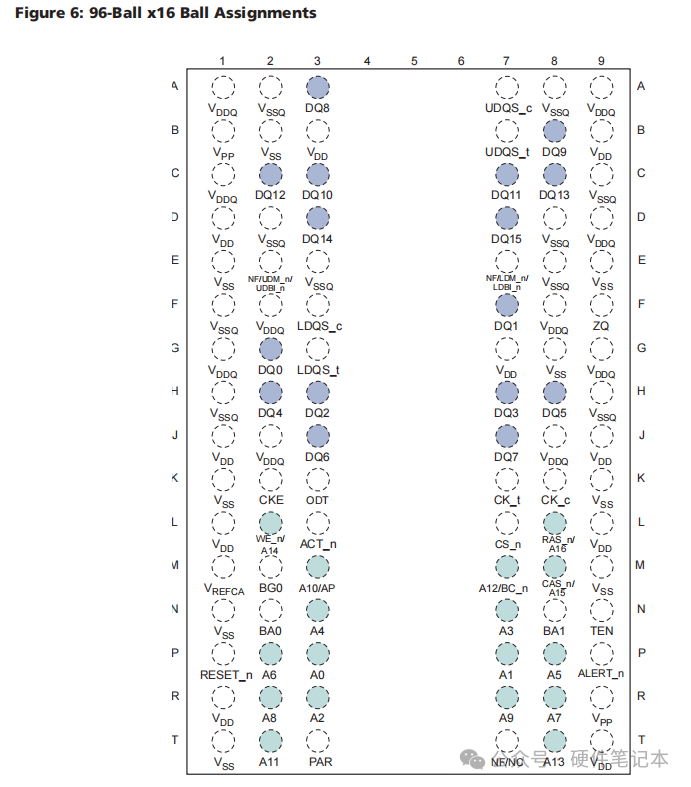

例如,速度为2666 MT/s的内存模块在速度等级-075E下的时序参数为18-18-18,对应的访问时间、行地址到列地址延迟和行预充电时间均为13.50纳秒。

1.Speed Grade:内存模块的速度等级。

2.Data Rate (MT/s):内存模块的数据传输速率,单位为百万次传输每秒(MT/s)。

3.Target CL-nRCD-nRP:目标时序参数,包括CAS延迟(CL)、行地址到列地址延迟(RCD)和行预充电时间(RP)。

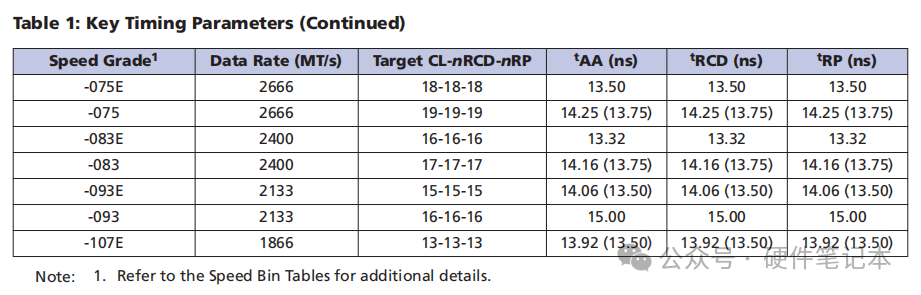

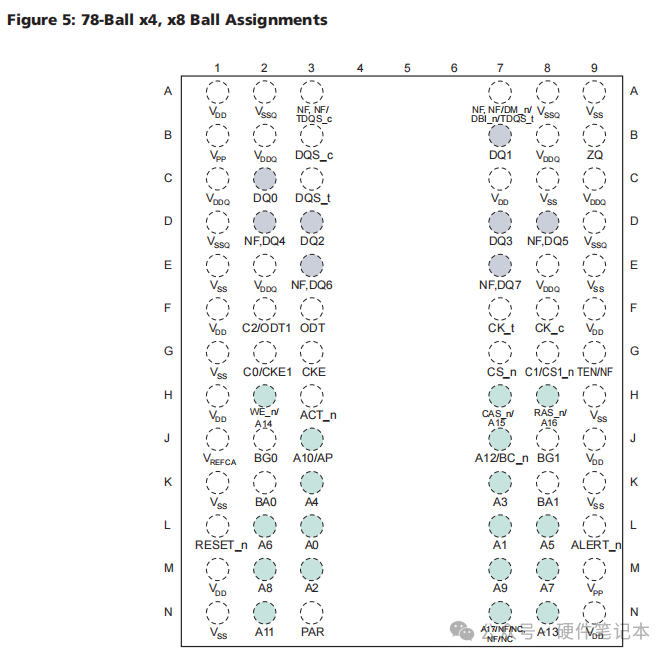

2.4 DDR4的封装

尺寸:13.2mm X9mm

尺寸:12mm X8mm

尺寸:11mmX7.5mm

尺寸:14mmX9mm

尺寸:14mmX8mm

尺寸:13.5mm X7.5mm

尺寸:13mmX 7.5mm

当然,DDR还有很多其它细节,包括选型,一些重要的电源线,数据线,地址线,控制线和时钟信号等,大家感兴趣可以自己下来了解,下面再说说DDR4的PCB设计。

DDR4布局

1、DDR在布局的时候一定要尽可能的靠近CPU,阻容元件放置在DDR背面,特别是滤波电容要尽量靠近管脚,走线要尽量短,电源线尽量粗,必须要配置比较大的储能电容。

可选用嘉立创的阻抗计算神器,链接如下:

https://tools.jlc.com/jlcTools/index.html#/impedanceCalculatenew

https://www.jlc.com/portal/q7i37381.html

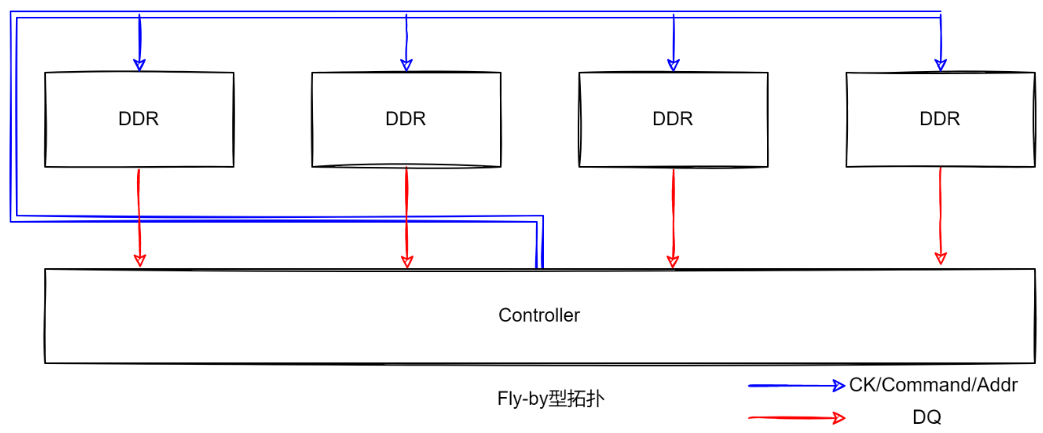

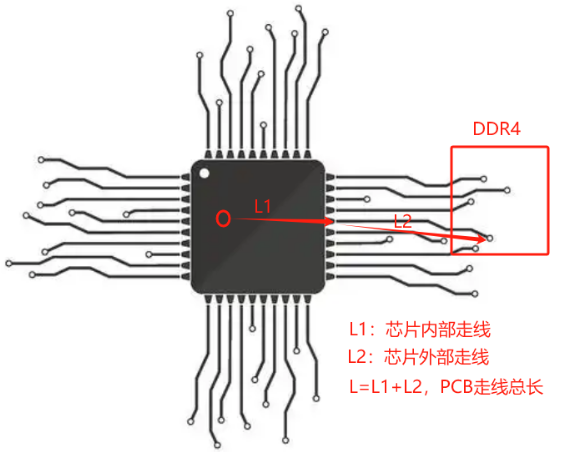

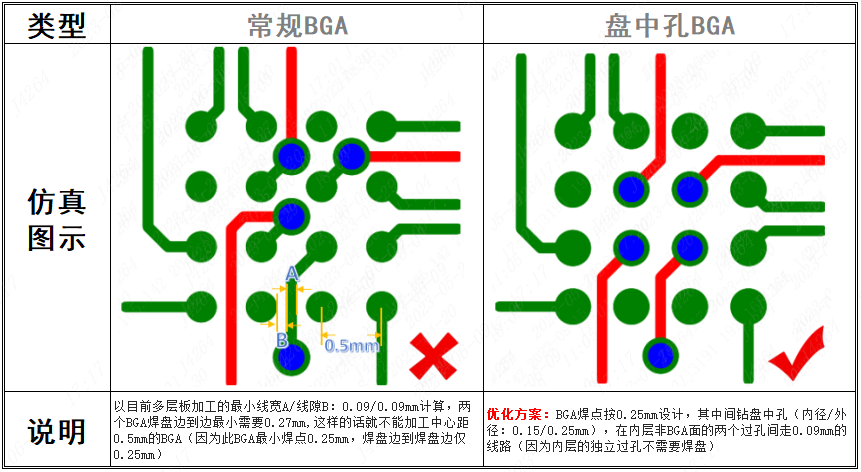

2、DDR4的信号可以分为4组数据线和2组地址线,数据线最好同组同层(即:同一组的信号必须要走线在同一层),地址线一般很难做到同组同层,这一点也没有硬性要求。先把数据线走通,对于同一组信号内的走线,layout要做等长处理,最好控制在10~20mil以内(数据走线),对于地址信号走线要求就没那么高,一般50mil以内就可以了。

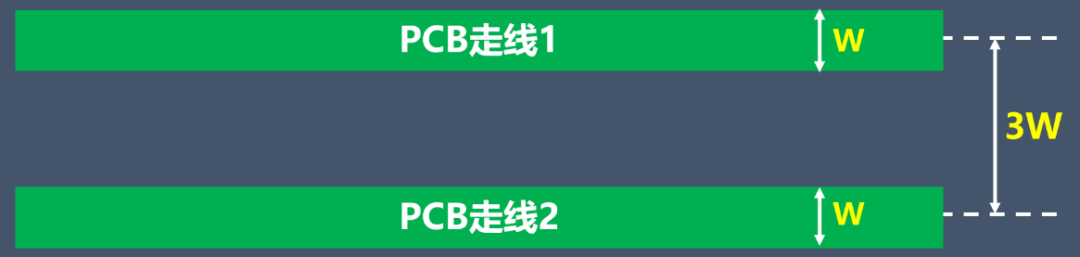

4、做等长的时候要注意一个3w原则,相邻的信号线,中心间距大于线宽的3倍,还需要对敏感的差分线做包地处理。

以上描述看起来很简单,实际操作会更复杂,多熟悉几次应该就好了。

还有一些相关要求,可参考DDR4的走线设计要求在JEDEC标准中有详细的规范

https://blog.csdn.net/weixin_43199439/article/details/142467998

好了,PCB设计的重点就讲这些了。

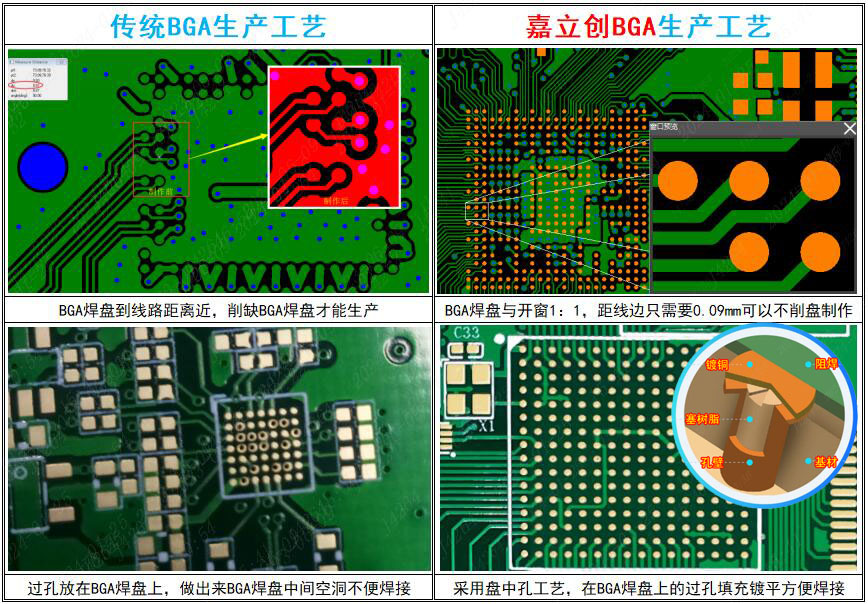

原理图和PCB都搞定了,那么下一步就要打样回来调试,板厂我首选嘉立创,主要是平时一直都是在他家打板,没出过啥问题,他们家的工艺文件规范,服务态度好,每次打板都会建一个小群,几个人服务一个人那种,真的有体会到上帝就是顾客的那种感觉,有问题可以及时沟通,效率很高。

好了,今天的分享就到这里,咱们下次再见。

声明:

推荐阅读▼

电路设计-电路分析

EMC相关文章

电子元器件