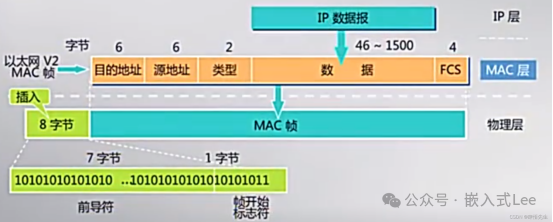

前面我们在”基于DWC_ether_qos的以太网驱动开发”系列文章中分享了驱动开发调试过程。其中最重要的就是要先调通收发数据流。而MAC和PHY之间数据流是重要的一环,其通过GMII(RGMII)接口通讯,该部分是数字接口,我们可以通过逻辑分析仪来监控RGMII接口的信号,可以知道MAC和PHY之间数据流是否正确。比如假设发送数据对方收不到,那么可以看RGMII的TX是否有正确数据发出,可以确定是MAC这端问题还是PHY那一端问题,然后进一步分析。这一篇就分享实践过程。

既然是对RGMII接口进行监控分析,那么就需要先来了解一些RGMII接口的基本信息。

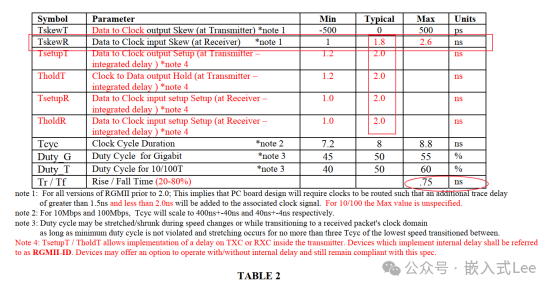

参考规格书《Reduced Gigabit Media Independent Interface(RGMII) 4/1/2002 Version 2.0》只有9页内容较少,可很快地看完。以下是总结的重要信息。

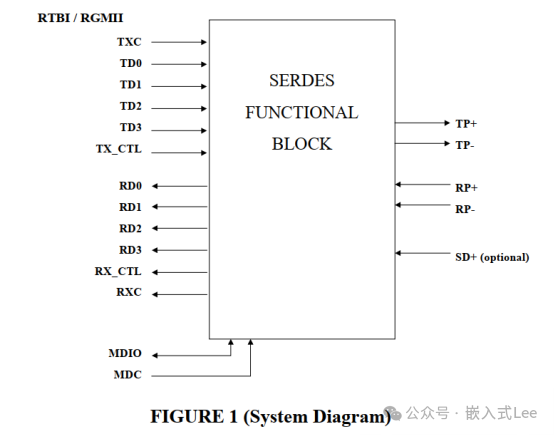

RGMII旨在成为IEEE802.3u MII、IEEE802.3z GMII和TBI的低引脚替代。其主要目标是以经济高效和技术独立的方式将MAC和PHY互连所需的引脚数量从最多28个引脚(TBI)减少到12个引脚(TX RX各6个,4个数据加一个时钟一个控制)。其实现方式是通过双边沿传输数据和控制信号来减半数据引脚和控制引脚,即数据在双边沿传输,控制信号在双边沿都有意义。对于千兆,时钟为125MHz双边沿就是250MHz,4个引脚就是1000MHz。

信号

信号名字 | RGMII | 描述 |

TXC | MAC | MAC端发送时钟 125Mhz、25Mhz或2.5Mhz+-50ppm。 对于1000M网是125MHz. |

TD[3:0] | MAC | MAC端发送 TXC的上升沿传输bit[3:0] 下降沿传输bit[7:4] |

TX_CTL | MAC | MAC端发送 在TXC的上升沿表示数据使能TXEN,下降沿表示数据错误信息TXERR |

RXC | PHY | PHY端驱动的时钟 125Mhz、25Mhz或2.5Mhz+-50ppm。 对于1000M网是125MHz. |

RD[3:0] | PHY | PHY端发送 RXC的上升沿传输bit[3:0] 下降沿传输bit[7:4] |

RX_CTL | PHY | PHY端发送 在RXC的上升沿表示数据有效TXDV,下降沿表示数据错误信息RXERR |

总结一下就是上升沿传输数据低4位,下降沿传输数据高4位

CTL在CLK上升沿时表示有数据,CLK下降沿时代表ERR(具体怎么代表见后面)

信号采用正逻辑,即高有效。

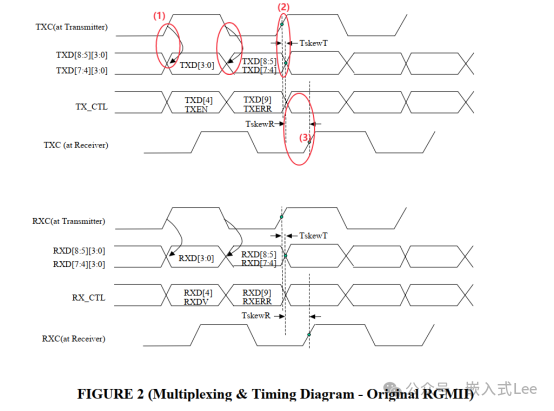

参考如下图三个关键位置

(1)发送端在CLK的上升沿和下降沿发出数据, 但是硬件上数据和时钟走的不同的path还是有一定偏差的即TskewT。然后经过PCB等到了接收端,CLK和数据偏差变为了TskewR。

理论上TskewR要刚好是2nS(即对于接收端看到CLK边沿在数据中间,一个周期是1/125MHz=8ns,DDR所以上升沿和下降沿传输数据都只有4ns)将是最理想状态,即建立和保持时间都是2ns,注意这里是在接收端角度而言。

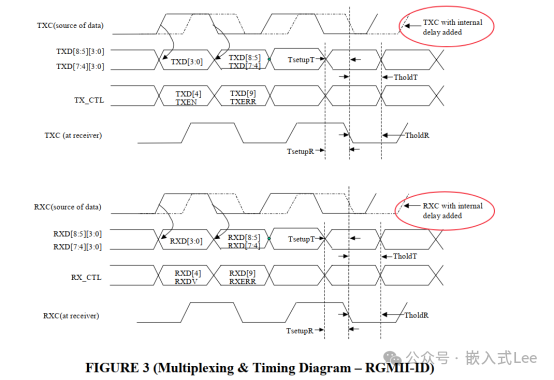

所以为了达到上述建立和保持时间的理想状态,一般芯片内部都可对CLK进行delay调整,如下图的RGMII-ID,ID即Internal delay。如下图所示意,理想状态是人为的将CLK往后delay 2ns使得CLK在数据中间。但是实际上肯定不是delay正好2ns,因为PCB走线和其他path路径影响综合,CLK可能超前也可能滞后数据任意时间,但是不管怎样只要delay的范围能到1个CLK周期就能覆盖所有的偏移,不断调整delay得到一个可以工作的delay范围取中间值即可。

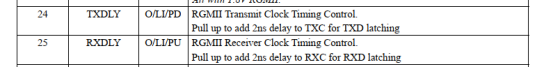

在PHY芯片那边一般有个电阻可配置使能内部2nS的delay,不能微调,所以一般还需要结合主控这边的微调达到最优状态。

比如RTL8211F的引脚24和25,上拉即使能内部的2ns的delay。

最最重点关注TskewR即站在接收端理想状态是CLK边沿在数据的中间,使得保持和建立时间都是2ns。同时周期准确性稳定性,占空比也重要,Tr/Tf也要关注。

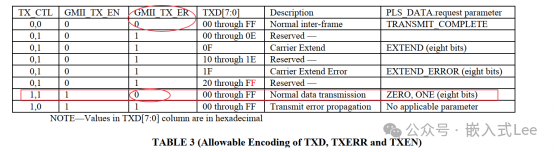

前面提到了的CLK的下降沿表示ERR信息。具体定义如下

其中TX_EN和RX_DV是上升沿的值,TX_ER,RX_ER是下降沿的值。

简单的说就是上升沿和下降沿保持一致时是五错误,不一致时有错误,即XOR操作。

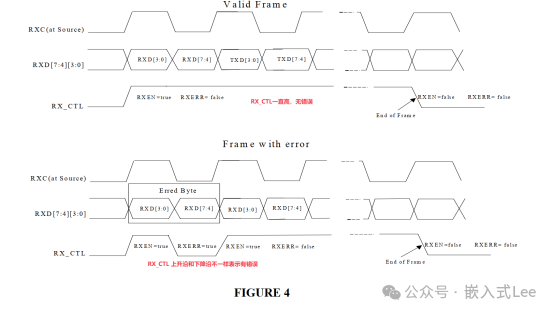

所以无错误传输数据时TX_CTL和RX_CTL一直是高。

TXERR <= GMII_TX_ER (XOR) GMII_TX_EN

RXERR <= GMII_RX_ER (XOR) GMII_RX_DV

如下所示,TX_CTL在CLK的上升沿下降沿一样时无错误,其他情况都是有错误,TX的编码如下

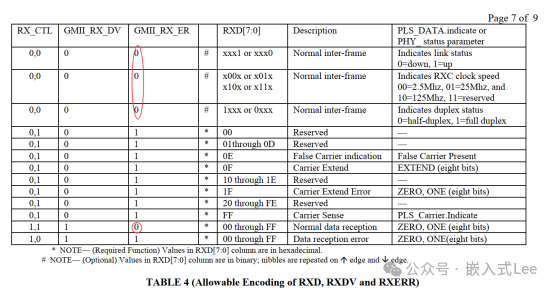

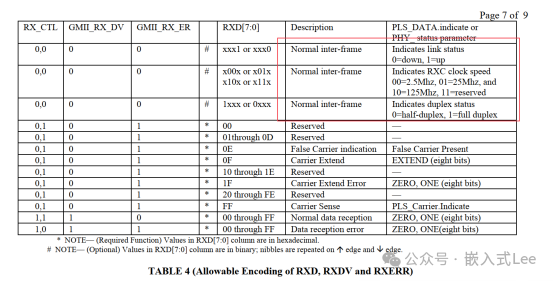

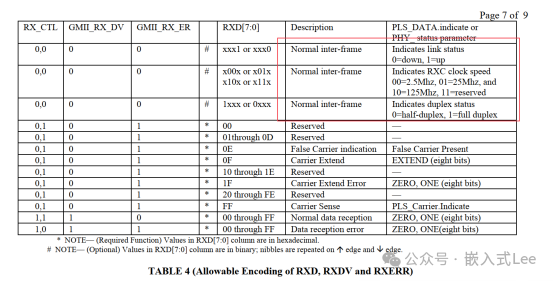

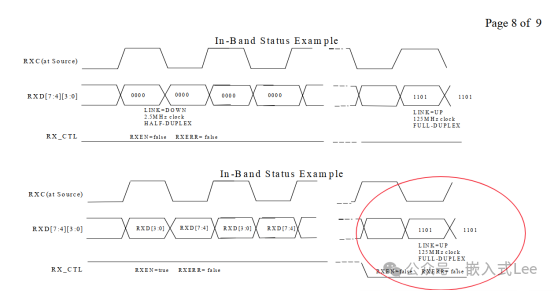

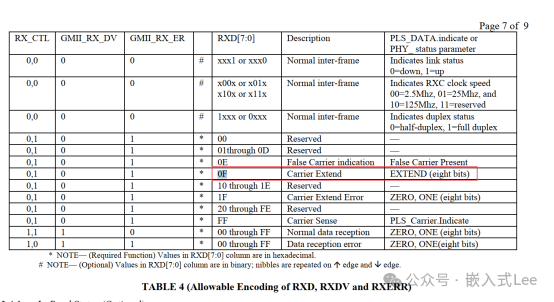

RX的编码如下

可选

为了检测PHY的链路状态、速度和双工模式,帧间信号Normal inter-frame将被放置在RXD[3:0]信号上,如下所示。当不存在正常数据、数据错误、载波扩展、载波侦听或假载波时,应指示PHY的状态。当链路状态关闭时,PHY速度和双工由PHY的内部设置定义。

要求

CRS由RXDV为有效

或者RXDV为无效、RXERR为有效、同时RXD[7:0]为FF的情况

或者上表中定义的Carrier Extend, Carrier Extend Error or False Carrier的情况表示。

Carrier Extend, Carrier Extend Error仅适用于千兆速度。

MAC通过在TXEN为有效同时检测到CRS或RXDV为有效时,检测到冲突。TXEN为有效时,PHY不会判断为CRS。

如下如表示链接状态

1101 表示up 125m full-duplex

Bit0 0:down 1:up

Bit[2:1] 2.5M,01=25M,10=125M

Bit3 0-half-duplex 1=full duplex

如下图表示Carrier Extend

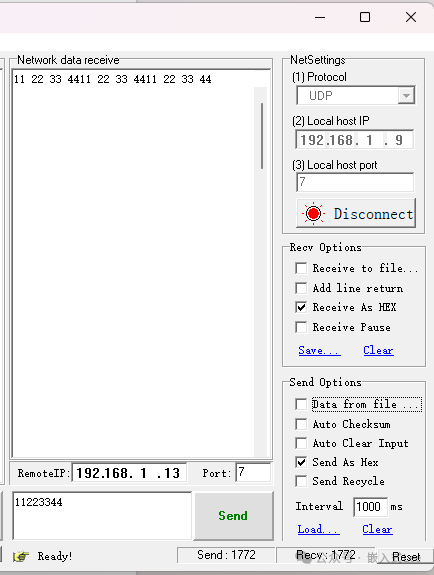

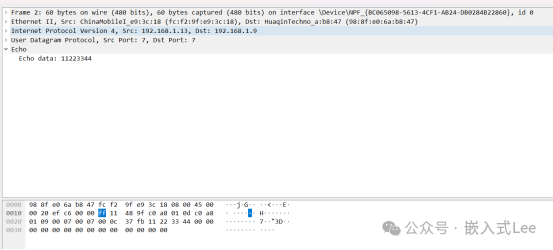

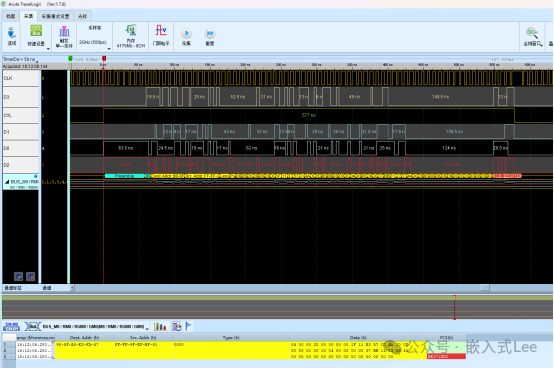

我这里使用逻辑分析仪Acute TravelLogic Analyzer最高采样率2GHz,即对应0.5nS,半个周期4ns也有8个点,可以比较好的抓取信号并解析。

电脑发送UDP包内容是11223344,板子收到包原样返回,抓取返回的包

逻辑分析仪抓TX数据时最好芯片内部TXC加delay,类似的抓RX数据时PHY加delay。这样逻辑分析抓到的数据才是有满足条件的建立和保持时间方便解析。

逻辑分析仪抓取的包如下

注意逻辑分析仪的接入本身可能对信号产生干扰,可能导致逻辑分析抓到的数据并不对,但是至少可以看到帧的各部分是否有。

对照协议就可可以分析数据了比如前导7个0xAA加一个0xAB,数据部分,FCS部分。

1.收发不到数据,先示波器查看TXC和RXC是否有,频率是否正确稳定。 然后看TX_CTL和RX_CTL是否有拉高。只要有CLK和TX_CTL则一定会有数据,哪怕是错误数据,此时就可以通过交换机监控端口看到至少有错误包,这一步完成了再继续调整delay。

调试RGMII的最关键一步就是delay的调整,即调整CLK到数据的中间,可以先使能PHY那边的2ns,delay。然后再微调主控这边的delay。遍历取一个中间最优值。

2.能发短包,不能发长包

确认时钟频率是否正确。比如时钟频率大于或小于125MHz,在发长包时bit累计偏差会导致后面的bit错位。

RGMII的调试比较简单,重点是关注TXC和RXC的delay调整,以及信号的确认。