----追光逐电 光引未来----

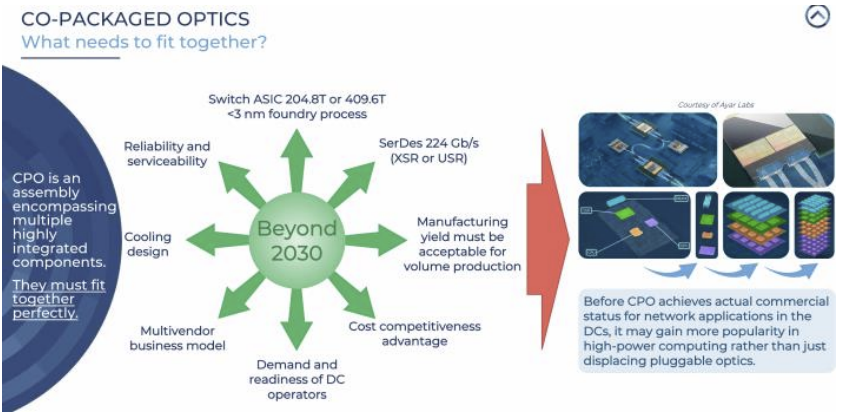

AI 光通信时代背景下,数据中心规模持续扩大,带宽容量与高速数据传输速率的需求明显增加。光电共封装(Co-Packaged Optics,CPO)作为一种新型的光电子集成技术,光电共封装技术进一步缩短了光信号输入和运算单元之间的电学互连长度,在提高光模块和ASIC芯片之间的互连密度的同时实现了更低的功耗,是解决未来大数据运算处理中海量数据高速传输问题的重要技术途径。

凭借其在成本、功耗、集成度等多维度上的显著优势,CPO技术有望在 AI 时代迎来历史机遇期。近期,开源证券通信团队发布行业深度报告《深度拆解CPO:AI智算中心光互联演进方向之一》,通过深度拆解CPO技术,带您探讨AI光通信时代的产业变化、技术核心以及发展潜力,把握CPO产业的投资机遇。

CPO的深度拆解:或带动硅光光引擎、CW光源、光纤、FAU、MPO/MTP等需求增长

—

CPO方案通过将光引擎与交换芯片近距离互连,相较于传统可插拔方案具有高带宽、低延时、低功耗、小尺寸等优点,同时利用基于硅光的光引擎,CPO使用经过验证的半导体制造技术和设计工艺实现了高水平的光学和电气设备集成,有望实现规模化生产、可靠性提高和成本的降低。

1、 硅光光引擎是CPO技术核心之一

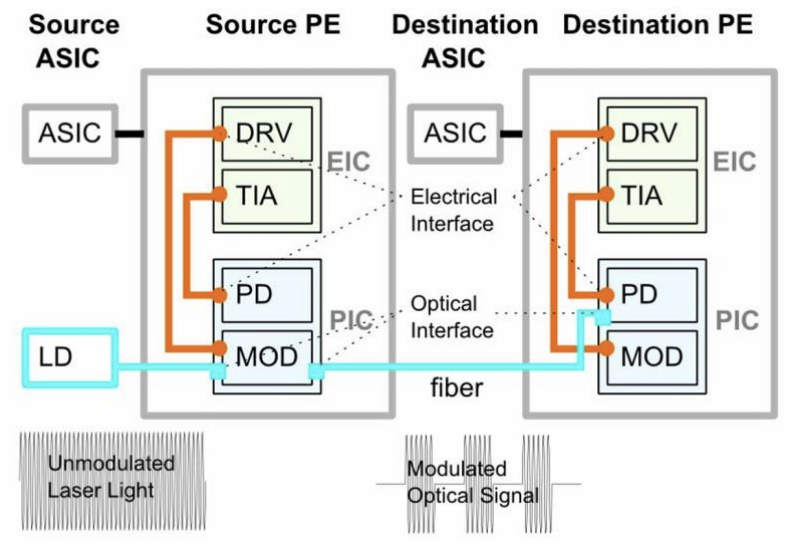

CPO 作为一种光电器件的先进封装技术,涉及系统架构、芯片制造和封装的升级,从运行原理上看,无论与ASIC的接近程度如何,实现光电转换的高性能光引擎(PE/OE)都是CPO技术的核心。

光引擎是CPO技术核心之一

资料来源:H. Hsia等《Heterogeneous Integration of a Compact Universal Photonic Engine for Silicon Photonics Applications in HPC》

光引擎平台:硅光技术是目前CPO光引擎的主要解决方案

目前CPO光引擎主要的技术路径分别是基于硅光的技术路线和基于VCSEL的技术路线。硅光子集成技术因其集成度高、CMOS工艺兼容已成为CPO光引擎的主要解决方案。

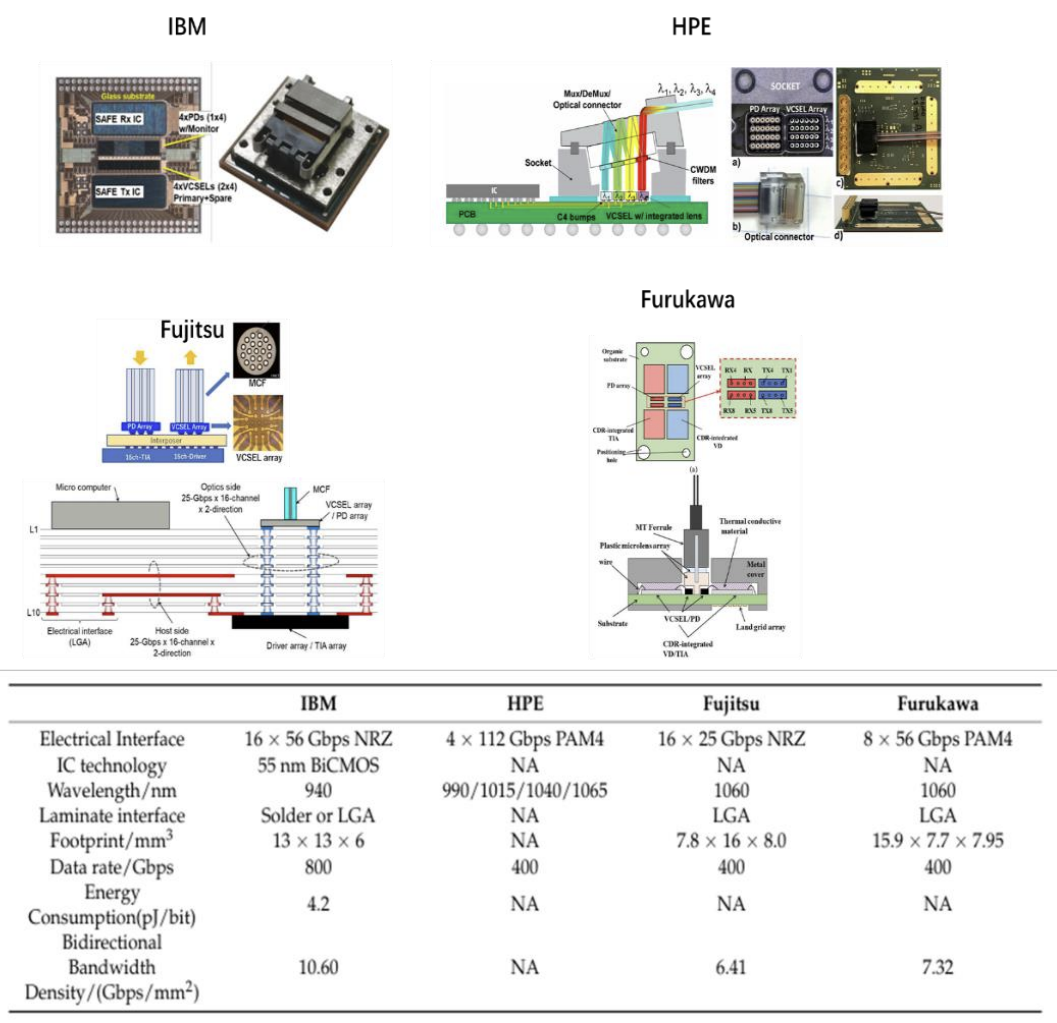

VCSEL方案在成本和功耗方面为超短距离传输提供了明显的优势,但整体目前仍处于研发阶段。当前参与VCSEL CPO研究和开发的主要组织是IBM、惠普、富士通和古河。

VCSEL CPO方案适用于超短距离传输

资料来源:Tian, W等《Progress in Research on Co-Packaged Optics》、开源证券研究所

硅光子集成技术是基于硅和硅基衬底材料,利用现有CMOS工艺进行光器件开发和集成的新一代技术。目前硅光CPO的讨论多集中于光源、调制器、封装集成等技术路径的研究。

光引擎集成:CPO技术将增加先进封装工艺需求

核心光引擎的集成方案对系统的功率、性能、面积和成本有着深远的影响。随着半导体封装技术的演进,光引擎集成及CPO技术路径多样,整体发展方向包括:功率,实现效率的优化;性能,提高带宽,缩短通信长度;面积,满足HPC芯片所需的要求,以先进封装实现更小尺寸;成本,通过不断减少替代材料,提高制造效率。

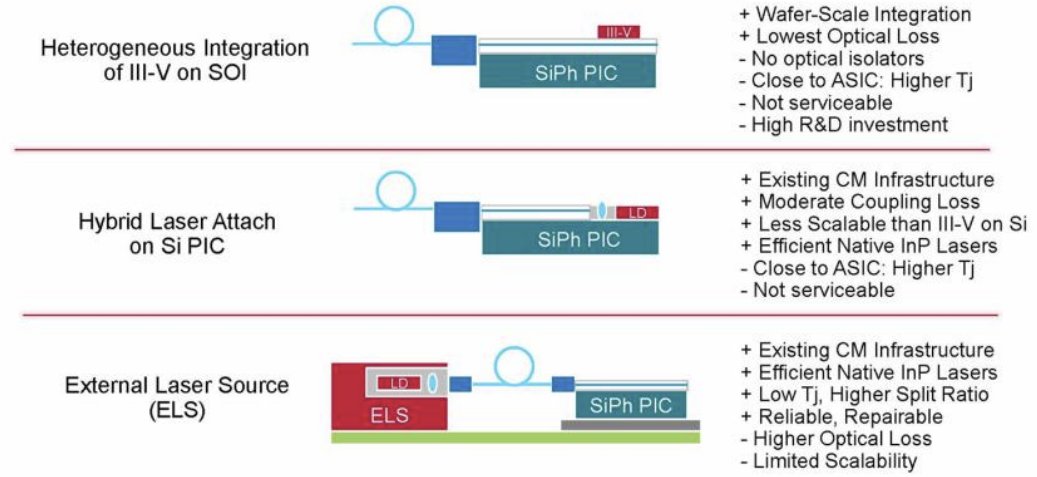

2、 光源:ELS是当前硅光CPO的主流选择

目前外部激光源 (ELS)是硅光CPO的主流选择。基于硅光CPO,由于硅材料间接带隙的能带结构使得它无法实现高效率的片上光源,因此在硅基光电子芯片中其光源器件仍然需要依赖InP/GaS材料的半导体激光器。当前主流硅光CPO将连续波(CW)激光器光源单独外置,作为高密度封装体的外围可插拔单元。这样的设置有如下优点:一是实现了易失效光源元件的可更换和可标准化生产;二是激光器的外置减少了硅芯片单元的散热压力,有利于系统稳定性;三是外部光源单元可以灵活配置,如采用波分光源或者非致冷光源等。

硅光CPO主要采用ELS

资料来源:John E等《Performance and Reliability of Advanced CW Lasers for Silicon Photonics Applications》

输出功率和功耗是ELS的关键特征。激光源作为CPO核心器件之一,在CPO体系中激光器约占系统功耗的10-20%,硅光CPO中ELS的引入带来更高的插入损耗,这些损耗需通过增加ELS的输出功率来补偿。

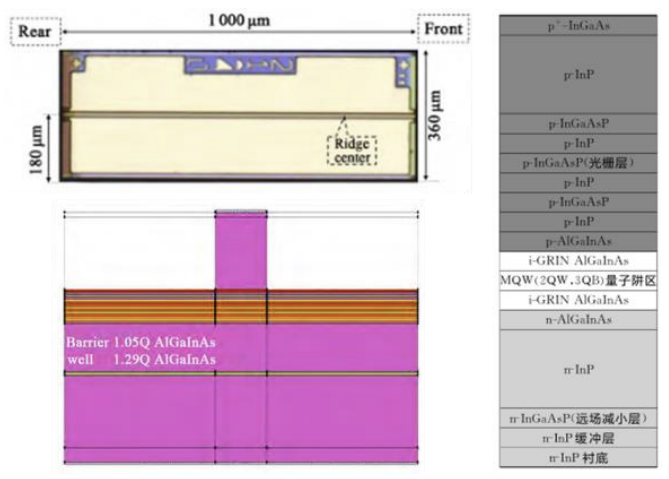

ELS向着高功率、低噪声、低功耗方向发展。在整个ELS产品设计中,关键技术包括耐高温大功率光源芯片,光路透镜耦合,电流源控制反馈等,其中在激光光源方面,CW-DFB激光器仍是目前CPO技术最优的外置光源选择。

CW-DFB激光器是目前CPO技术最优的外置光源选择

资料来源:刘耀等《用于共封装光学的高功率连续波DFB激光器》

ELS正在逐步标准化。当前CPO系统中针对ELS做标准定义的主要有三个标准组织,分别是OIF(光互联论坛)定义的ELSFP(External Laser Small Form Factor Pluggable)标准; IPEC(国际光电委员会)定义的PELS(PluggableExternal Laser Source)标准; CCITA(中国计算机互连技术联盟)定义的ELS(External Light Source)。

3、光学互联:CPO光链路较可插拔方案引入额外的光纤及光纤连接器

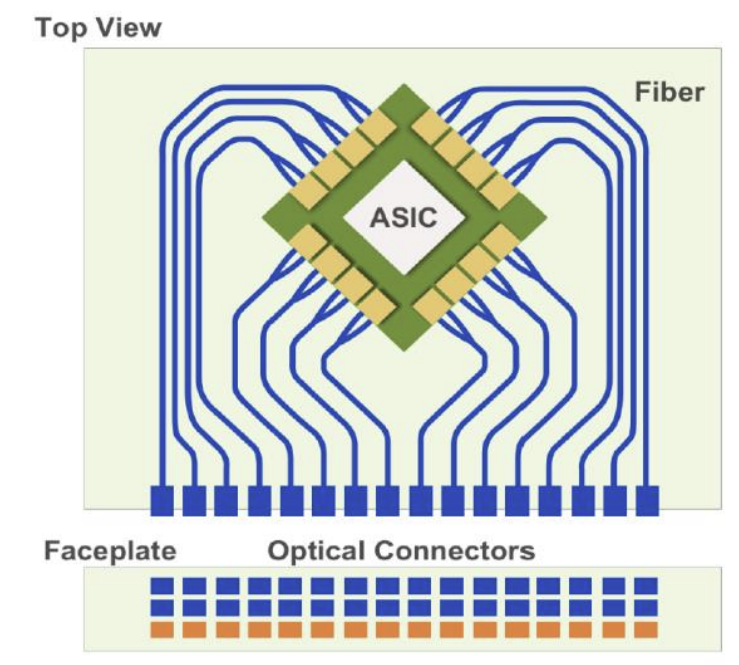

CPO内部光纤路由的处理也是CPO的一大挑战。从构成上来看,CPO系统的实现涉及各种组件的系统规模集成,包括光引擎、ASIC封装、光纤阵列、大型体基板、电源管理组件、热组件、路由光纤组件以及外部激光源等。

CPO光互连主要包括光引擎到前面板连接器的光纤路由

资料来源:COBO《Design Considerations of Optical Connectivity in a Co-Packaged or On-Board Optics Switch》

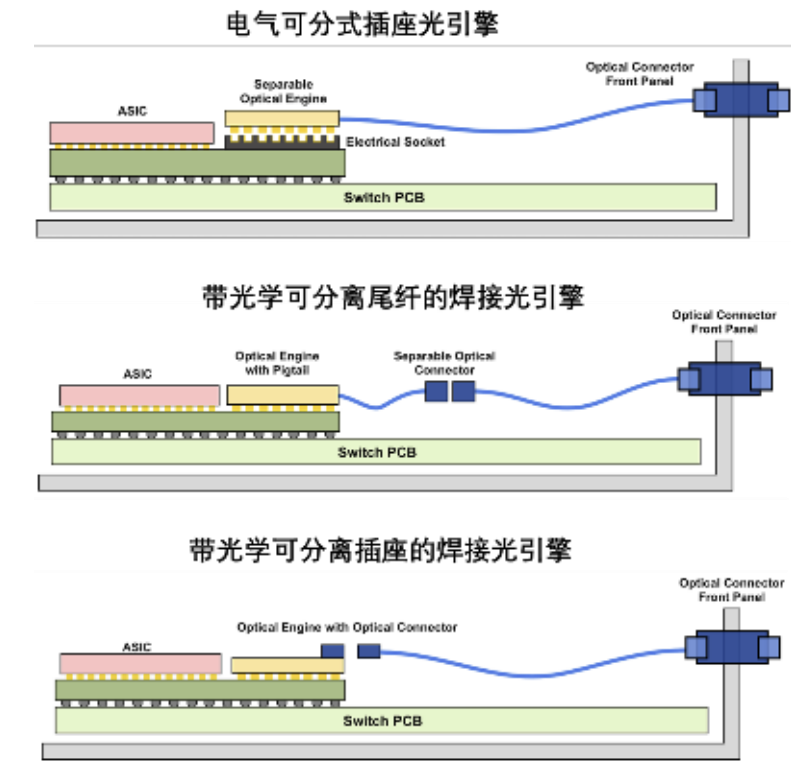

(1)光引擎端:根据不同封装工艺,可通过对光引擎接口进行设计保护措施、更换组件,从而改良整个 CPO 交换机的良率和可靠性。组件和CPO的物理分离包括电气、光学分离。

光引擎接口保护涉及多种光电分离方案

资料来源:COBO《Design Considerations of Optical Connectivity in a Co-Packaged or On-Board Optics Switch》、开源证券研究所

硅光光引擎通过与光纤阵列单元(FAU)耦合实现光的进出。光纤阵列(FA)是把光纤按照一定的间距排列固定起来形成的光器件,是光进出光器件的通道。

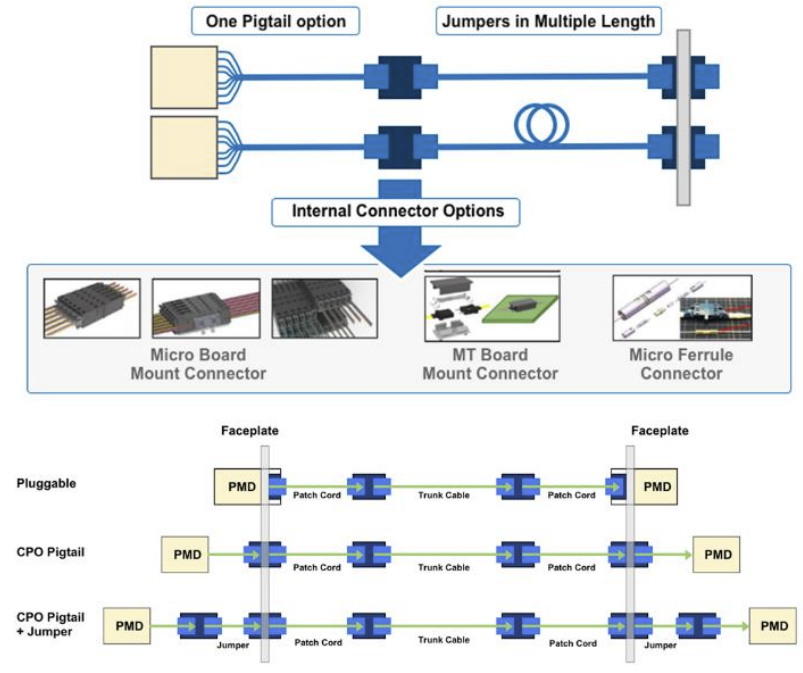

(2)光引擎—前面板:需要不同长度的光纤来路由每个光学引擎,尾纤长度的变化带来设计及安装维护的挑战。

中板/板载光互连解决方案:通过在OE和面板之间增加一个中板连接器,并提供各种长度的跳线,尾纤长度可以减少到只有一个设计,可以简化光引擎在面板上的安装,简化光引擎供应商的制造,并降低光引擎和附加尾纤损坏的风险。另一方面,该方案会增加额外的连接器从而导致光损耗,由于潜在连接点数量的增加,CPO 组件将在设计中添加额外的光纤电缆和连接器,除了CPO解决方案中包含的电缆外,还增加了一组跳线电缆,可以使用更不敏感且易于清洁的气隙或扩束连接器,来降低这些连接的组装和维护相关的运营成本。

通过引入中板/板载光互连解决方案来解决光引擎尾纤长度不同问题

资料来源:COBO《Design Considerations of Optical Connectivity in a Co-Packaged or On-Board Optics Switch》

在光纤线束管理方面,还可以进一步引入光纤柔性板(Fiber Shuffle)、带状光纤(Fiber Ribbon)、光缆捆束(Fiber Harness)、光纤带集线器(Fiber ribbon accumulator)、光纤预装盒等来提高光纤的可靠性。

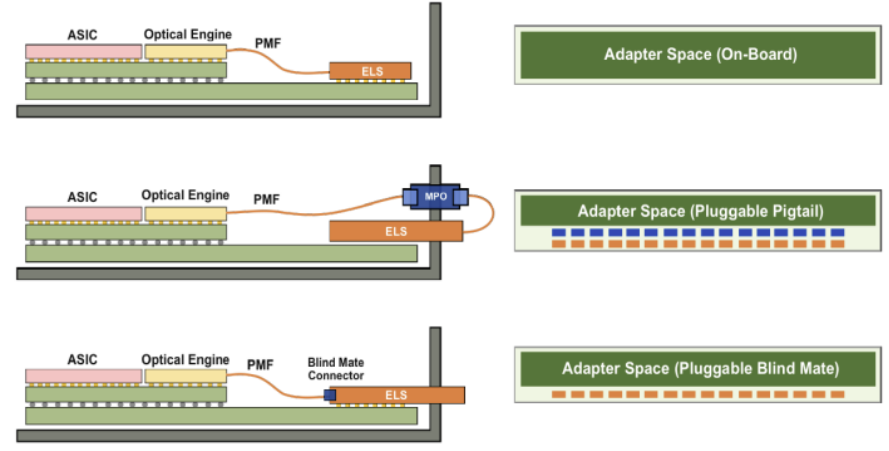

(3)ELS—光引擎:ELS与光引擎的互联设计可分为 3 种类型:板载光学 (OBO) 设计、带光纤尾纤的前板可插拔设计(可插拔尾纤)和带盲插接光纤连接器的前板可插拔设计(可插拔盲插)。三种 ELS 类型中的每一种都使用一组保偏 (PM) 光纤来连接到光引擎。

保偏光纤是一种特种光纤,它能够在光纤通信和传感系统中保持光的偏振状态。

ELS通过保偏光纤连接光引擎

资料来源:COBO《Design Considerations of Optical Connectivity in a Co-Packaged or On-Board Optics Switch》

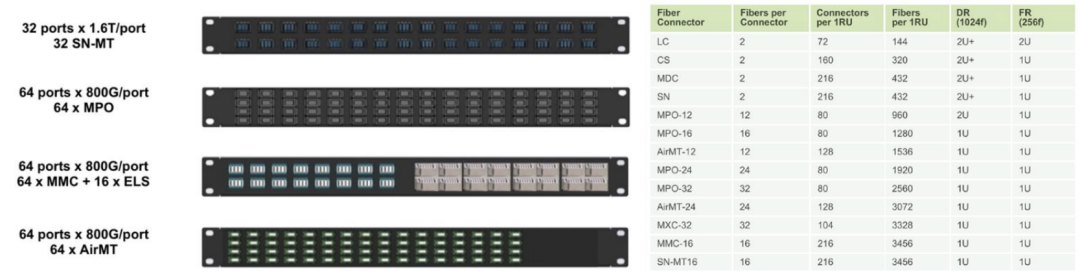

(4)前面板侧:前面板可以通过多种方式进行配置,具有光纤端口通道密度和连接器类型的不同组合,同时需满足数据中心的运营需求,并协助开关盒的热管理,特别是如果这涉及>1kW系统的空气冷却。

光纤连接器品种繁多,以 MPO/MTP 为代表的多芯连接器有望成为未来连接器发展趋势。整体来看,光纤连接器正朝着低成本、标准化、高埠数、小型化、结构简化、易于安装的方向发展,特别是随着局域网、数据中心和存储区域网络中的连接器增多,高密度与小型化将是未来连接器发展的主要方向。

总的来看,与使用可插拔光模块的光链路相比,使用CPO的光纤链路包含更多的光纤连接器。这些附加连接器包括CPO交换机面板上的连接器以及任何中板连接器。必须仔细考虑这些连接器的特性,以确保CPO共封装的光学器件满足可与可插拔模块互操作;向后兼容已安装在数据中心的结构化布线。

前面板需对光纤端口通道密度、连接器类型和热管理等综合考虑

资料来源:COBO《Design Considerations of Optical Connectivity in a Co-Packaged or On-Board Optics Switch》

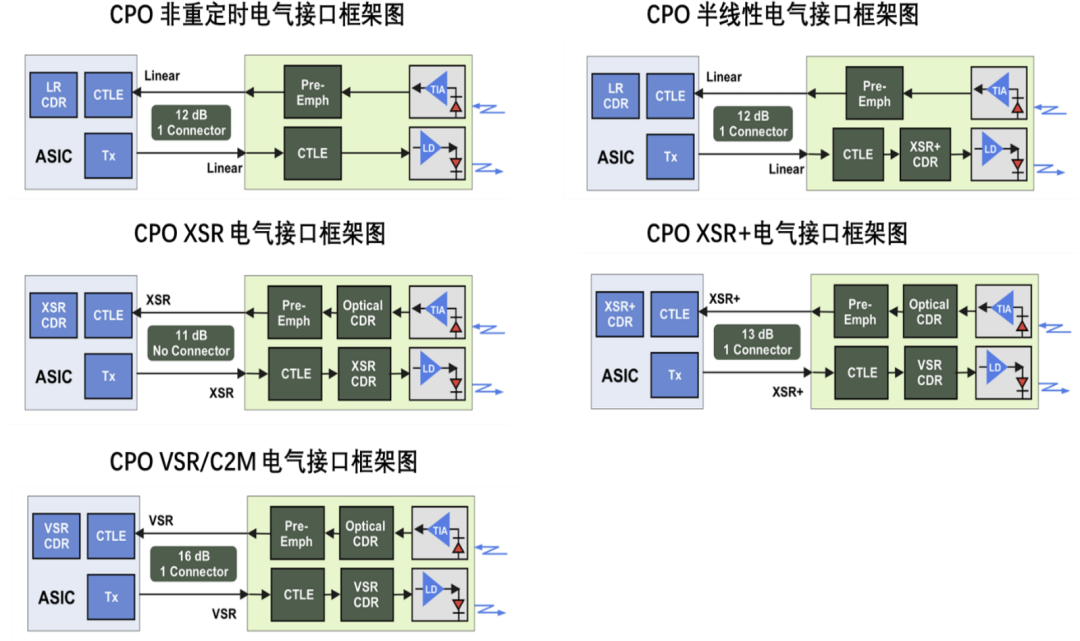

4、电气互联:CPO中单片CMOS EIC或成发展方向

随着数据中心核心交换机的聚合带宽达到 51.2 Tb/s,由于交换机前面板的有限空间有限以及 SerDes 和交换机 IC 之间的通道损耗过大,传统可插拔光模块面临更多挑战,CPO通过交换芯片和光引擎的共封装,在消除交换机前面板的带宽密度限制的同时,封装内毫米级的电气链路也可以产生更小的损耗,并进一步简化 SerDes 设计和降低功耗。

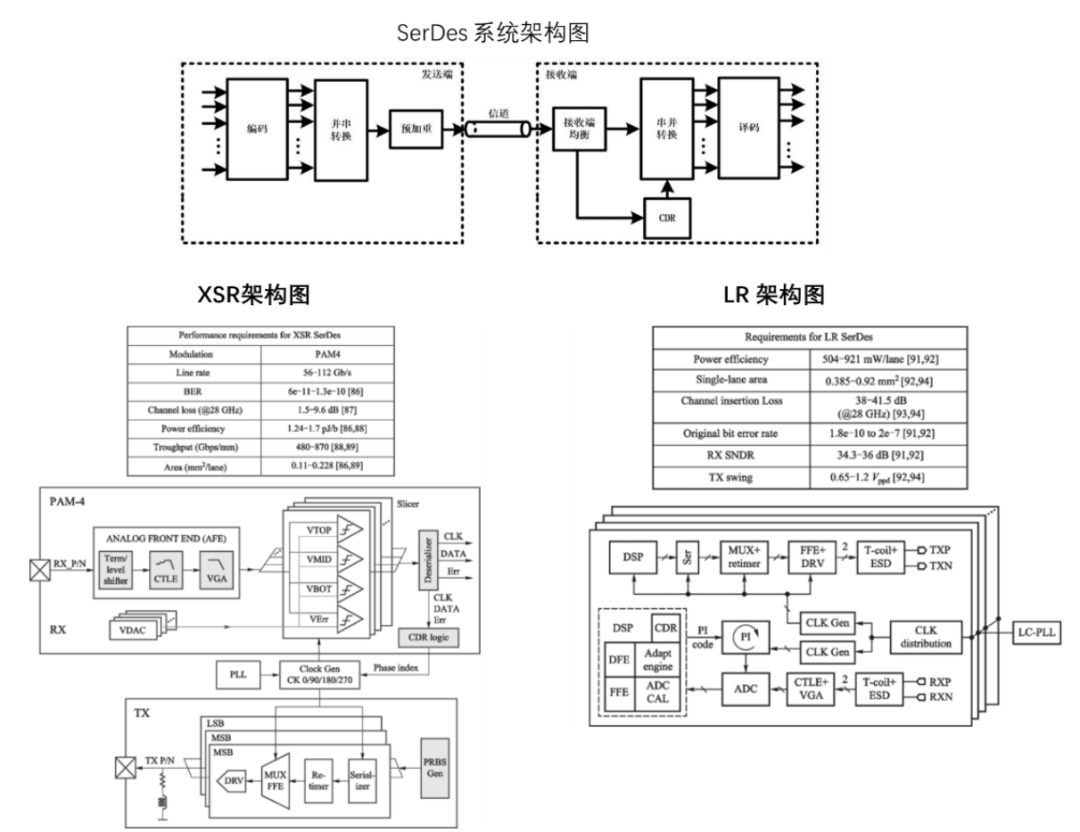

不同的 SerDes 模块针对不同的距离进行了优化。SerDes串行互连技术采用差分信号传输方式实现数据的高速传输,具有功耗低、抗干扰强、速度快的优点。

CPO电气接口选择多样

资料来源:COBO《Design Considerations of Optical Connectivity in a Co-Packaged or On-Board Optics Switch》、开源证券研究所

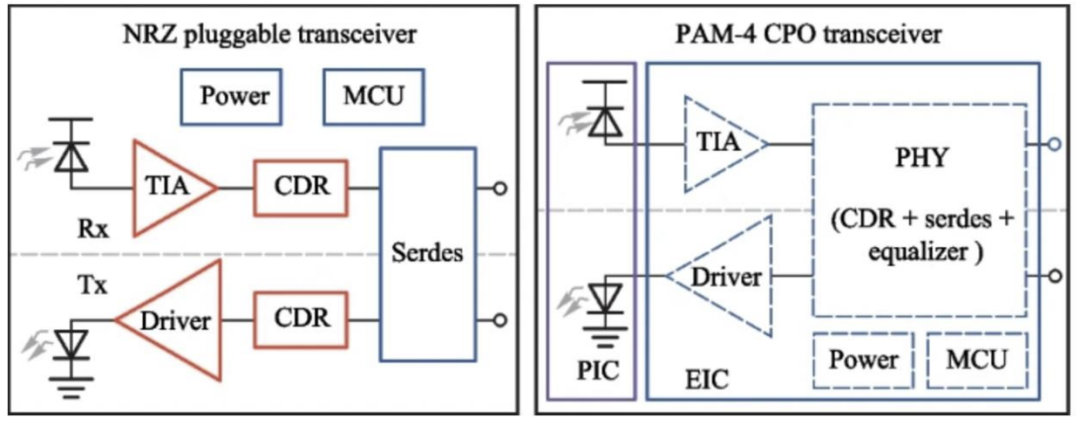

高速CPO中DSP功能或仍不可或缺。在传统光模块中,随着通道速度达到 50 Gb/s 及以上,在NRZ上引入了PAM-4调制方案 以节省一半的带宽,其中大多数后端功能(如 CDR 和 SerDes)都合并到 CMOS PHY 芯片(有时也称为 DSP)中,其中还引入了密集的数字均衡,以补偿 PAM-4 信号中信号完整性的恶化。

主机端 XSR SerDes 通过缩短两个通信芯片之间的连接距离来优化功率效率、集成密度和传输延迟。线端LR SerDes主要处理非理想因素,如有限带宽、线性调频效应、噪声、色散效应和器件的非线性。

不同的 SerDes 模块针对不同的距离进行了优化

资料来源:Min Tan等《Co-packaged optics (CPO): status, challenges, and solutions》、开源证券研究所

单片 CMOS EIC或成为重要发展方向。对于需要极高集成度和功耗的 CPO 应用来说,一方面,EIC单片集成方法或是不可避免的,这需要将模拟 TIA 和Driver进一步集成到 CMOS EIC 芯片中,另一方面,这要求接收器设计技术从模拟优化的 SiGe 转向数字优化的 CMOS,需要克服噪声、带宽和线性度等问题的技术挑战。总的来看,随着这些技术与低功耗和低成本的CPO本征优势相结合,单片 CMOS 电子器件或成为未来重要发展方向。

单片集成EIC或成CPO发展方向

资料来源:Min Tan等《Co-packaged optics (CPO): status, challenges, and solutions》,

AI光通信时代,CPO迎三大产业变化

—

1、变化1:硅光技术加速发展,CPO硅光光引擎不断成熟

硅光光引擎作为CPO的技术核心,在AI光通信时代加速成熟。硅光技术是实现光子和微电子集成的理想平台。在当前“电算光传”的信息社会下,微电子/光电子其技术瓶颈不断凸显,硅基光电子具有和成熟的CMOS微电子工艺兼容的优势,有望成为实现光电子和微电子集成的最佳方案。硅光光引擎作为当前CPO光引擎的主流方案,硅光技术的成熟有望进一步带动CPO的发展。

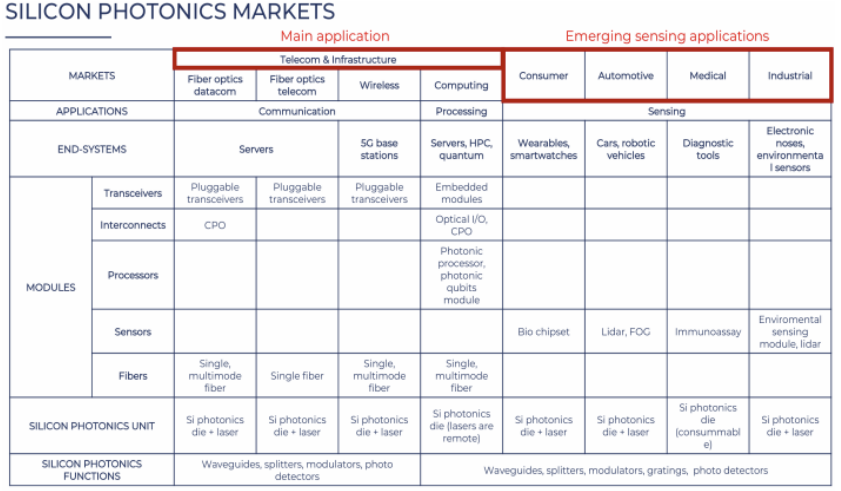

硅光技术应用广泛

资料来源:Eric Mounier《Chiplets enabled by silicon photonics》

(1)从硅光技术应用来看,硅光技术作为硅光光模块、CPO和OIO光引擎底层技术,高速时代基于硅光光通信的拓展,有望进一步催化硅光光引擎技术成熟。

数据中心中硅光光模块已逐步应用

资料来源:Eric Mounier《Chiplets enabled by silicon photonics》

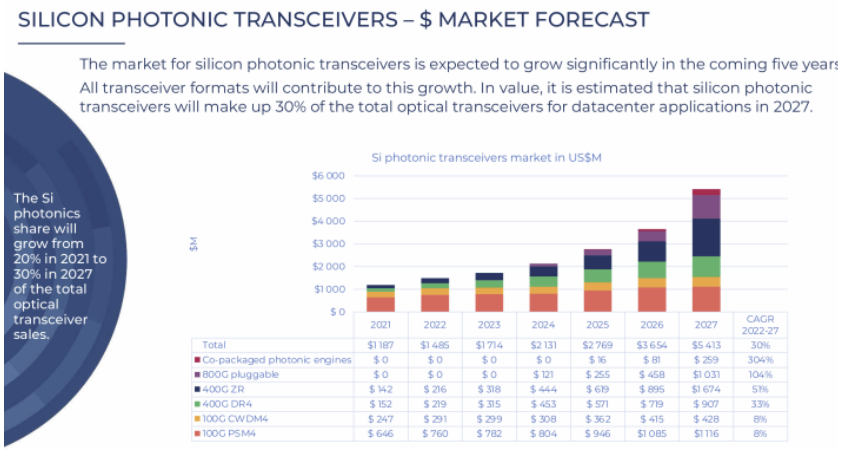

在光模块应用中,在不同速率和距离的与传输距离下,硅光子技术相比III-V器件竞争优势有演进的过程,随着大数据中心对联结带宽的不断升级,多通道技术成为必须,高集成高速硅光芯片成为性价比更优越的选项,目前800G光模块已在全球范围内逐步进入商用部署阶段。同时长期来看,我们认为随着硅光光模块低成本、多通道大带宽的技术优点有望得到进一步凸显,硅光光模块的渗透率有望得到进一步提升,特别是在1.6T、3.2T等高速时代,有望进一步促进硅光技术成熟,CPO中硅光光引擎有望得到进一步发展。

硅光收发器市场规模有望不断扩大

数据来源:Eric Mounier《Chiplets enabled by silicon photonics》

在OIO应用中, 硅光方案高度契合OIO发展需求, OIO(In-Package Optical I/O)是一种基于芯片的光互联解决方案,与计算芯片(CPU、GPU、XPU)集成在同一封装中,旨在实现分布式计算系统中它们之间的无缝通信(跨板、机架和计算行),在相同能效情况下,OIO的边带宽密度与UCle、NVlink、PCIe等电互连相当,但传输距离远超电互连。

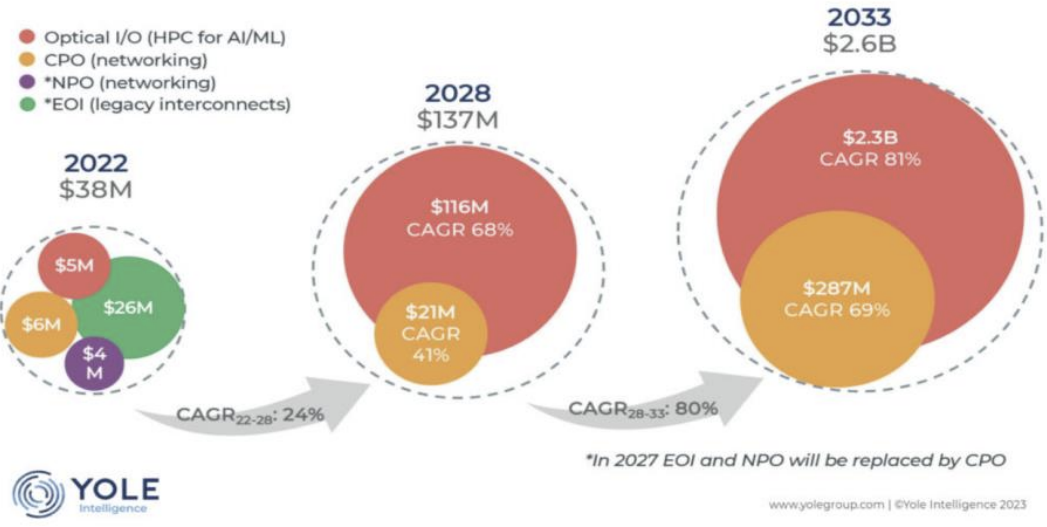

我们认为,OIO目前仍处于起步阶段,与计算芯片联合设计仿真优化,在物理层和协议层方面都需要进一步创新,不同于CPO主要针对网络架构,针对计算架构的OIO中硅光+Chiplet或成为主流解决方案,头部芯片厂商及硅光初创公司/设计公司企业不断投入研究,随着AI技术对算力的持续需求,芯片间数据传输不断增大,OIO的技术优势有望不断凸显,与OIO技术通源的CPO技术也有望得到相应的重视和发展。据Yole预测,OIO市场有望从2022年的500万美元增长到2033年的23亿美元。

高耗能算力场景促进OIO发展

资料来源:Martin Vallo《Co-packaged optics are inching closer to reality》

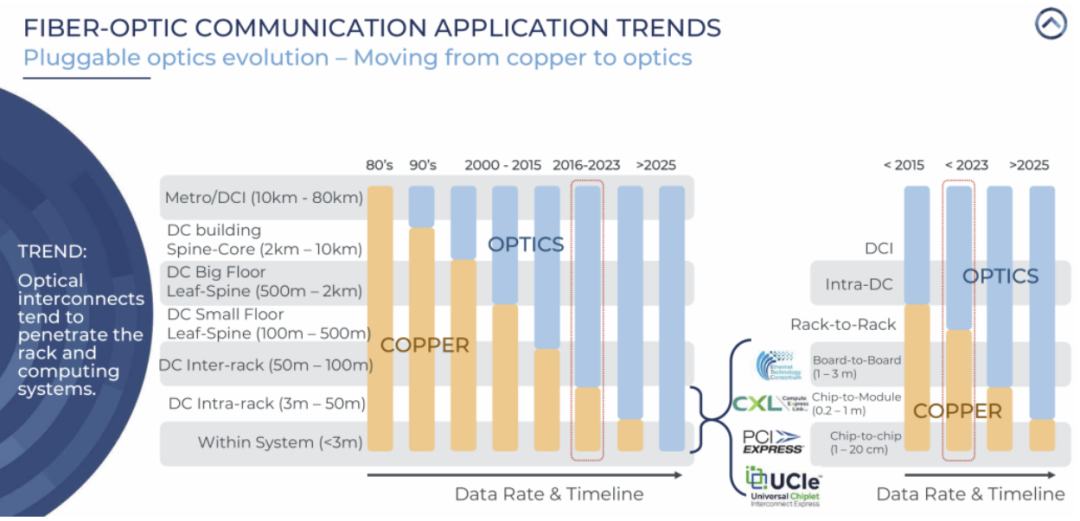

(2)从硅光发展节奏来看,全球企业积极推动硅光技术发展,硅光产业链进一步完善。目前,硅光技术产业仍在发展,产业链不断构建,已初步覆盖了前沿技术研究机构、设计工具提供商、器件芯片模块商、Foundry、IT企业、系统设备商、用户等各个环节。

硅光产业链不断完善

资料来源:Yole

(3)从硅光产业机会来看,硅光方案景气度不断提高,硅光技术有望成厂商切入CPO产业契机。第25届中国国际光电博览会(CIOE 2024)于2024年9月11-13日在深圳国际会展中心举办。在AI的拉动下,从光电芯片及光器件/光引擎到光模块在向高速率方向快速升级,同时以硅光/CPO/薄膜铌酸锂/相干等为代表的新技术成熟度不断提升,其中硅光技术成熟度和市场关注度显著提升,众多企业布局硅光技术。

海内外企业积极布局硅光子技术

资料来源:各公司官网、讯石光通信网、开源证券研究所

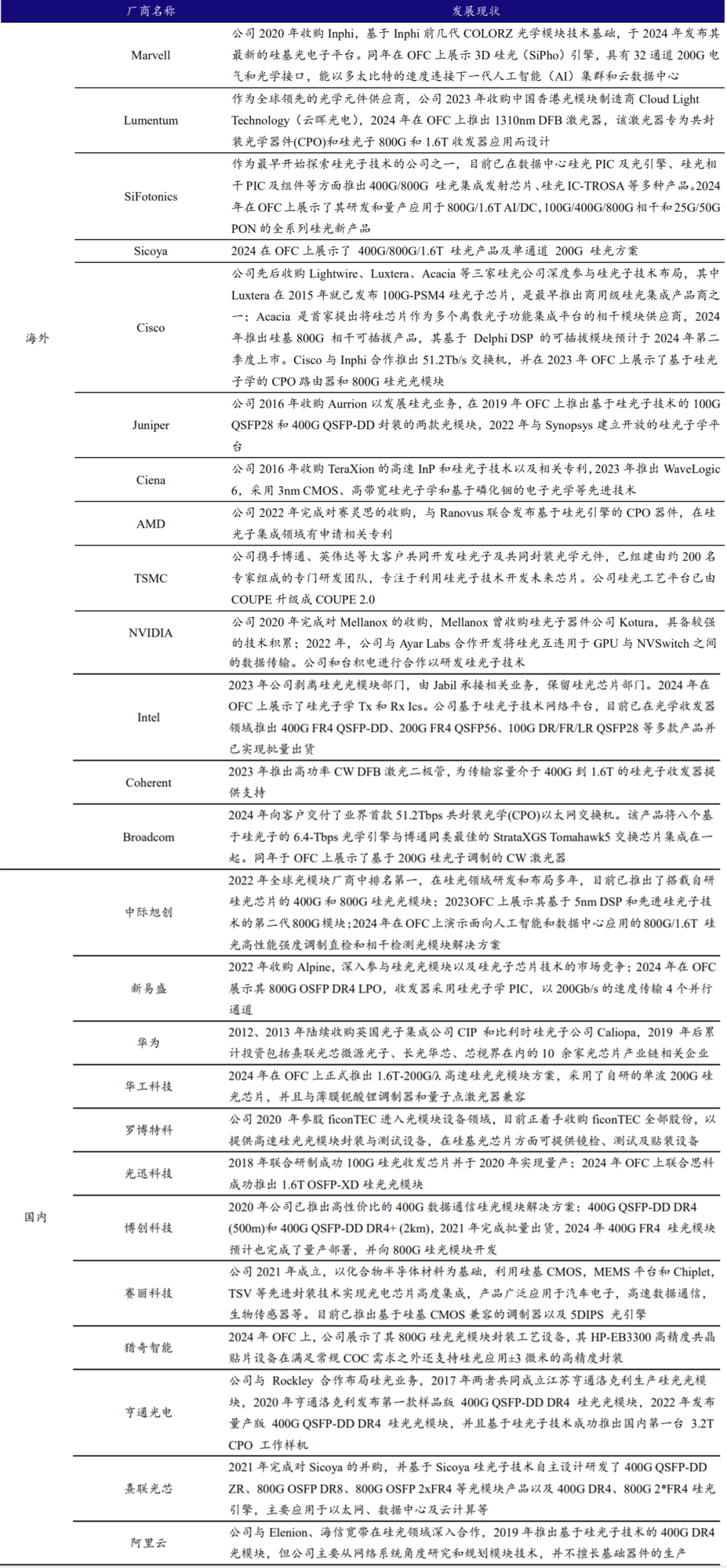

2、变化2:龙头厂商积极布局CPO,进一步催化CPO产业发展

各大芯片厂商积极布局CPO技术,硅光CPO原型机不断推出。CPO方案众多,各大芯片厂商推出CPO方案。我们认为,一方面,其中基于硅光光引擎的CPO技术为主流方案,有望充分受益于硅光技术的发展;另一方面,龙头厂商的入局,有望进一步加速CPO产业链的完善和发展。

硅光CPO原型机不断推出

资料来源:Tian, W等《Progress in Research on Co-Packaged Optics》、开源证券研究所

变化3:AI时代高速交换机需求增长,CPO方案优势不断凸显

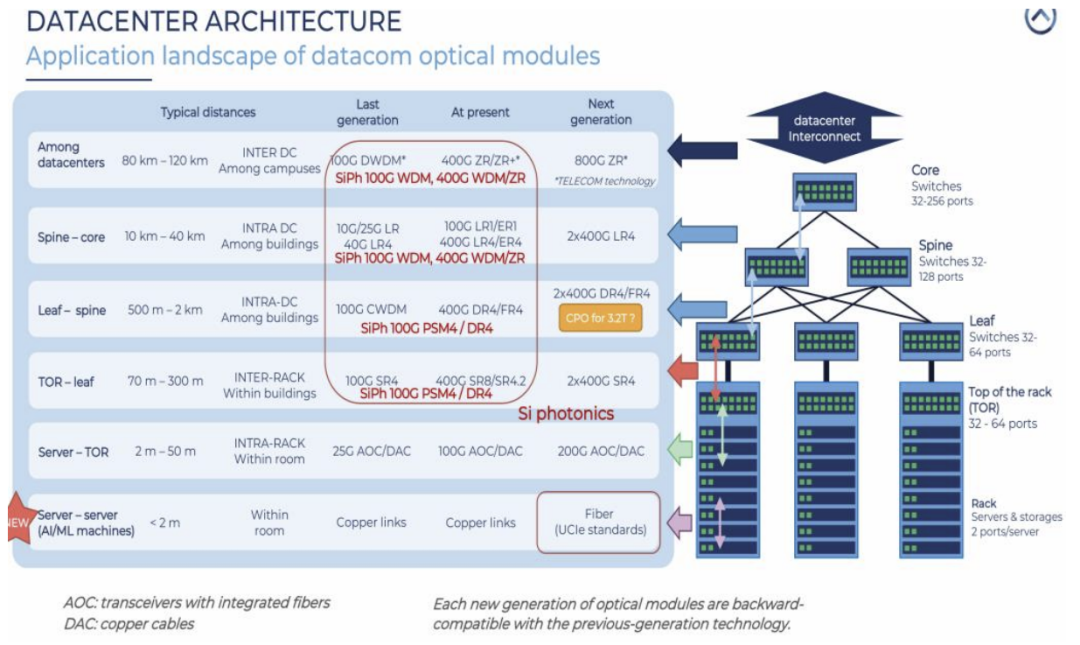

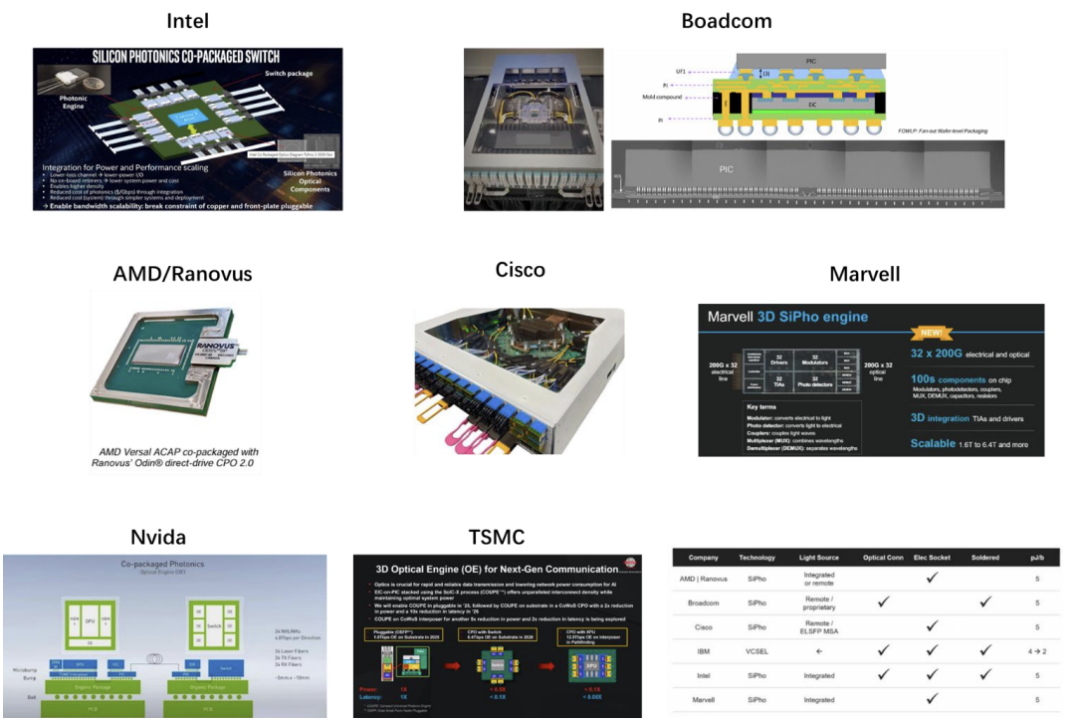

CPO交换机AI时代迎来产业机遇期。在光互连不断穿透机架和计算系统的背景下,交换机作为光通信网络系统中核心网络设备,随着全球AI的高速发展,AI集群规模持续增长,AI集群网络对组网架构、网络带宽、网络时延、功耗等方面提出更高要求,带动交换机朝着高速率、多端口、低功耗等方向迭代升级,AI时代CPO方案交换机有望迎来产业机遇期。

光互连正逐渐取代铜互连

资料来源:Martin Vallo《Co-packaged optics are inching closer to reality》

AI时代交换机带宽加速迭代,端口互联速度快速发展

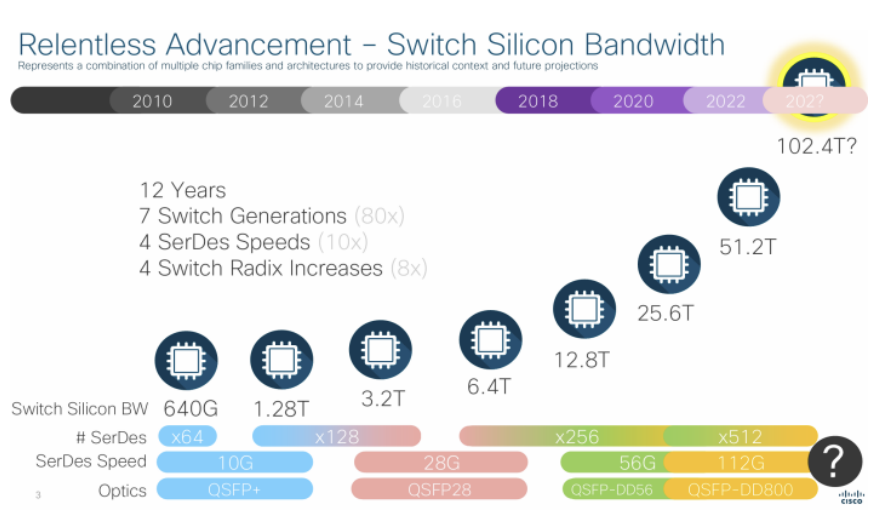

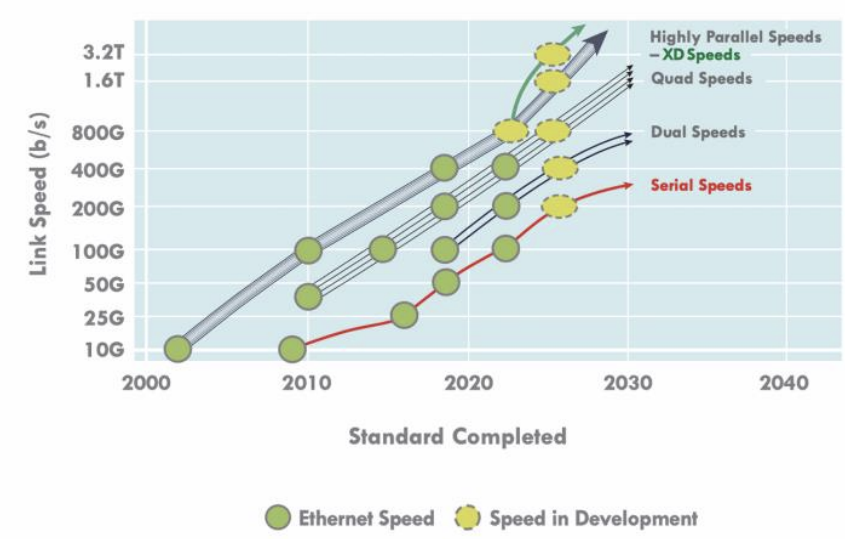

AI加速交换机带宽发展,端口互联速度快速迭代。自2019 年后全球数据中心产业开始步入算力中心阶段,根据Cisco数据,2010-2022年全球数据中心网络交换带宽提升了80倍,特别是近期AIGC的快速发展带来网络架构的升级和GPU的加速迭代,进一步带动设备间更高的带宽需求,2023年作为AI元年,AI在一半的时间内将互联速度提升一倍,数据中心交换芯片的演化角度来看,目前进入每两年翻一番的快速增长阶段,预计2025年有望实现102.4T的容量,对应1.6T光口。

ASIC带宽约每两年翻一番

资料来源:Rakesh Chopra《Looking Beyond 400G: A System Vendor Perspective》

以太网速度跟随ASIC带宽的扩展

资料来源:Sandeep Razdan等《Co-Packaged Optics Integration for Hyperscale Networking》

AI集群加速Scale out,后端网络组网拉动高速交换机需求

在数据中心里,包括前端网络和后端网络,以及内部计算网络。AI训练集群带来GPU互联需求,新增后端网络组网需求。传统数据中心架构下,传统服务器与交换机之间通过网卡互相通信,网卡可直连CPU进行数据交换;AI服务器比传统服务器新增GPU模组,服务器内部GPU之间通过PCIe Switch芯片或NVSwtich芯片实现内部互联,GPU模组通过对应的网卡与其他服务器的网卡互联,实现各节点之间的通信。因此相比传统网络架构,AI服务器组网增加后端网络组网(Back End),增加了每台服务器的网络端口数量,拉动对高速交换机、网卡、光模块、光纤光缆等组件的需求。

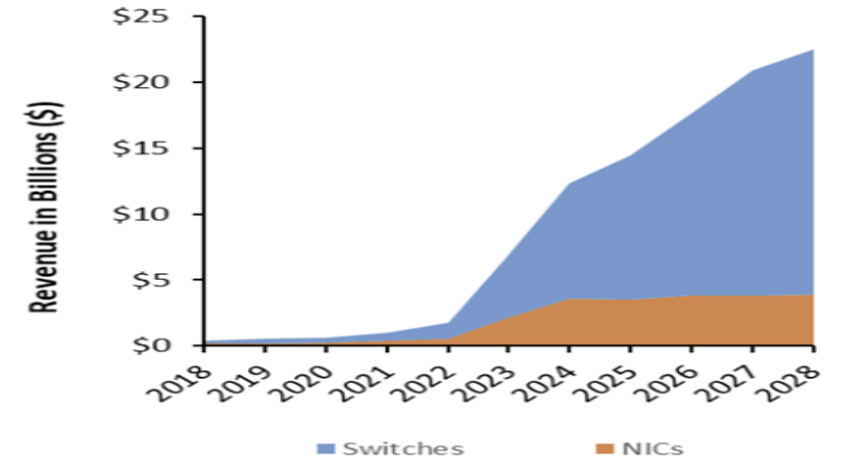

AI/ML后端网络市场规模快速增长,进一步拉动交换机需求。

RDMA市场中交换机需求快速增长

资料来源:650 group

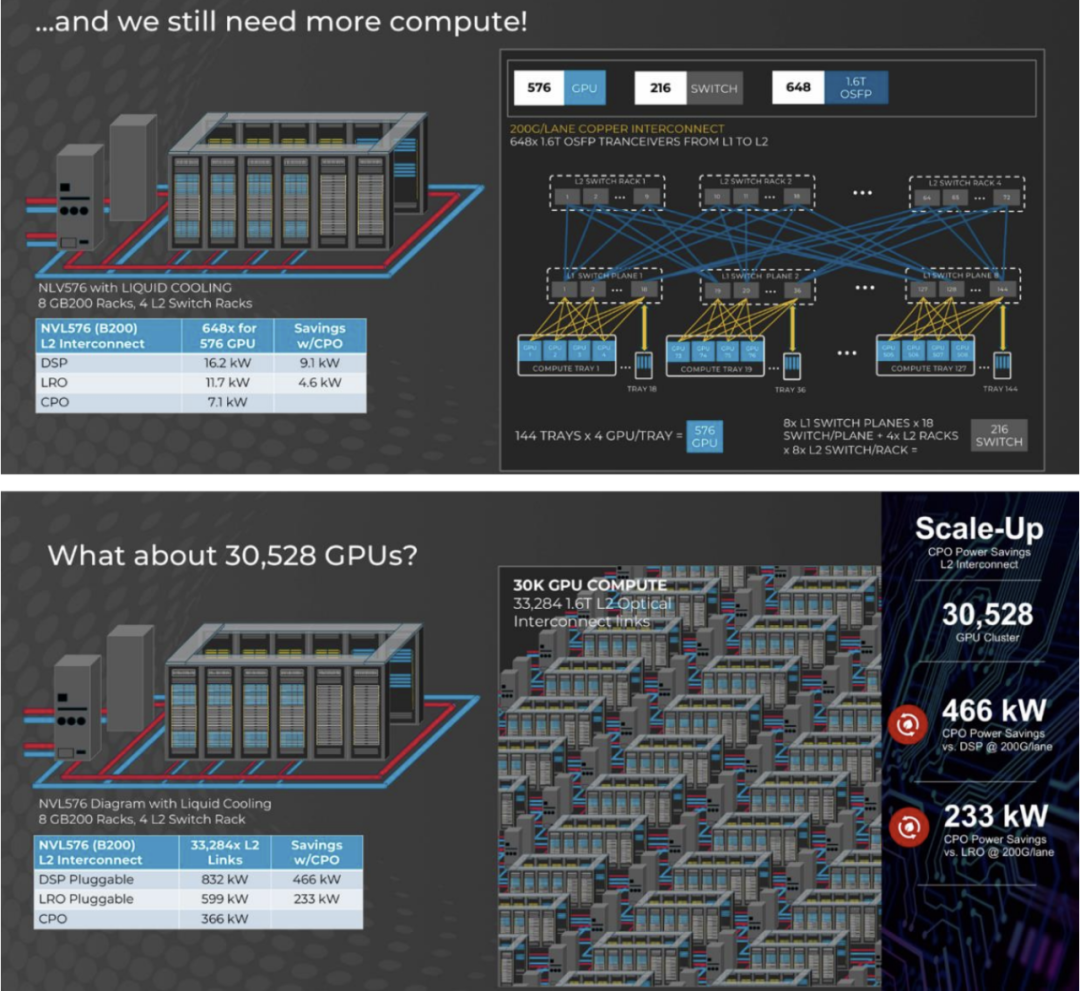

AI集群加速Scale out,大集群组网带来大量高速交换机需求。随着AI模型参数持续增长,带动集群规模从百卡、千卡拓展至万卡、十万卡,对于超节点及超大规模组网架构,未来有望从Scale up和Scale out两个维度来实现总算力规模的提升,Scale out推动组网架构从2层向3层、4层架构拓展,带来大量高速交换机需求。

Scale up:主要通过提高单个节点内的算力规模,进而提升集群的算力规模。Scale out:主要通过高速互联容纳更多节点,进而提升集群整体算力规模。

AI集群功耗成关键挑战,CPO方案优势凸显

CPO是在成本、功耗、集成度各个维度上优化数据中心的光电封装方案。传统光电互连采用的板边光模块,走线较长,寄生效应明显,存在信号完整性问题,且模块的体积较大、互连密度低、多通道功耗较大。共封装技术通过将光收发单元与ASIC芯片封装在一个封装体内,进一步缩短了光信号输入和运算单元之间的电学互连长度,在提高光模块和ASIC芯片之间的互连密度的同时实现了更低的功耗。CPO相较于可插拔光模块,带宽密度提升一个数量级,能量效率优化40%以上。

随着AI集群的快速扩张,系统功耗迅速提升。进一步,随着NVL576进一步向着万卡集群组网,以30528 GPU集群为例,根据Broadcom的估算,基于DSP 可插拔方案,其互连功耗将达到832kW,采用CPO方案有望降低到366kW。

CPO方案有望有效降低AI集群功耗

资料来源:Rajiv Pancholy《Will You Need CPO in 3 Years?》、开源证券研究所

CPO发展潜力较大,商业落地仍需产业协同

—

总体来看, CPO是实现高集成度、低功耗、低成本、小体积的最优封装方案之一。虽然CPO具有显著的潜在优势,但CPO目前处于产业化初期,除了技术上的挑战外,更受集成光学器件的市场接受度、标准和制造能力的限制。作为光通信解决方案的一环,其发展仍需整体产业链的协同推进。

1、技术方面,CPO在工艺、仿真以及测试等方面仍面临很多挑战

(1)封装工艺:CPO涉及到TSV、TGV、多层高密度互连基板、Bumping和芯片堆叠等先进封装中的关键技术,每种关键技术都有各自的优缺点,比如:TGV通孔技术可能会损伤玻璃造成表面不光滑,大多数TGV加工方法效率低,没法大规模量产,TGV结构的电镀成本和时间比TSV略高,玻璃衬底表面的黏附性较差,容易导致RDL金属层异常,玻璃本身的易碎性和化学惰性给工艺开发带来了难度;TSV的通孔加工、孔填充都有较高的工艺要求,此外还涉及到晶圆减薄,存在潜在的成品率和可靠性的问题;

(2)器件性能问题:目前的硅光技术还有一些需要克服的技术难题,比如如何减少硅波导的损耗、如何实现波导与光纤的有效耦合、如何克服温度对于功率和波长稳定性的影响等。

(3)散热技术:热会导致机械应力,可能导致基板翘曲,影响光耦合和电子互连的性能,CPO中分配给光学和电气元件的空间非常有限,由于光学元件对热量较为敏感,散热设计成为CPO另一个挑战;

(4)仿真技术:随着集成密度的不断提高,为提高产品的一次设计成功率,仿真技术在CPO设计阶段的应用将显著提升,由于CPO面临着光学、电学、热力学等交叉学科的融合和多层级的跨越,对仿真提出了更高的要求。目前光子设计自动化(PDA)工具能够提供精确的光子器件仿真,但仿真效率较低,不适合大规模系统级仿真,同时电子设计自动化(EDA)工具大多基于电路级或系统级仿真,因此能够应用于电路级和系统级仿真的光子器件模型是大规模电子-光子联合仿真的关键,是未来光电共封装器件大规模商业化的重要条件,可以提高设计效率。光-电-热-力多物理场的跨维度耦合仿真以及芯片-封装-系统的跨尺寸联合仿真将成为仿真领域的发展趋势和难点;

(5)测试和良率挑战:由于光芯片是直接与电芯片通过先进封装工艺封装在一起,这给良率和测试带来了诸多挑战,同时光器件和电器件建立在不同的制造工艺技术上,因此具有不同的测试要求。共封装的光学器件具有较高的通道密度,同样给测试带来挑战。

2、 产业协同:AI时代CPO方案或与可插拔方案长期共存

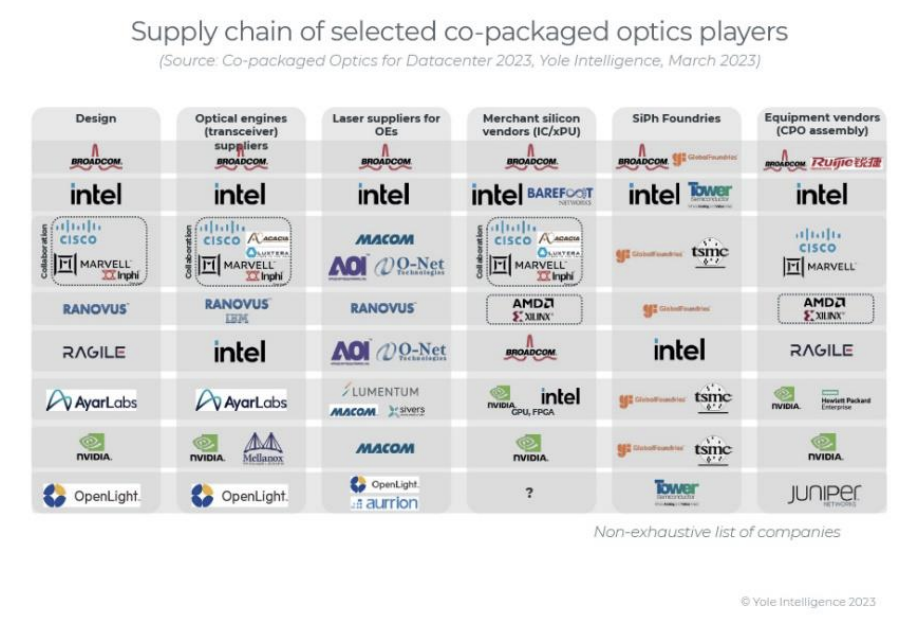

根据Yole报告,CPO技术路线下,产业链分为了设计、光引擎、激光光源、芯片供应商、硅光代工、设备商(CPO组装)。随着CPO产业的逐步成熟,CPO正逐渐从学术研究成果转变为市场需求产品,但在当前可插拔光学器件行业逻辑下,要成为商业化主流方案,仍需交换芯片及设备厂商、各模块厂商、各元器件厂商和运营商共同参与,其商业落地或将会对产业格局产生深远影响:

(1)CPO方案与可插拔方案产生直接竞争。目前可插拔光模块市场供应链已经非常成熟,具备成熟工业生态系统,它包括分立或集成元件供应商、生产发射器和接收器光学组件(TOSA 和 ROSA)的光学公司、多路复用器、数字信号处理器 (DSP) 和 PCB,以及组装/测试集成商,商业体系复杂,参与厂商众多。

(2)CPO产业有望带动硅光代工行业发展。随着AI/ML系统的发展,未来数十亿个光互连、芯片-芯片和板-板的市场潜力推动大型代工厂为大规模生产做准备,由于大多数光子学制造知识产权 (IP) 由非代工公司持有,因此 Tower Semiconductor/Intel、GlobalFoundries、ASE Group、TSMC 和 Samsung 等大型代工厂正在准备硅光子学工艺流程,以接受设计公司的任何光子集成电路 (PIC) 架构。

CPO产业链逐步成熟

资料来源:Yole

我们认为,受益于底层硅光技术的进一步发展,龙头芯片/主机厂商的深度布局及示范作用,以及AIGC算力需求对高带宽、低功耗、低成本的光通信方案的追求,CPO有望在AI时代迎来其历史机遇期,特别是随着CPO相似技术的OIO技术的进一步成熟,商业系统中的通信和计算技术更紧密地集成,传统架构(基于铜的电气互连)的芯片到芯片或板到板的能力瓶颈有望被打破,使得高性能计算等领域得到拓展,CPO商业化落地有望得到进一步加速,但另一方面,CPO作为整体光通信解决方案中的一环,其实际商业化发展高度依赖于产业协同,特别是在传统可插拔方案的成熟市场下,其与可插拔光模块方案在不同应用场景下仍各有优劣,并有望保持较长时间的共存。

CPO市场前景广阔

资料来源:Yole

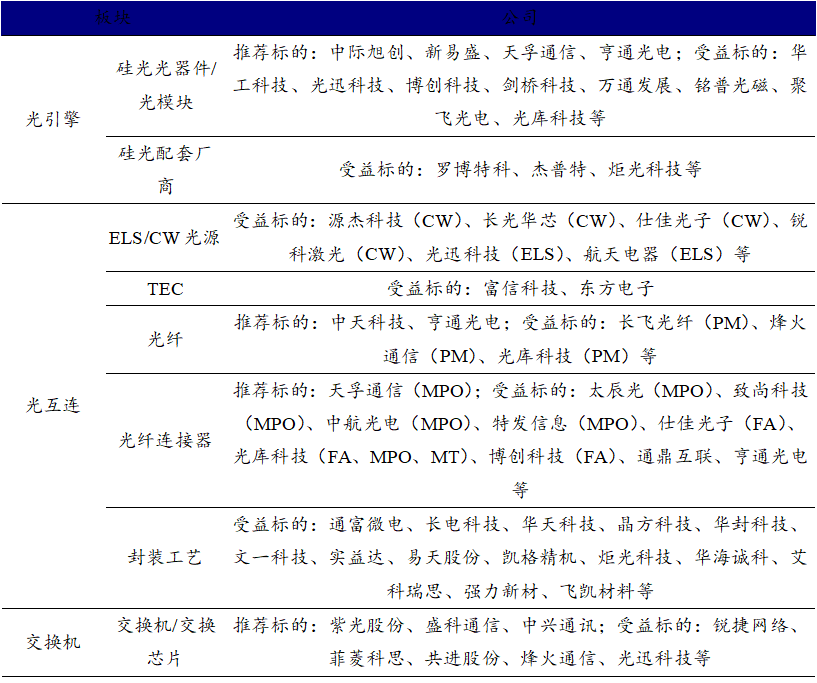

受益标的梳理

—

我们认为,当前CPO发展主要以海外AI算力需求为核心,产业链参与厂商以海外企业为主导,其发展或对传统光通信产业链格局产生较大影响:一是硅光技术重要性进一步凸显;二是CPO加大对先进半导体工艺的需求,整体来看,需重点关注以下板块:

CPO产业重要板块及公司

资料来源:开源证券研究所

申明:感谢原创作者的辛勤付出。本号转载的文章均会在文中注明,若遇到版权问题请联系我们处理。

----与智者为伍 为创新赋能----

联系邮箱:uestcwxd@126.com

QQ:493826566