本期主要介绍智多晶DDR Controller的常见应用领域、内部结构、各模块功能、配置界面、配置参数等内容。

01

智多晶DDR Controller应用领域

1.1 工控领域

在工业控制系统中,设备需要长时间稳定运行,同时对数据的实时性和准确性要求极高。智多晶DDR Controller的高可靠性和精准时序控制能力,使其成为工控领域的理想选择。例如,在PLC(可编程逻辑控制器)中,它能够快速响应各种传感器信号,实时处理和存储大量的控制数据,确保生产设备的精准控制和高效运行。此外,智多晶的SEAL 5000的SA5Z-30、SA5Z-50、SA5Z-100等FPGA器件内置了ARM核和DDR Controller,这种一体化的设计不仅提高了系统的集成度,还降低了功耗和成本。在一些复杂的工业自动化场景中,如机器人控制、智能工厂的生产调度系统等,这种FPGA内置DDR Controller的方案能够实现软硬件协同设计,将控制流与算法流分开处理,大幅提升运算速度和系统性能,同时兼顾了性能和成本的平衡。

1.2 通信领域

随着5G、6G等高速通信技术的发展,对数据传输速率和带宽的要求越来越高。智多晶DDR Controller支持多种高速接口和高性能DDR存储,能够满足通信设备对大数据量快速存储和读取的需求。在基站设备中,它能够高效处理大量的信号数据,支持高速的数据缓存和传输,确保信号的实时处理和发送。同时,在网络交换机、路由器等设备中,智多晶DDR Controller能够快速调度和转发数据包,提高网络的吞吐量和响应速度,为用户提供更流畅的通信体验。

1.3 消费电子领域

在手持设备等消费电子产品中,用户对设备的性能和功耗都非常关注。智多晶DDR Controller的高效数据传输能力和低功耗设计,使其能够为这些设备提供强劲的性能支持。例如,在手持设备中,它能够快速读取和存储应用程序数据、高清图片和视频等,提升设备的运行速度和响应能力。同时,通过优化的时序控制和电源管理,有效降低了内存访问过程中的功耗,延长了设备的续航时间,让用户能够更长时间地享受各种功能。

1.4 汽车电子领域

随着汽车智能化的发展,汽车电子系统需要处理越来越多的数据,如自动驾驶辅助系统中的图像识别、传感器数据融合等。智多晶DDR Controller的高可靠性和实时性,能够满足汽车电子系统对数据处理的严格要求。在自动驾驶辅助系统中,它能够快速处理来自摄像头、雷达等传感器的大量数据,实时生成准确的环境感知信息,为车辆的自动驾驶决策提供有力支持。

02

智多晶DDR Controller介绍

智多晶的Seal 5000系列FPGA芯片,内置DDR Controller硬核。其中SA5Z-30系列中的D1_U213内嵌了128Mb的DDR2颗粒、D2_U256内嵌了512Mb的DDR2颗粒、D3_U256内嵌了1Gb的DDR3颗粒;这对用户来说,不但降低了设计的难度,也有助于降低系统功耗,有利于提升产品竞争力。SA5Z-30系列(D0_U324)、SA5Z-50系列、SA5T-100系列、SA5T-366系列,可以外挂DDR3颗粒,其中SA5T-366系列还支持外挂DDR4颗粒。

2.1 DDR Controller结构框图

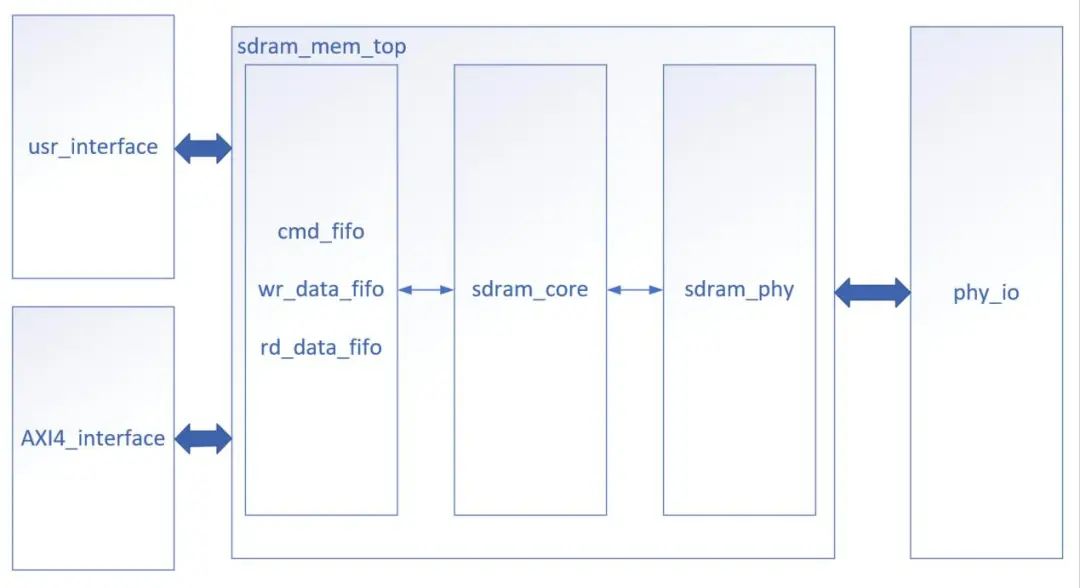

DDR Controller结构框图,如图一所示,其中user_interface模块为DDR2/3 Controller的用户接口部分,由软逻辑实现;sdram_mem_top模块DDR2/3 Controller的核心控制部分,由硬核实现;phy_io模块是DDR2/3 Controller的模拟电路部分,由软逻辑和原语实现。

图一 DDR Controller结构框图

2.1.1 各模块功能简述

user_interface模块,采用类似于AXI-Stream总线的方式,通过ready、valid和last信号握手方式,实现命令和读写数据的控制。

AXI4_interface模块(目前仅支持SA5T-100系列),采用标准的AXI4接口。

sdram_mem_top模块包含:interface_fifo模块、sdram_core模块和sdram_phy模块。sdram_phy模块中包含Initialization Logic、Read Training Logic和Write Leveling Logic等子模块。

phy_io模块,在SA5Z-30器件DDR Controller使用ODDRx2/IDDRx2,其余器件DDR Controller使用ODDRx4/IDDRx4。

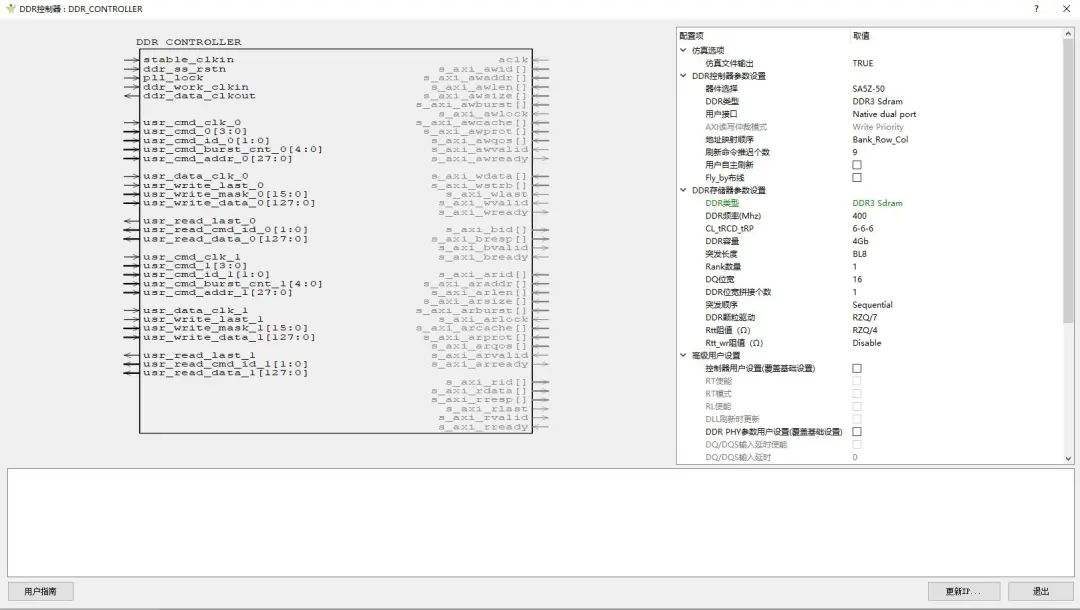

2.2 DDR Controller配置界面

图二为智多晶DDR Controller的配置界面,可以看到包含一些必须的配置参数,方便客户根据自己的硬件设计,灵活地配置;下面会对其配置参数做详细的介绍。

图二 DDR Controller配置界面

2.3 DDR Controller配置界面参数含义

2.3.1 器件选择

根据设计中使用的芯片,可以选择为SA5Z-30、SA5Z-50、SA5T-100、SA5T-336。

2.3.2 DDR 类型

DDR 类型,可以选择为 DDR2 Sdram 或 DDR3 Sdram。SA5Z-30-D1-U213和 SA5Z-30-D2-U256为合封DDR2,SA5Z-30-D3-U256为合封DDR3;其余芯片需要外挂DDR颗粒。

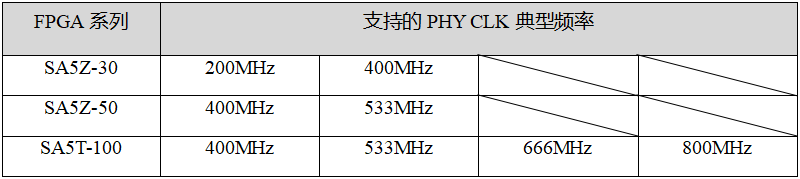

2.3.3 DDR 频率

不同型号的FPGA器件,DDR Controller支持的频率范围不一样。用户只能在限定的频率范围内选择合适的频率值(表中未包含的更低的频率,器件也可支持,参数的选择可以咨询FAE)。

2.3.4 CL-tRCD-tRP

DDR 的第一时序参数,会根据用户选择的“DDR 类型”以及输入的“DDR 频率”自 动生成相应的时序参数供用户选择。单位为一个PHY CLK时钟周期。

2.3.5 DDR 容量

在选择 DDR 类型后,会自动生成可支持的 DDR 容量大小。不同的 DDR 容量与 DQ 位宽相关,会影响 BANK、ROW、COL 的宽度。

2.3.6 突发长度

数据传输的突发长度分为 BL4和 BL8。只有 SA5Z-30 系列器件支持 BL4和 BL8 选项,其余系列器件只支持 BL8 选项。

2.3.7 Rank 数量

选择使用rank的数量,最大支持2个rank(SA5Z-30 仅支持单rank)。

2.3.8 DQ 位宽

数据传输通道的宽度,与DDR 位宽拼接个数共同决定单个时钟周期的数据传输量。有 8 通道器件和 16 通道器件两个选项,不同 DQ 位宽与 DDR 容量共同影响 ROW、BANK、COL 的宽度。

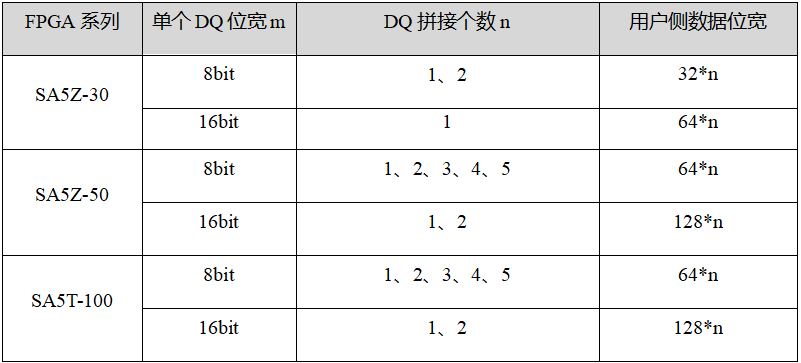

2.3.9 DDR 位宽拼接个数

根据硬件板卡挂载的DDR颗粒的 DQ 位宽,选择合适的DDR位宽拼接个数。对于不同的器件可以拼接的个数不同,下表列出了可以拼接的个数和对应的用户侧数据位宽。

注:DDR Controller支持最多32bit的DQ位宽;如果不使用DDR Controller的硬核,用户可以使用软逻辑以支持更宽的位宽。

2.3.10 突发顺序

支持 Sequential 和 Interleaved 两种突发顺序。Sequential 按照连续地址顺序访问存储单 元。Interleaved 按照协议规定的交错模式下访问存储单元。

2.3.11 DDR 颗粒驱动

DDR 颗粒驱动选择。DDR2 Sdram 中可选“Full Strength”和“Reduced Strength”。相 比与 Full Strength,Reduced Strength 驱动信号的强度减弱。DDR3 Sdram 中可选择 RZQ/7 和 RZQ/6 两种阻值。选择后会自动修改 MR 寄存器中的设定。

2.3.12 Rtt 阻值

与WL 相关ODT 的阻抗设置,RZQ/n,RZQ = 240Ω ,n = 2、4、6、8、12。

2.3.13 Rtt_wr 阻值

与写操作相关的动态 ODT 的阻抗设置。

下一期我们将继续讲解智多晶DDR Controller使用时的注意事项,敬请关注。

【直播预告】