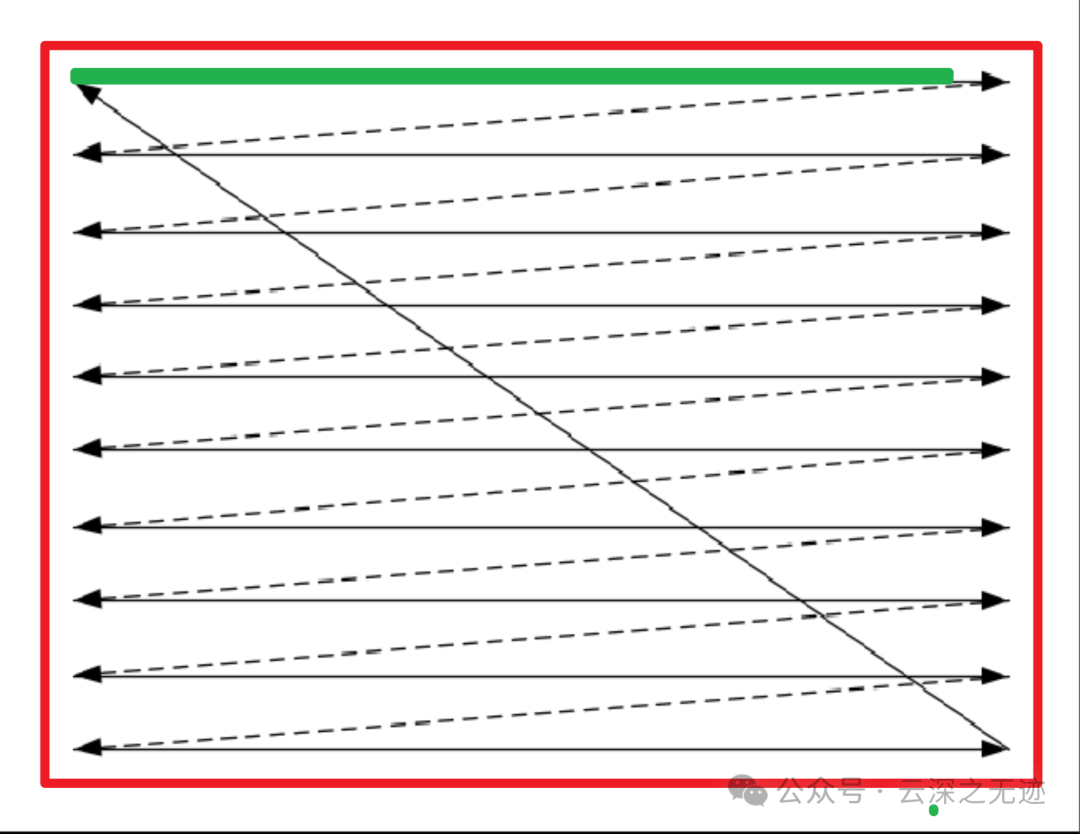

终于还是要写这个了,我们传输视频的时候,究竟是如何传输的,我们都知道一张照片,以及图像多了叫视频流:

这样

也就是说,一帧图像就是一张图像,而一张图像又是一行一行的像素堆砌出来的。

我们这次就来说明白,所谓的图像是如何被传输出去的。

在电气层面,肯定也是,一帧图像被分为好多行,输出,接着结束。然后传输下一帧。

而我们里面的这些状态,比如什么时候是一行传输完了,到下一行了,以及一帧完事了,下一帧开始传输,都要有详细的定义。

最主要的事情是同步!

同步(英语:Synchronization),指在一个系统中所发生的事件(event)之间进行协调,在时间上出现一致性与统一化的现象。在系统中进行同步,也被称为即时(in time)或同步化的(synchronous, in sync)。

所以在一个传输系统里面最重要的就是同步信号,因为相当于干活的标识。

在视频传输里面-VSYNC(Vertical Sync) 和 HSYNC(Horizontal Sync) 是两个关键的同步信号,分别用于帧同步和行同步。

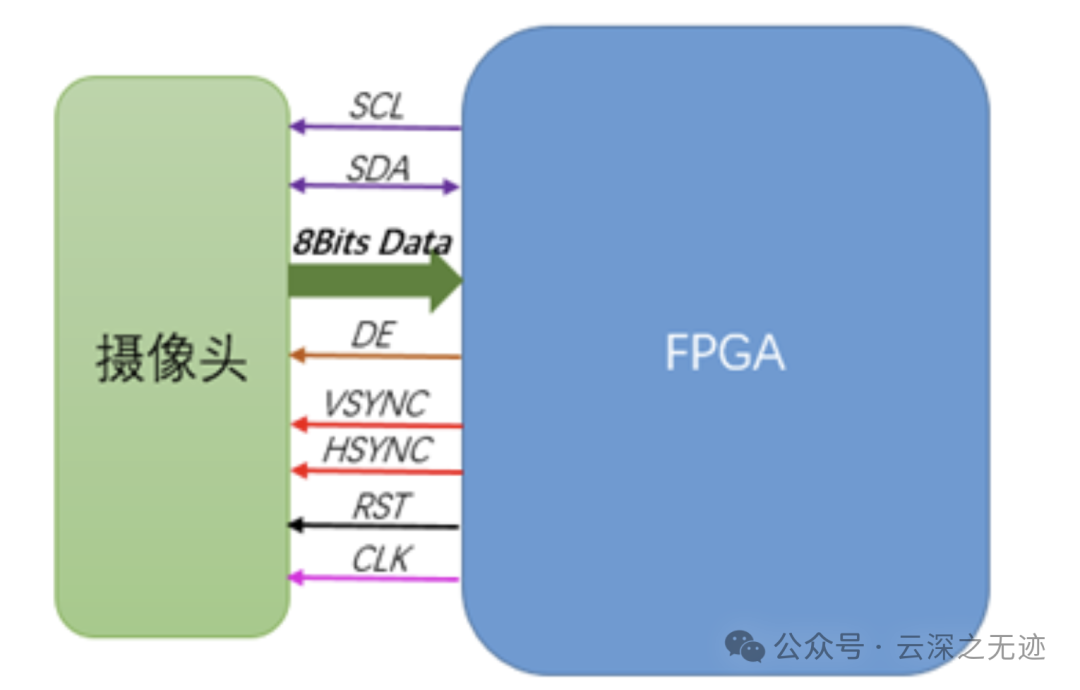

这个是一个FPGA获取并口摄像头的链接图

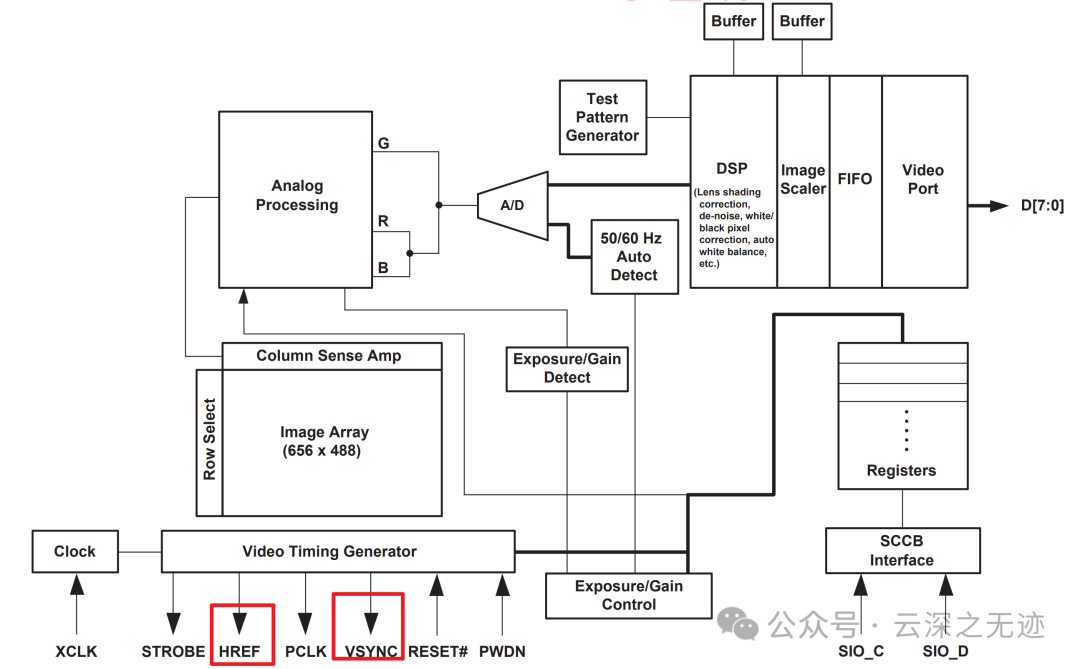

淘宝上面最多的是OV7670这个摄像头,也是并口的

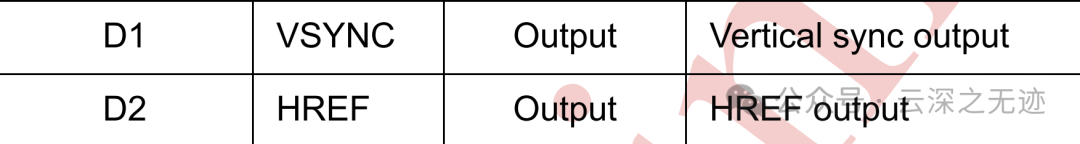

这个是两个同步线,HREF也就是HSYNC,但是不这样写

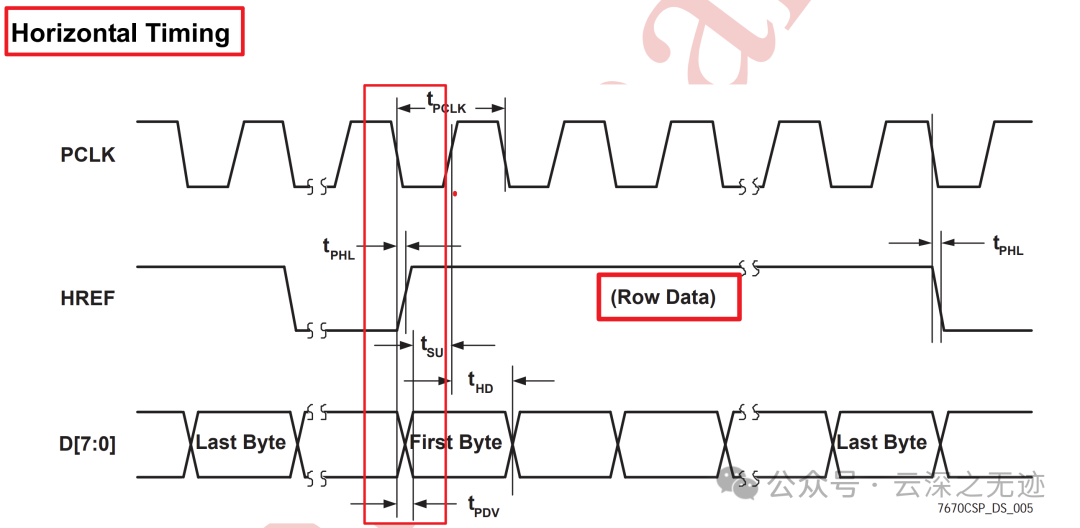

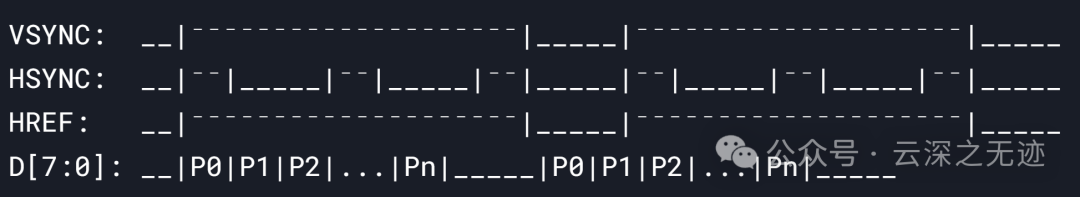

一个时序图

行同步:HSYNC 信号用于指示一行图像的开始和结束。

行频控制:通过 HSYNC 信号的频率控制视频的行频。

高电平有效:在 HSYNC 信号为高电平时,表示一行图像的开始。

低电平有效:在 HSYNC 信号为低电平时,表示一行图像的结束。

周期:HSYNC 信号的周期决定了视频的行频。例如,1080p 视频的行频为 67.5 kHz。

H这个时序拉高的时候,一行开始,下面的D(数据),开始传输,第一个字节,最后是拉低,一行完事。

HSYNC: __|‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾|_____|‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾|_____|<--- 一行图像 --->| |<--- 下一行图像 --->|

帧同步:VSYNC 信号用于指示一帧图像的开始和结束。

帧率控制:通过 VSYNC 信号的频率控制视频的帧率。高电平有效:在 VSYNC 信号为高电平时,表示一帧图像的开始。

低电平有效:在 VSYNC 信号为低电平时,表示一帧图像的结束。

周期:VSYNC 信号的周期决定了视频的帧率。

例如,60 Hz 的帧率对应 VSYNC 周期为 16.67 ms。

我们这里就知道了,图像是一帧一帧的,然后一帧的内部又是一行一行的,这就是最基本的时序,也是VGA时序的基础。

就是这样

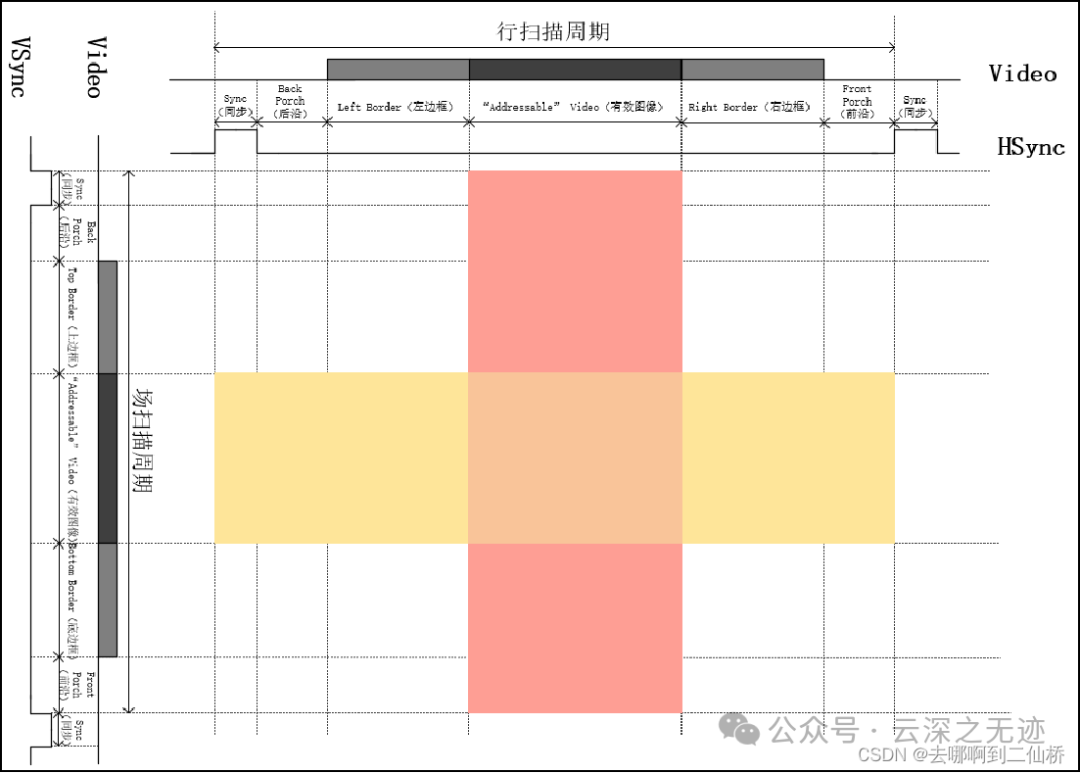

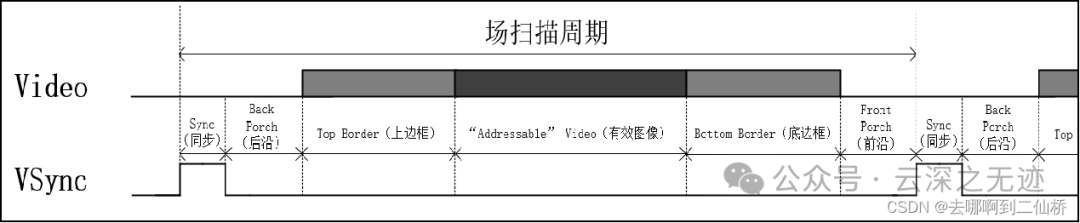

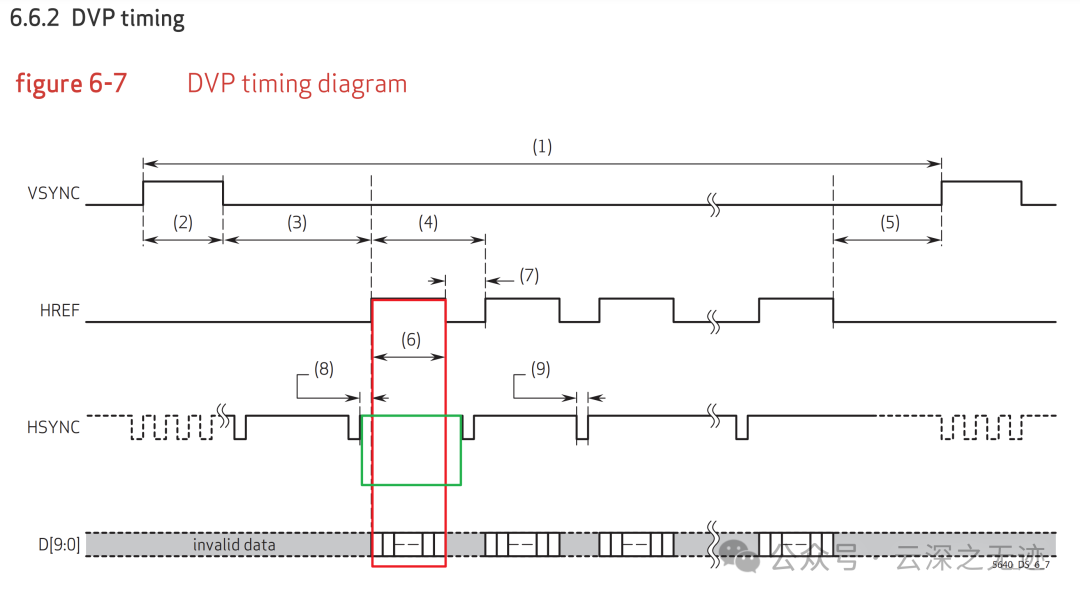

这是我找到全网最好的一个时序图

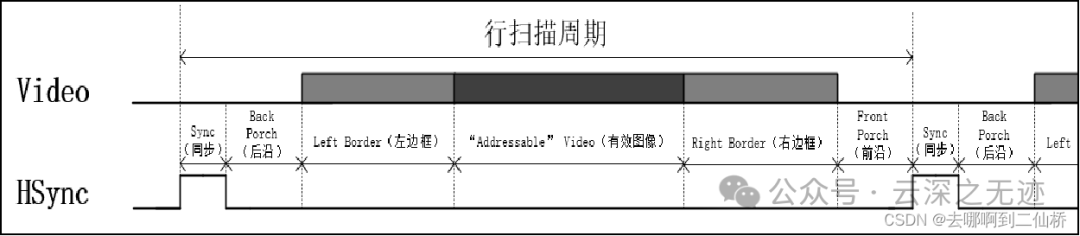

我们看一行的

信号来了以后,叫同步,然后是一个叫后沿的东西,接着说边框,这才是有效数据,后面是对称的。

一场就是一帧,竖着的

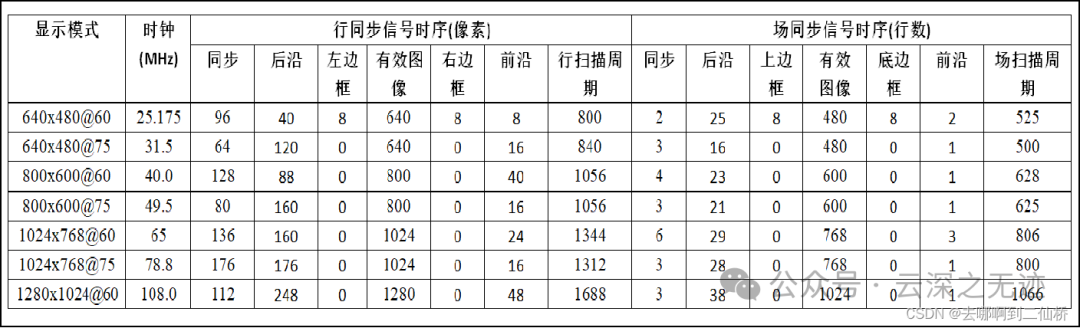

所以有着详细的时钟信息

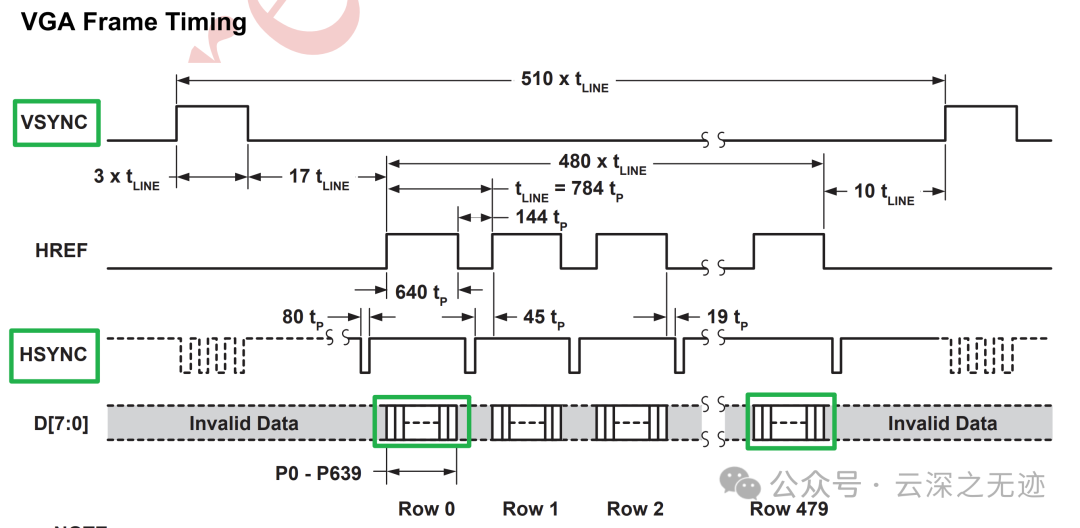

所以继续看摄像头里面的VGA时序

首先出现的是VSNYC(Vertical Sync,垂直同步信号)的信号,图像开始,但是数据这段是没有用的,所以看到是空数据。

然后是HSYNC,行数据同步信号,拉高的时候,看数据信号,一行开始发送,发到479,也就是一共480.

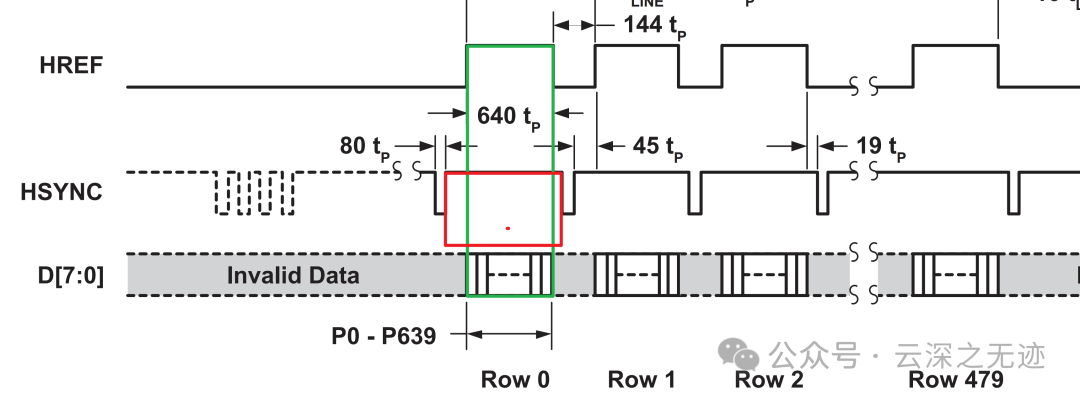

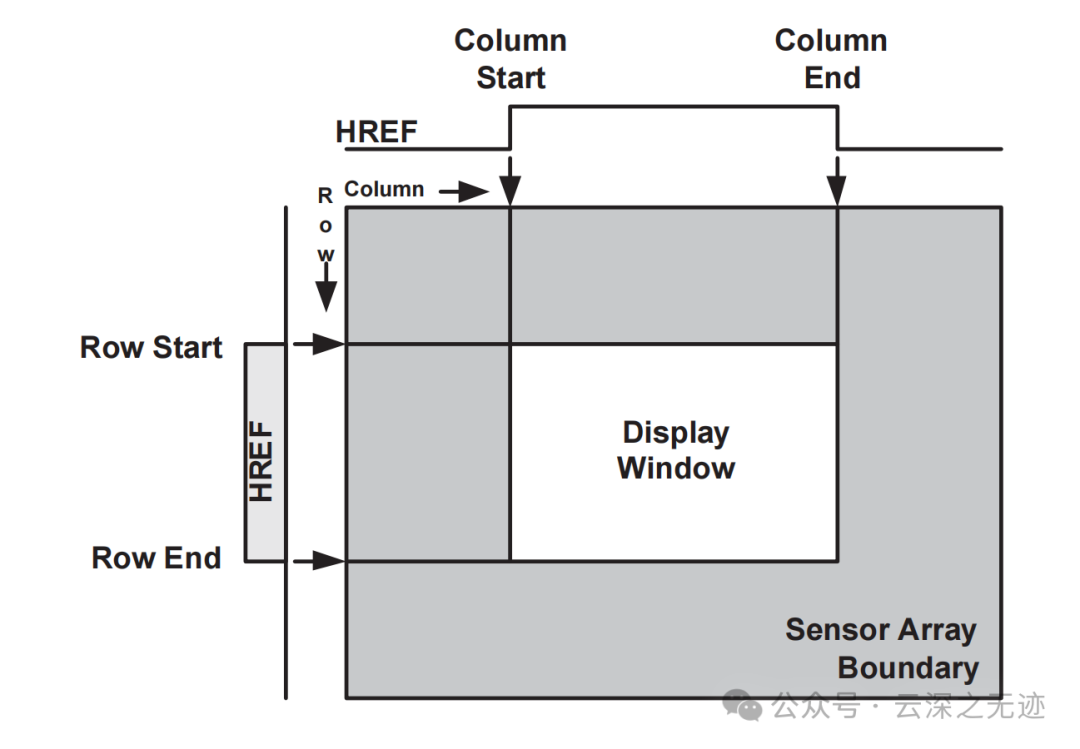

这个HREF指示一行图像中有效数据的开始和结束。

HREF这个信号更加的精密

HREF 的有效宽度通常小于 HSYNC 的有效宽度,因为一行图像中可能包含无效的消隐区域。也就是什么边框,边沿。

这个图就完美的说明了HREF是什么东西

懂了

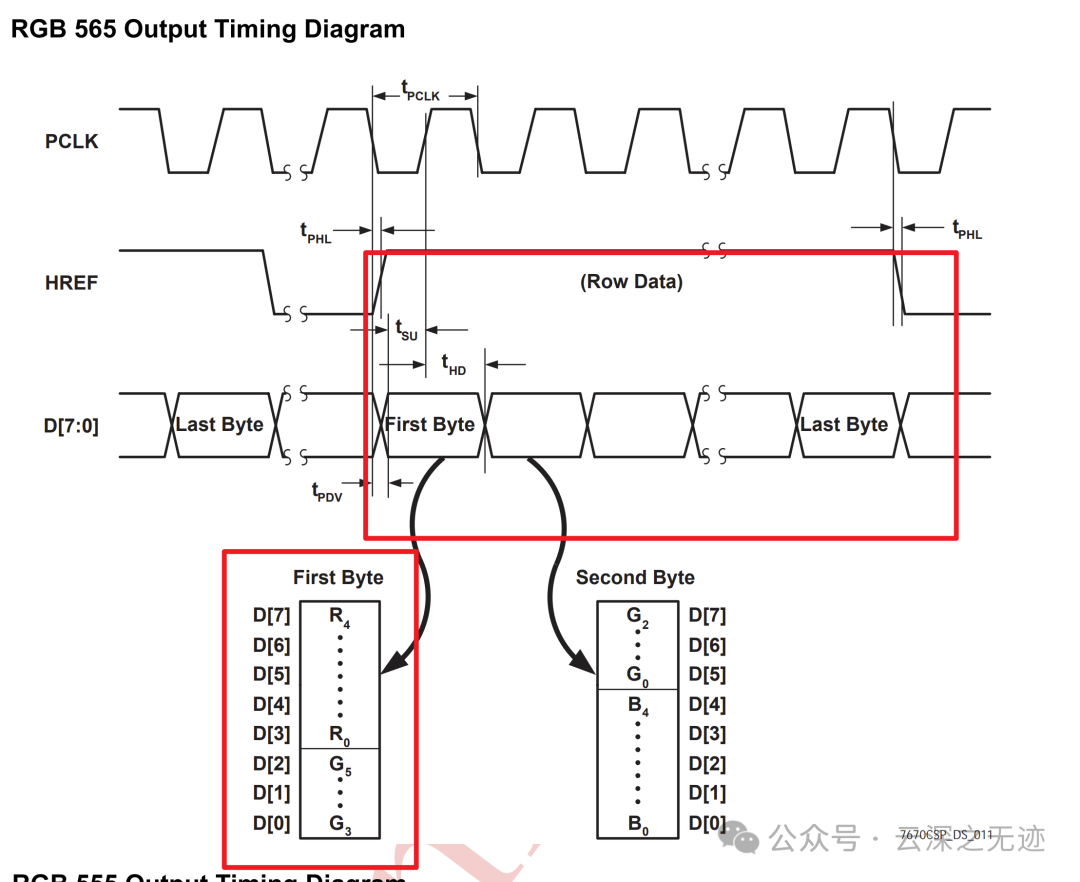

我们也知道这个摄像头可以输出RGB,也就是颜色数组的模式,G就是6位。

在HREF拉高的时候,一行开始传输,第一个字节,就是8位的颜色数据,R4-0,然后还有三位,传输G的高三位,下一个字节内是G松下的低三位和B的5位,就这样。

也就是说,八个线上面传输的就是这样的数据。

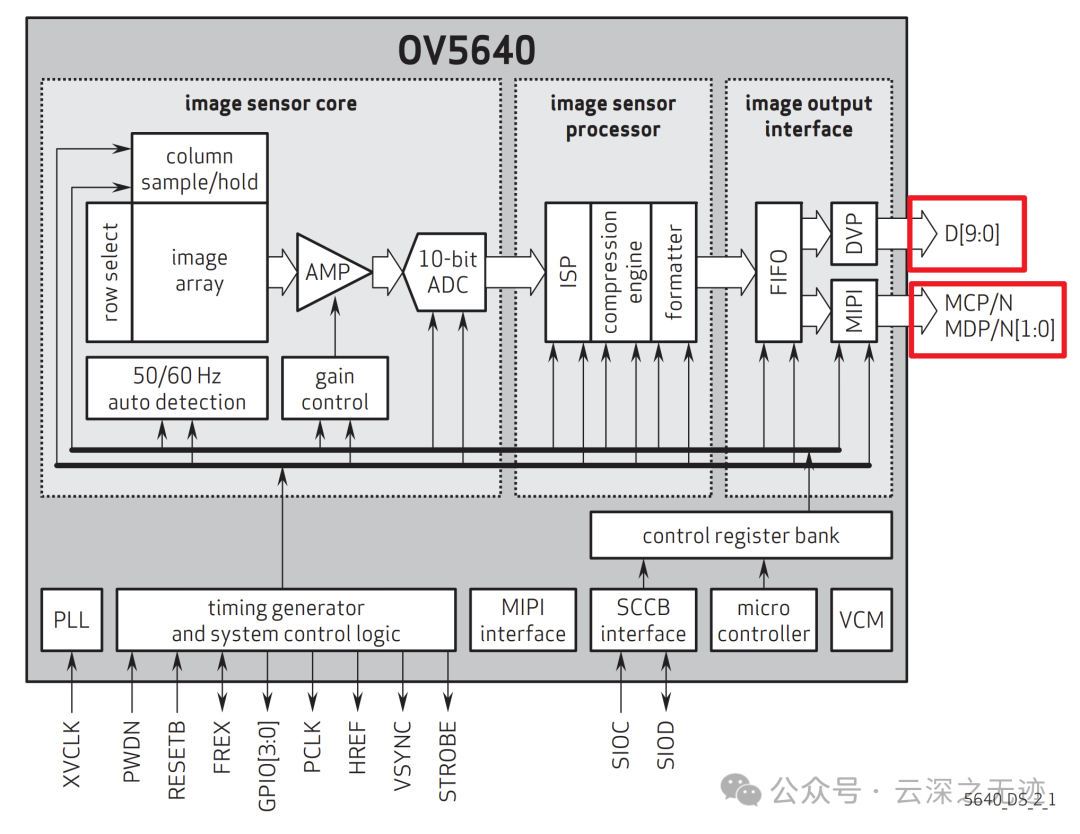

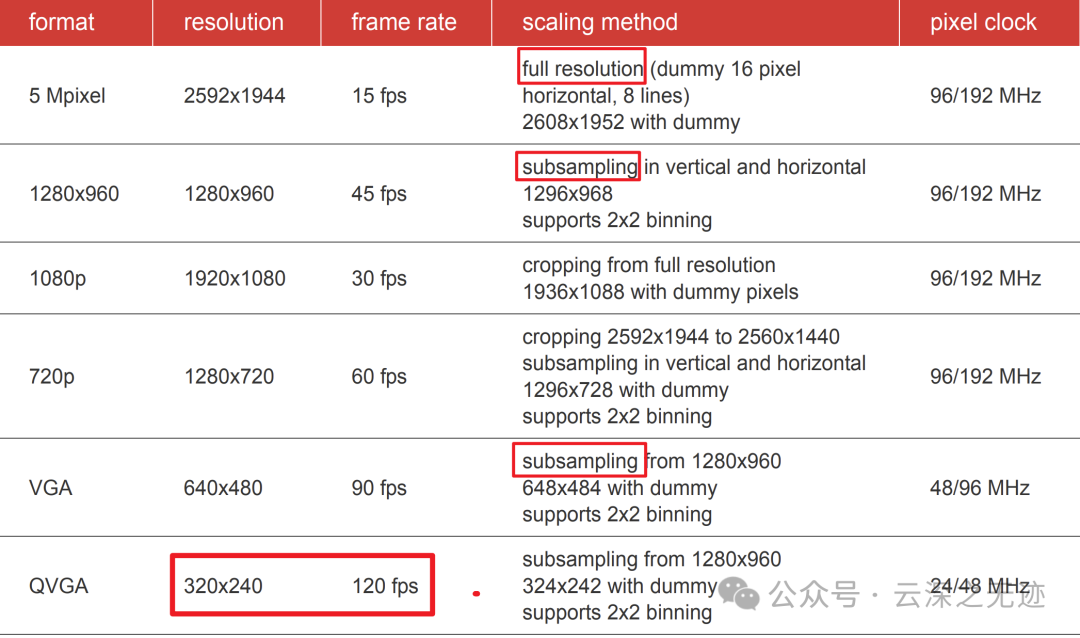

还有的摄像头是DVP和MIPI都有的

可以全速输出

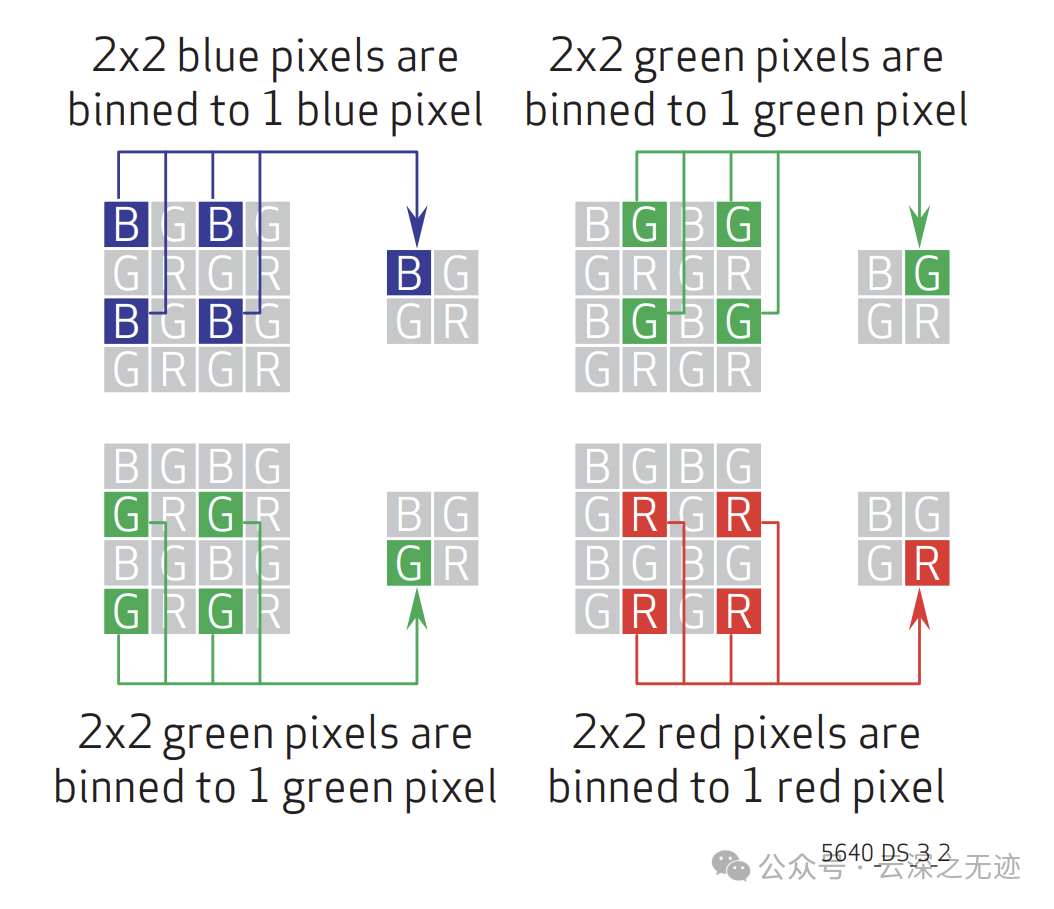

小于规定的都是降采样的,也叫子采样。

具体就是这样的,四个变一个

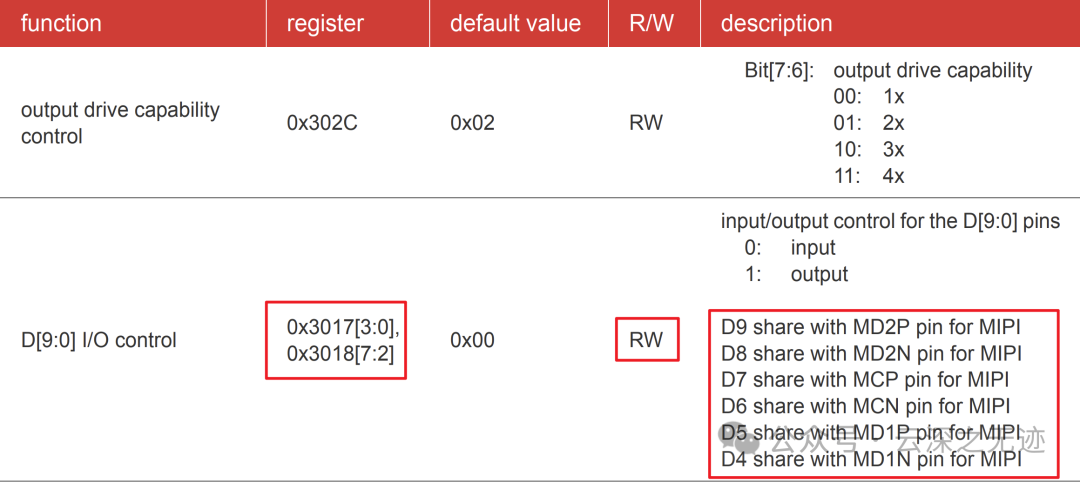

可以通过IIC控制输出的情况

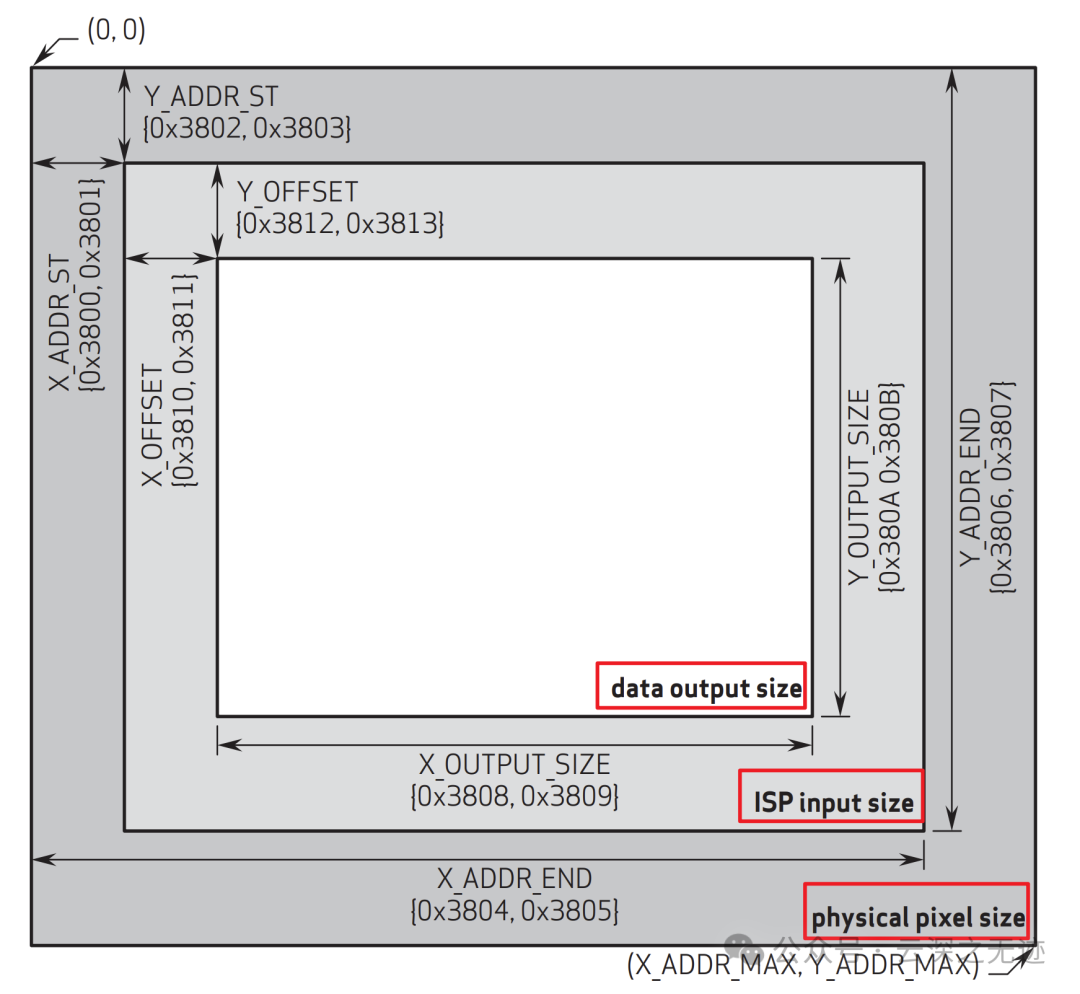

这个图像输出是物理的,ISP输入的,以及真实的数据输出的。

DVP我感觉和VGA是一样的

DVP是摄像头的数字结构

D[7:0]:8 位并行数据信号,传输像素数据。

RGB:模拟红、绿、蓝信号,传输像素颜色信息。这就是区别

这个是VGA的接口

https://blog.csdn.net/qq_51264805/article/details/122305848