接触了几个搞FPGA的大佬,可恶,觉得酷死了。本来想搞个国产的FPGA学习的,后来看了看资料,感觉还是用老牌的东西上吧。

AMD的Xilinx软件一看就很先进,哈哈哈哈,装好120G,哈哈哈,MLGB的,不知道装了个啥。

ZYNQ倒是看起来很屌,但是初学就应该搞点简单的:

安排

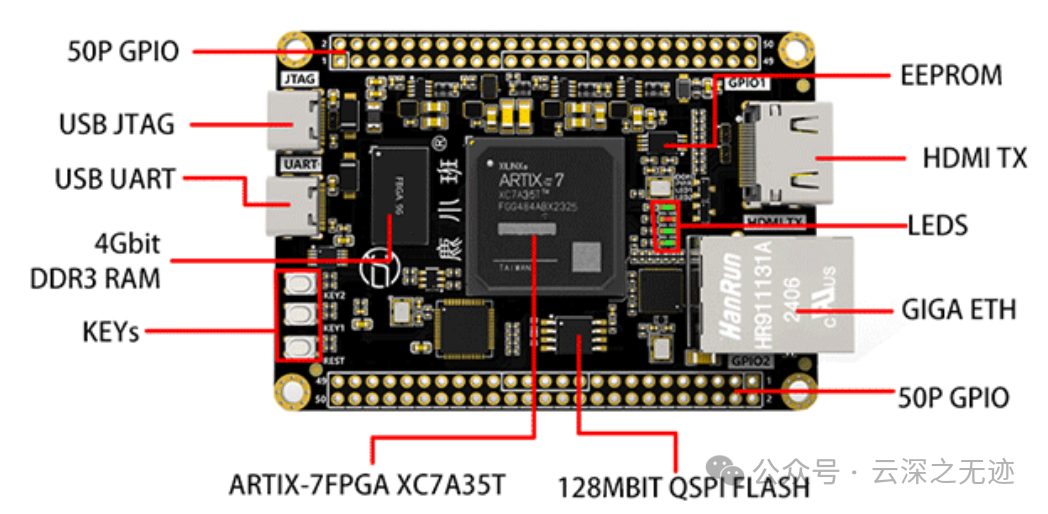

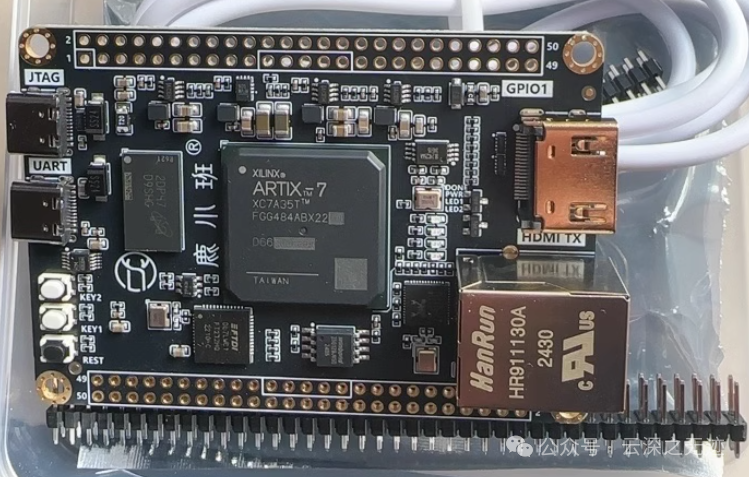

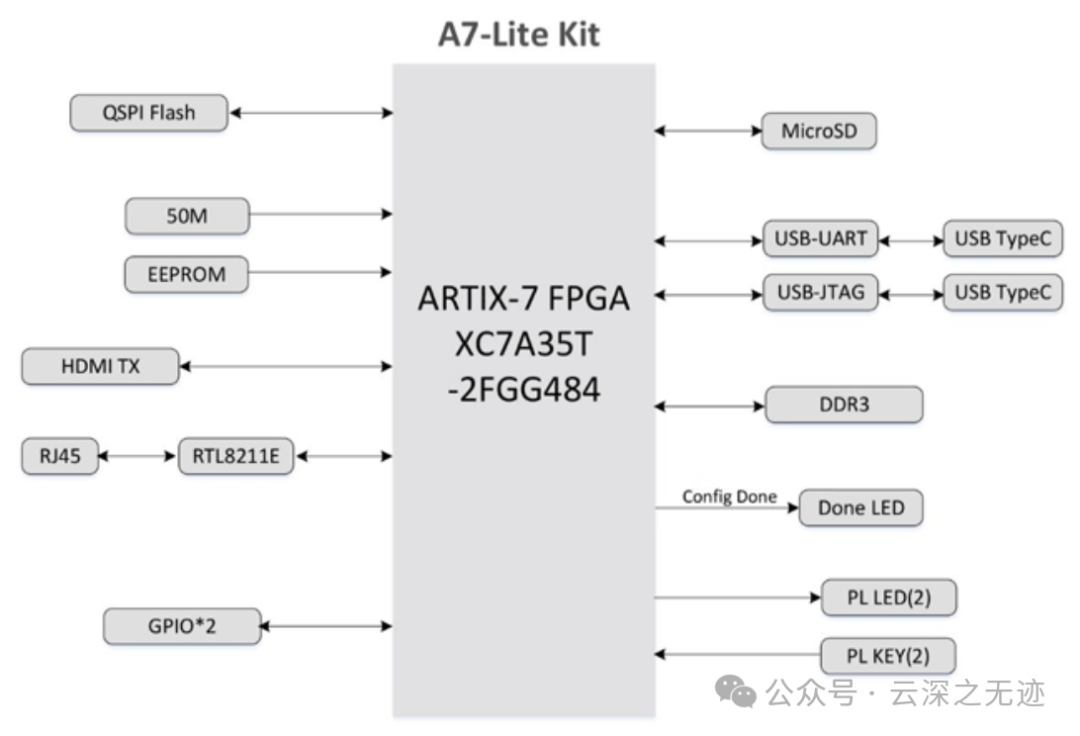

买了这个

偷的图,这大芯片

接口也齐全

不介绍了,现在开始记录一些步骤。

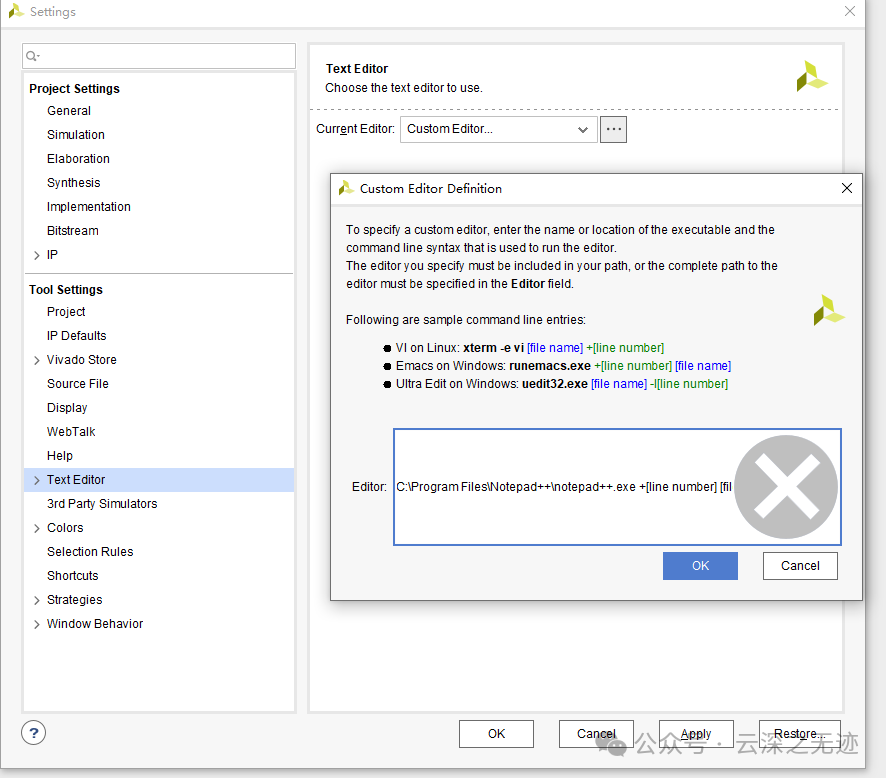

自带的编辑器不好用,需要notepad++:

配置一下

先打开一个文件

会自动生成一个模块,没想到补全的功能还挺好用

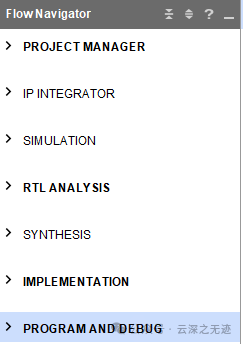

这个软件的操作体验非常好,整个体验就是把这个东西都点亮

先综合,前面写的几个都是组合逻辑

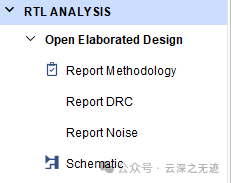

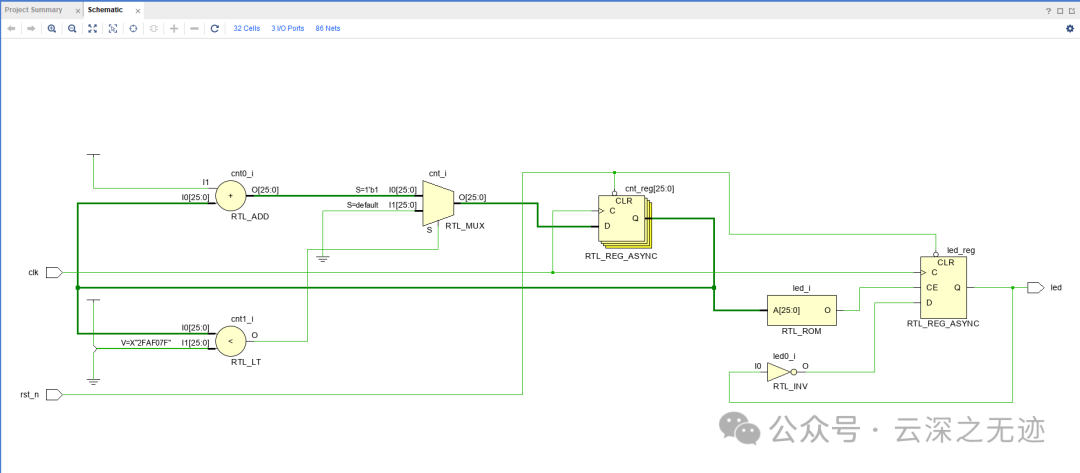

然后无误的话就出现了这个RTL的描述,也就是我们的编程语句换成高级一点。

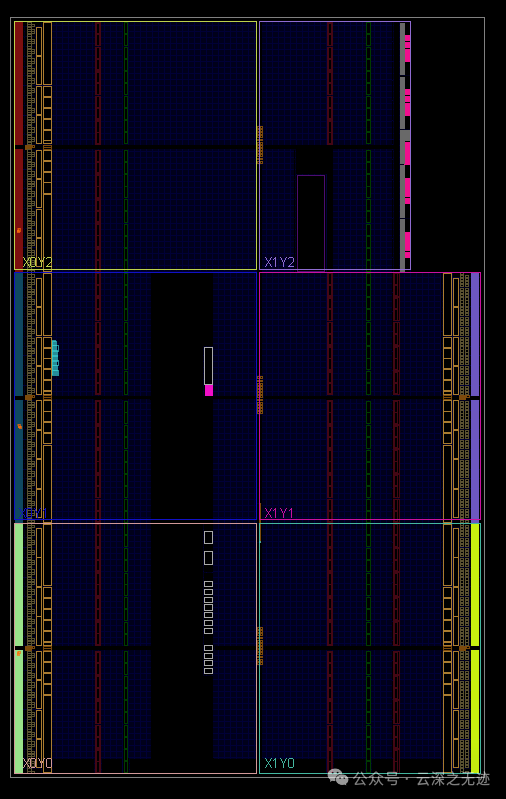

现在我们还需要把上面的逻辑映射成更小的FPGA里面的小块,这里逻辑很简单。

就上面一点点,每次看这种东西都很震撼,这么小,这么精密

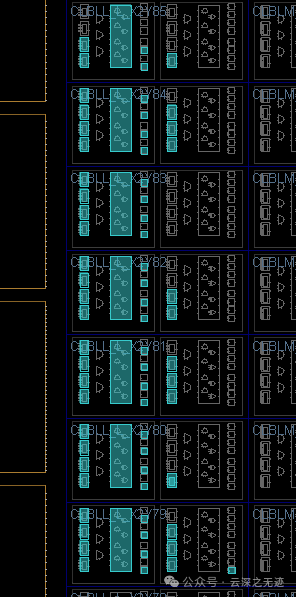

放大一点

看清楚没有

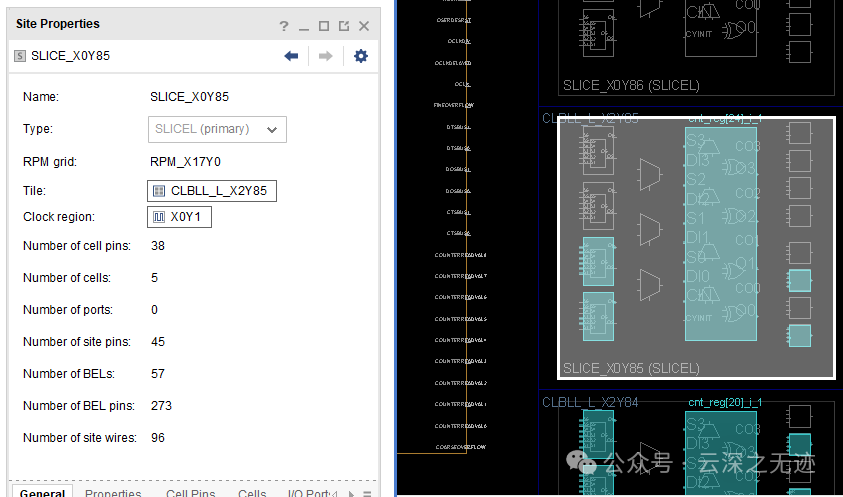

在机内对应的位置在这里,这个是一个块

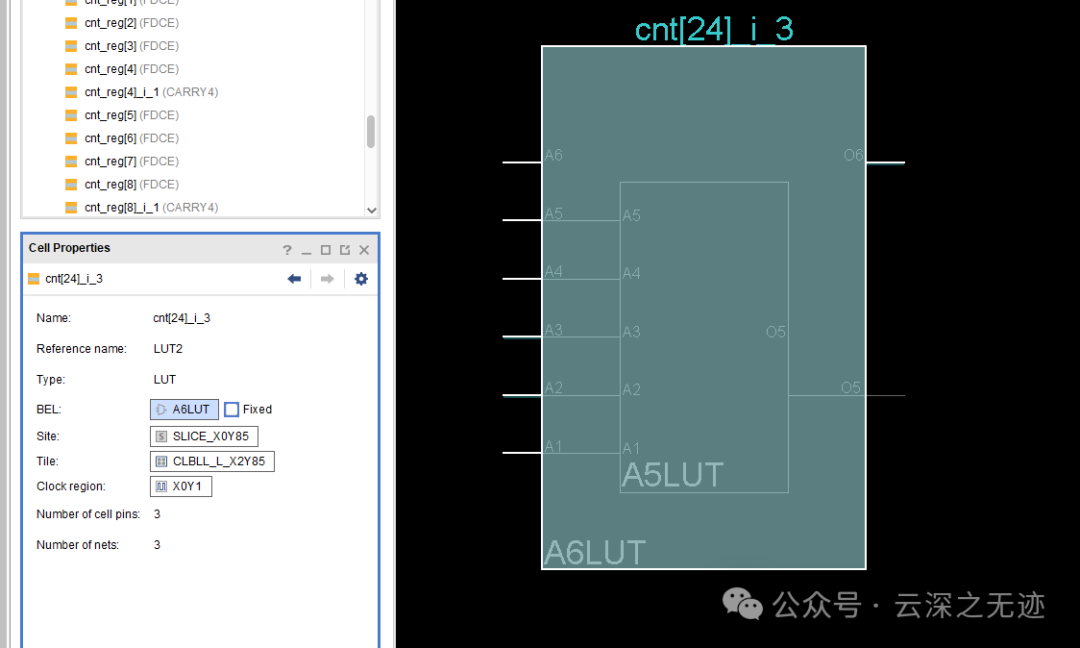

可以放大到LUT的这种程度

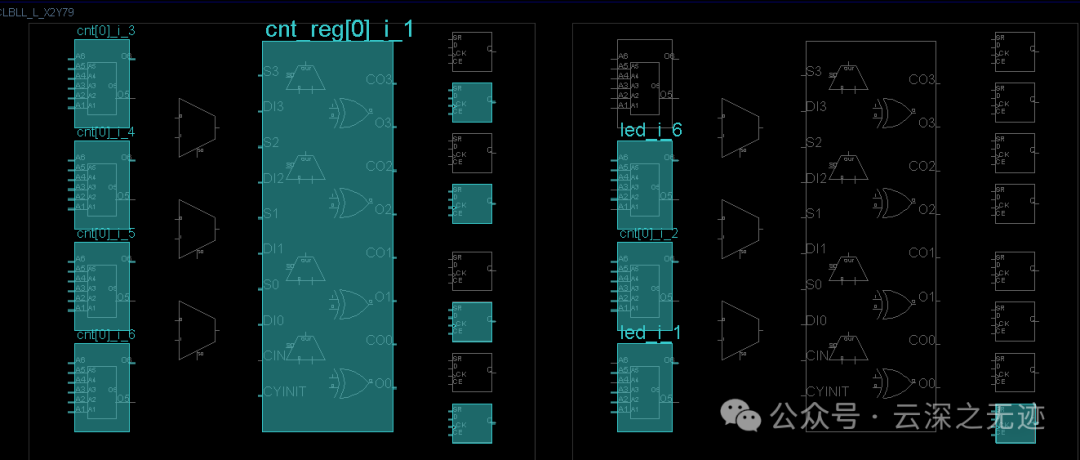

上面是在物理结构里面的样子,我们也可以切换成原理图的样子

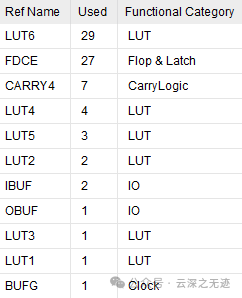

对应着真实的资源

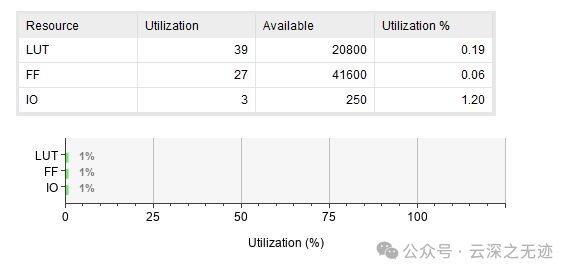

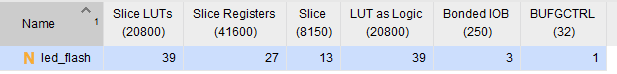

这步就可以统计资源用量啦

这些

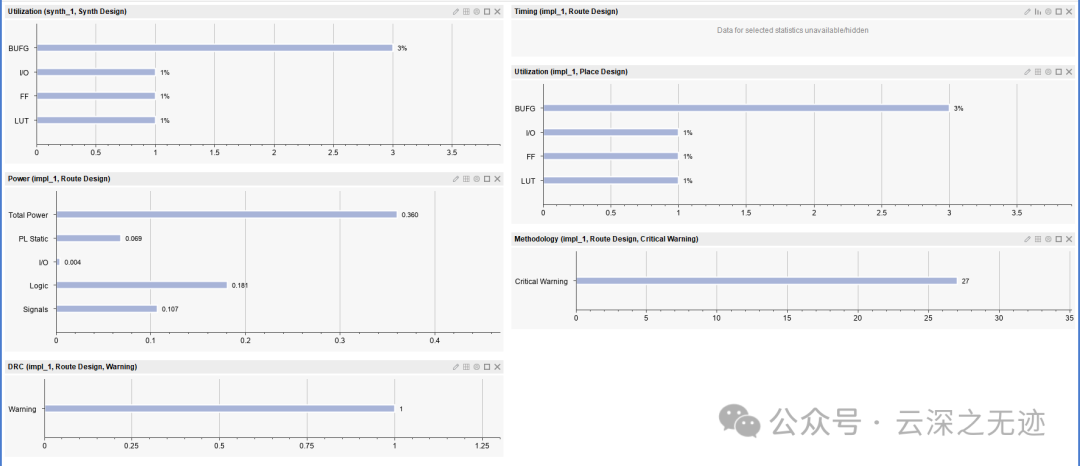

用了挺少的

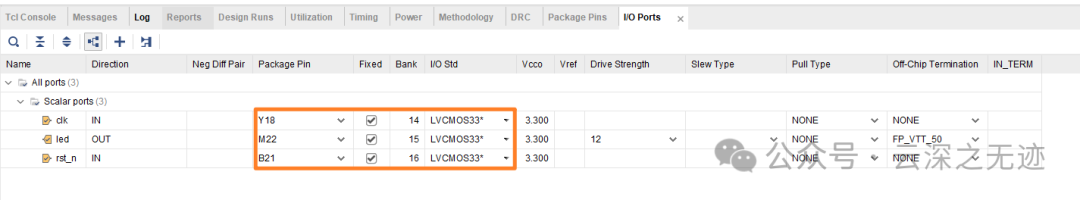

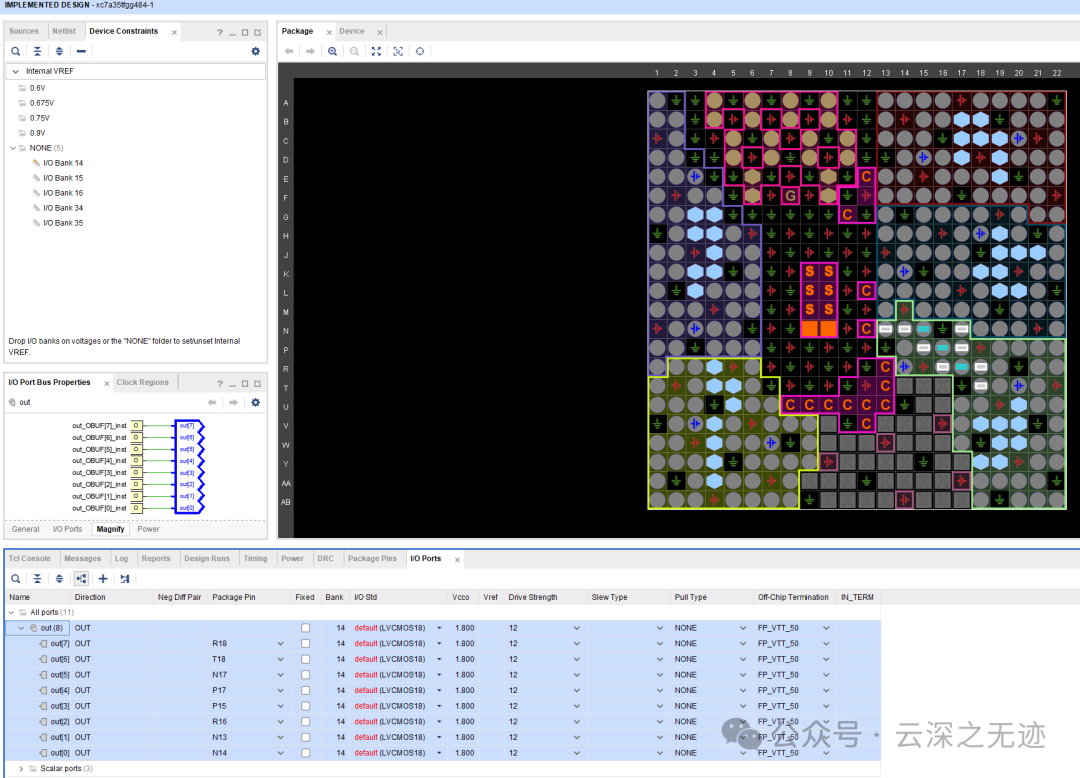

接下来的工作是物理约束,就是要把里面的引脚对应在物理的引脚上面:

就是这玩意

先可视化的操一下

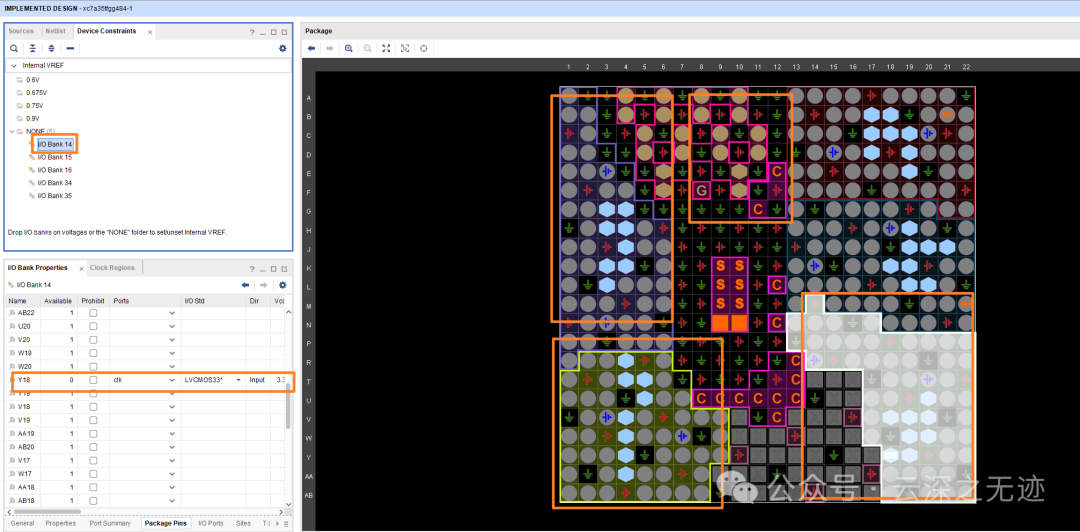

这就是按照Bank分块的IO脚

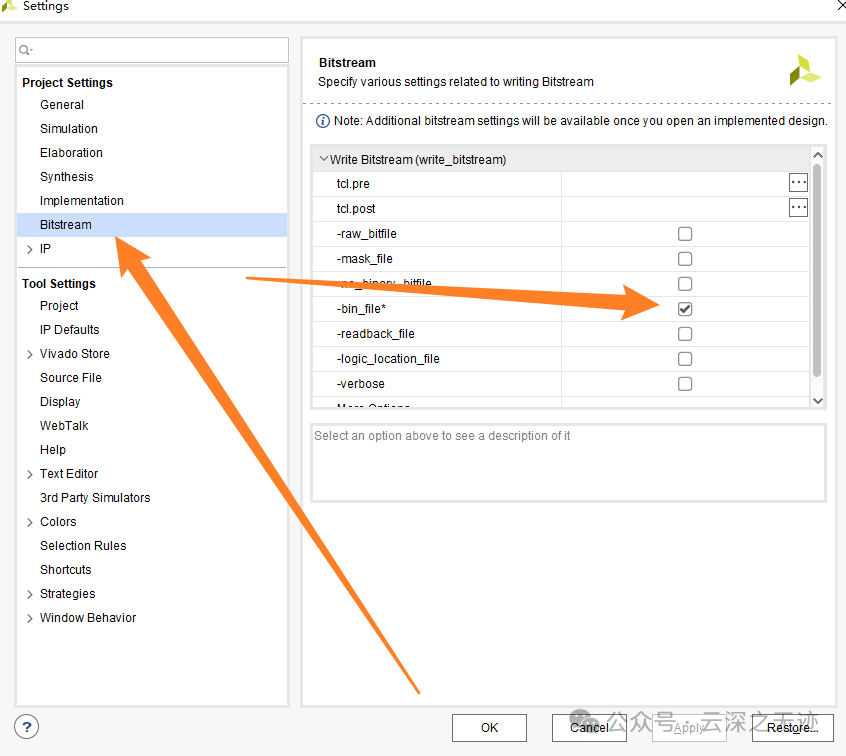

最后就是烧录,默认是不长久保存的

需要在这里开启

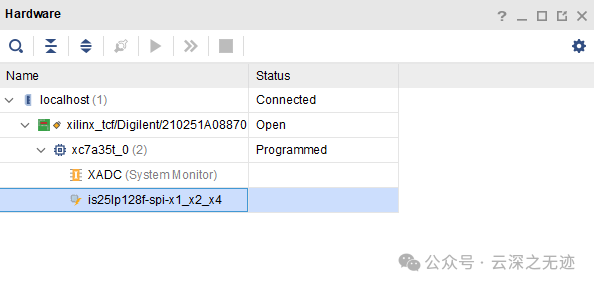

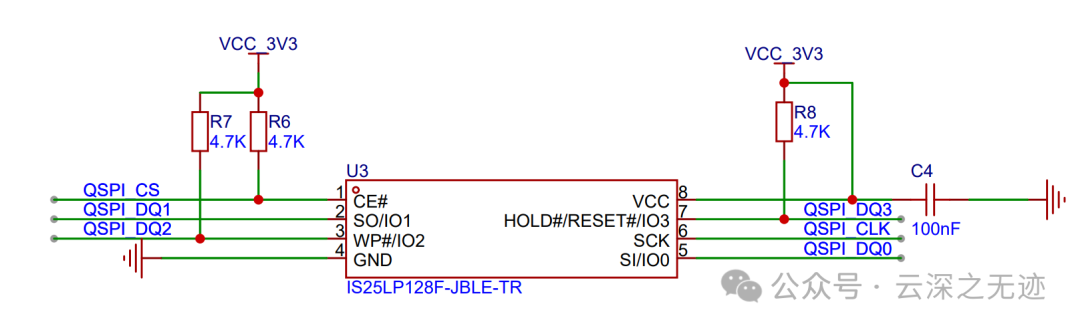

放FLASH的话,需要知道自己的型号

jlc设计的板子

这个

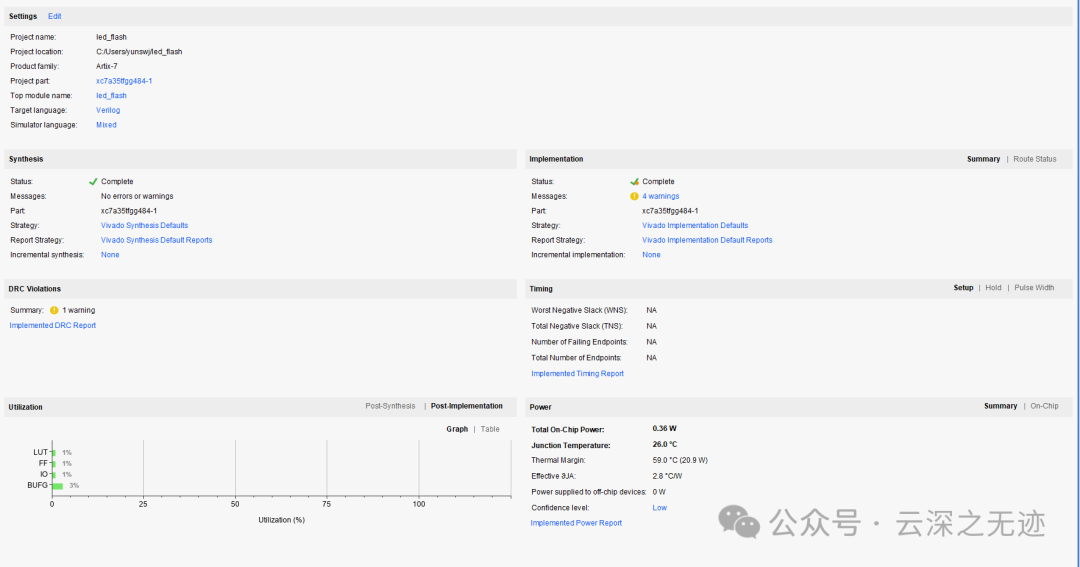

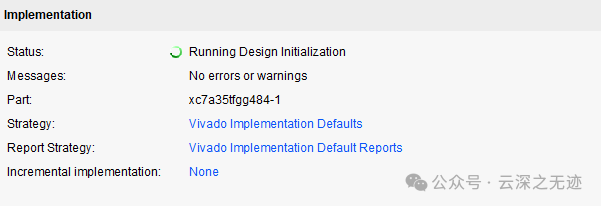

在主页可以对这个项目有清晰的了解,后面的步骤很耗时,所以在这里都可以实时的看见运行情况。

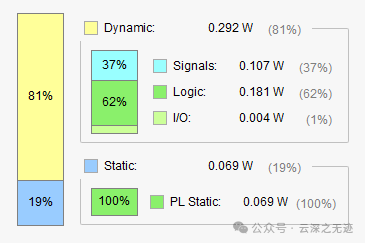

功率

因为没有时序约束,所以这里没有体现

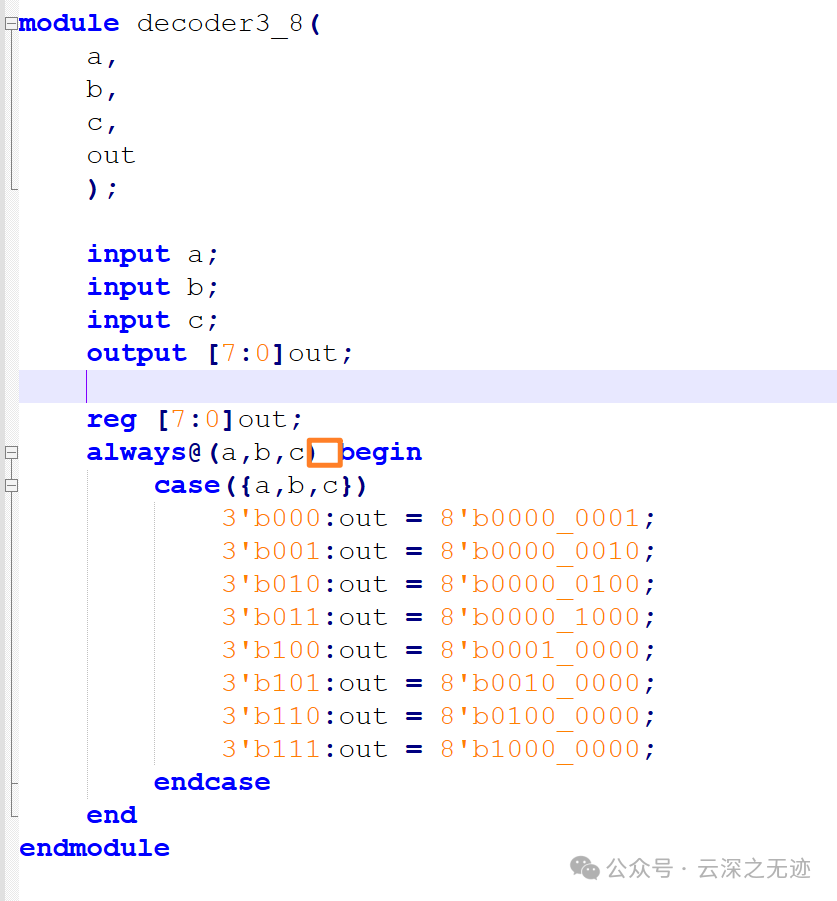

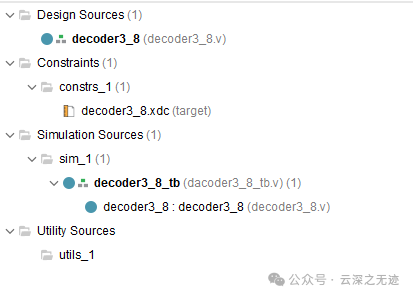

写一个38译码器:

现在问题还是语法不熟悉,错误多,逻辑很简单。

always这里需要一个空格

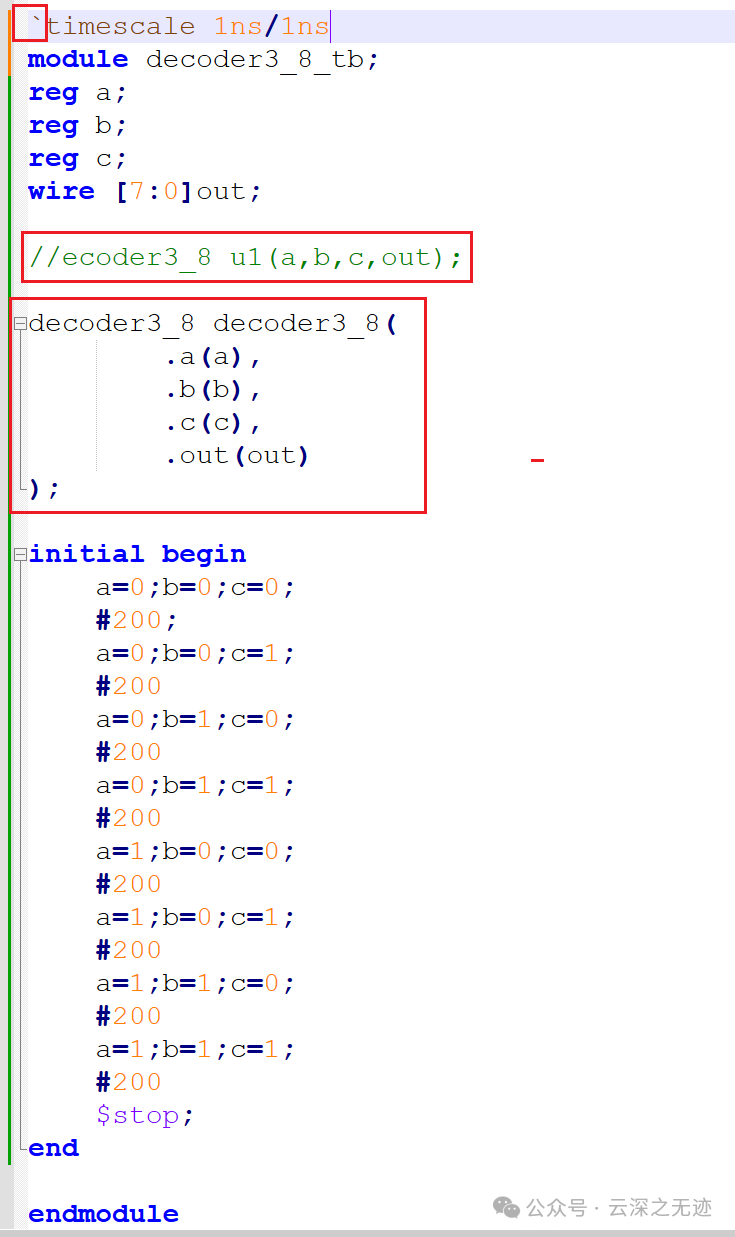

这个是仿真文件

实例化的方法有两种,用我写的这种多,无关顺序。

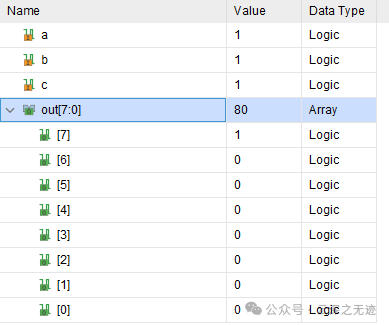

所有的信号

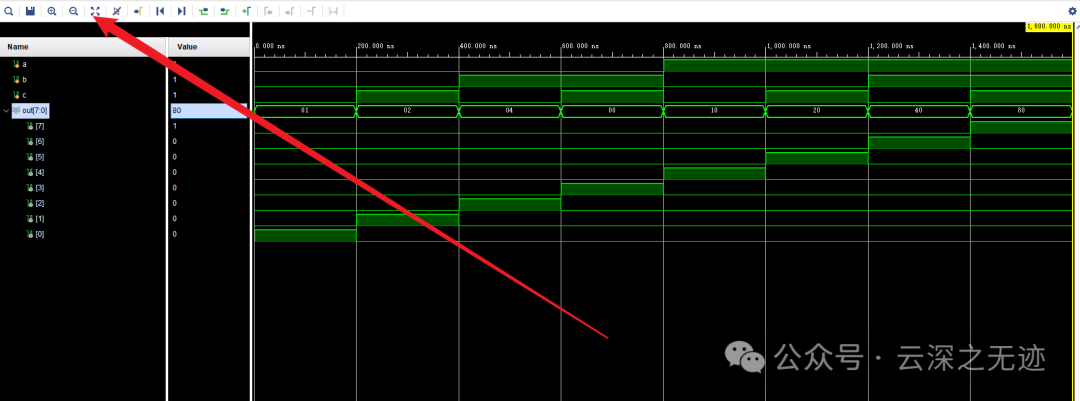

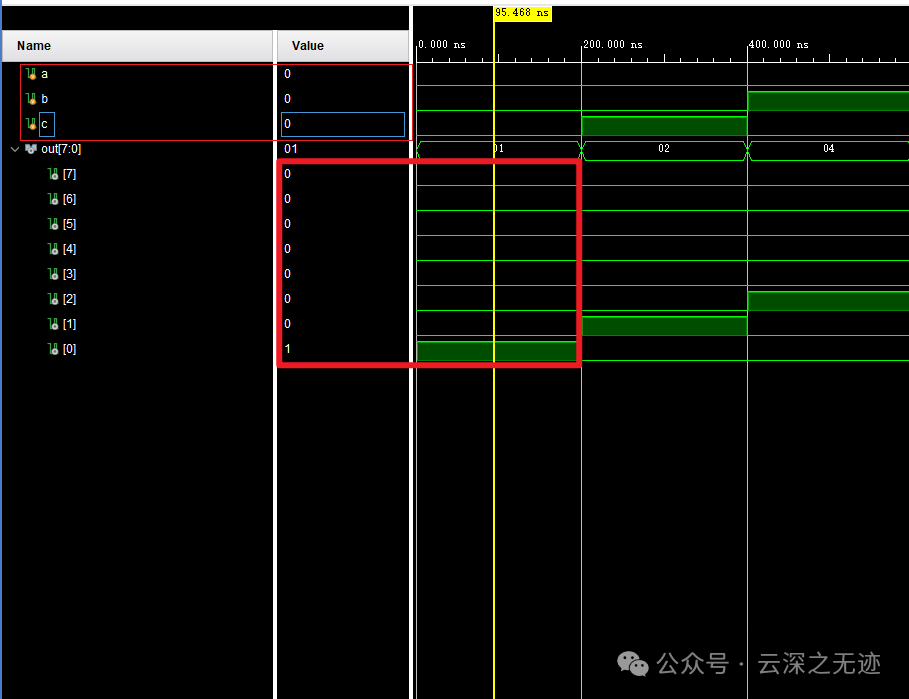

自动匹配屏幕大小

需要把这个标尺放在这里,看前面的真值表

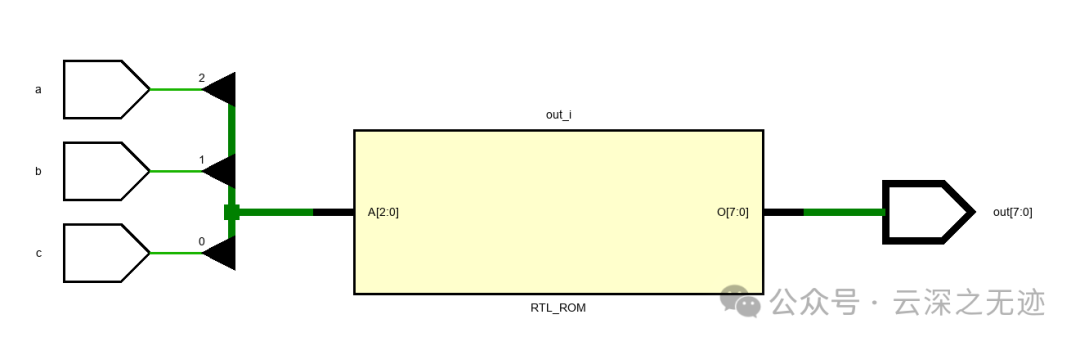

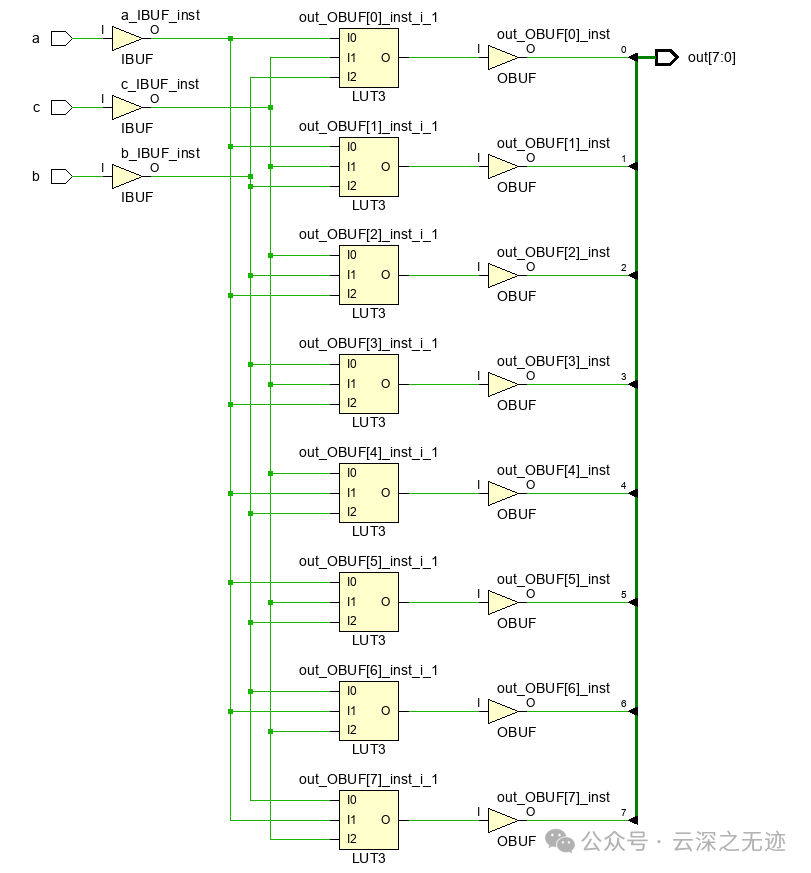

38译码器的RTL,看起来是对的

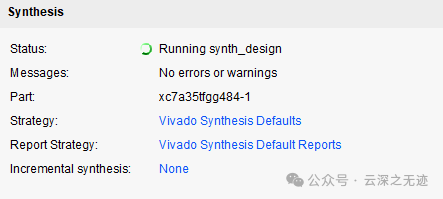

在主页都是可以看到目前的执行情况

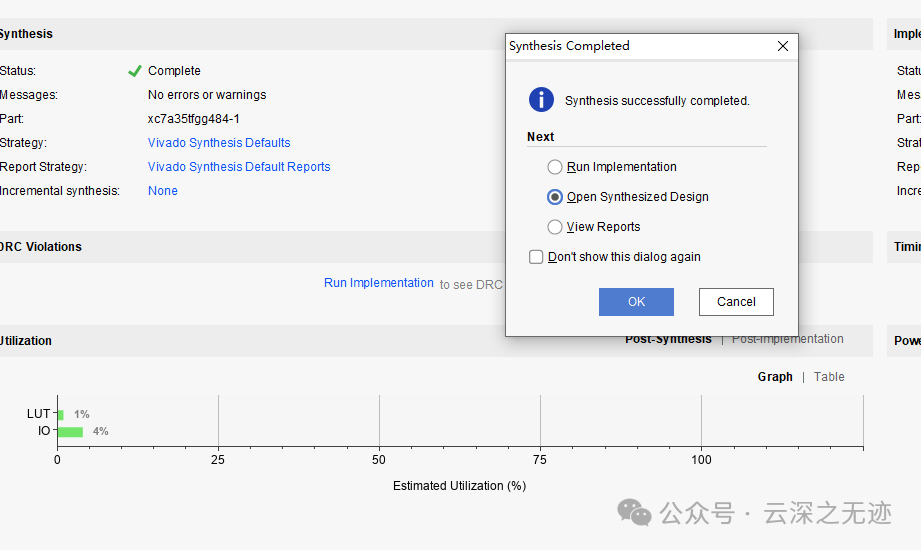

完事以后会提醒你的

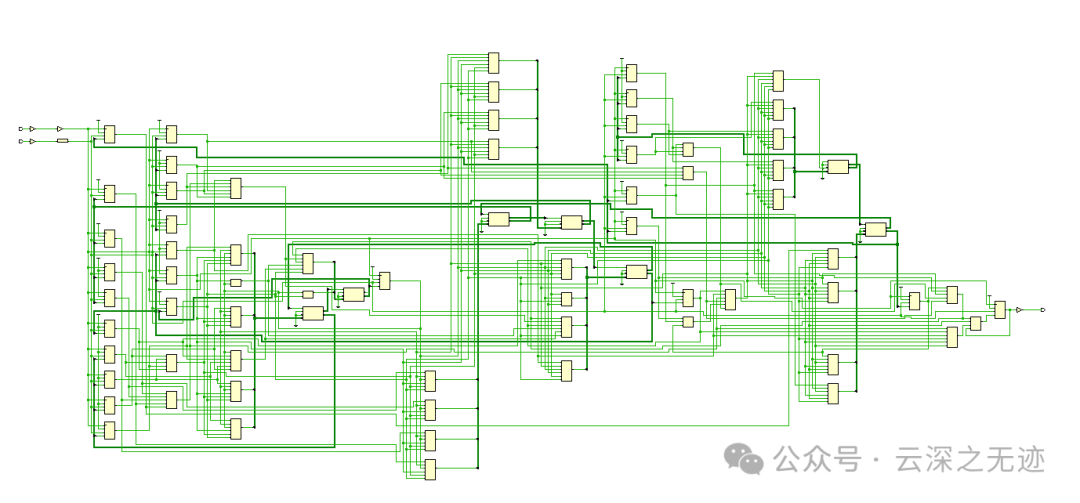

很难相信,我写出来的。。。这个事上面的原理图

这个是物理的综合,明显感觉更加的耗费时间

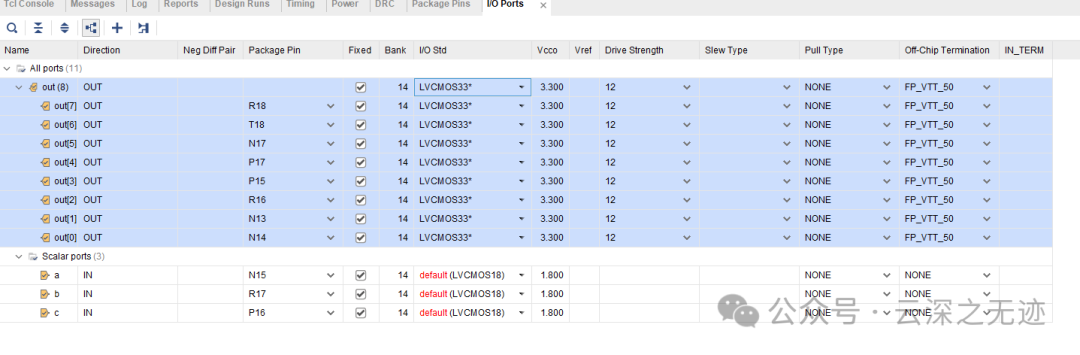

然后步骤和上面是一样的

全是CMOS33

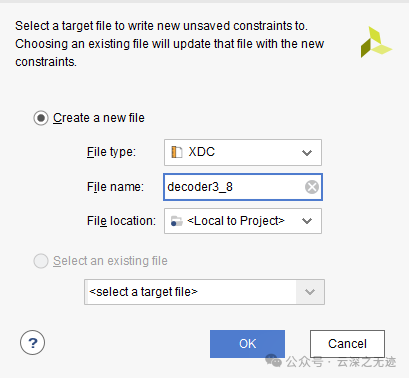

在引脚映射的页面,需要保存一下

大概就是这样的

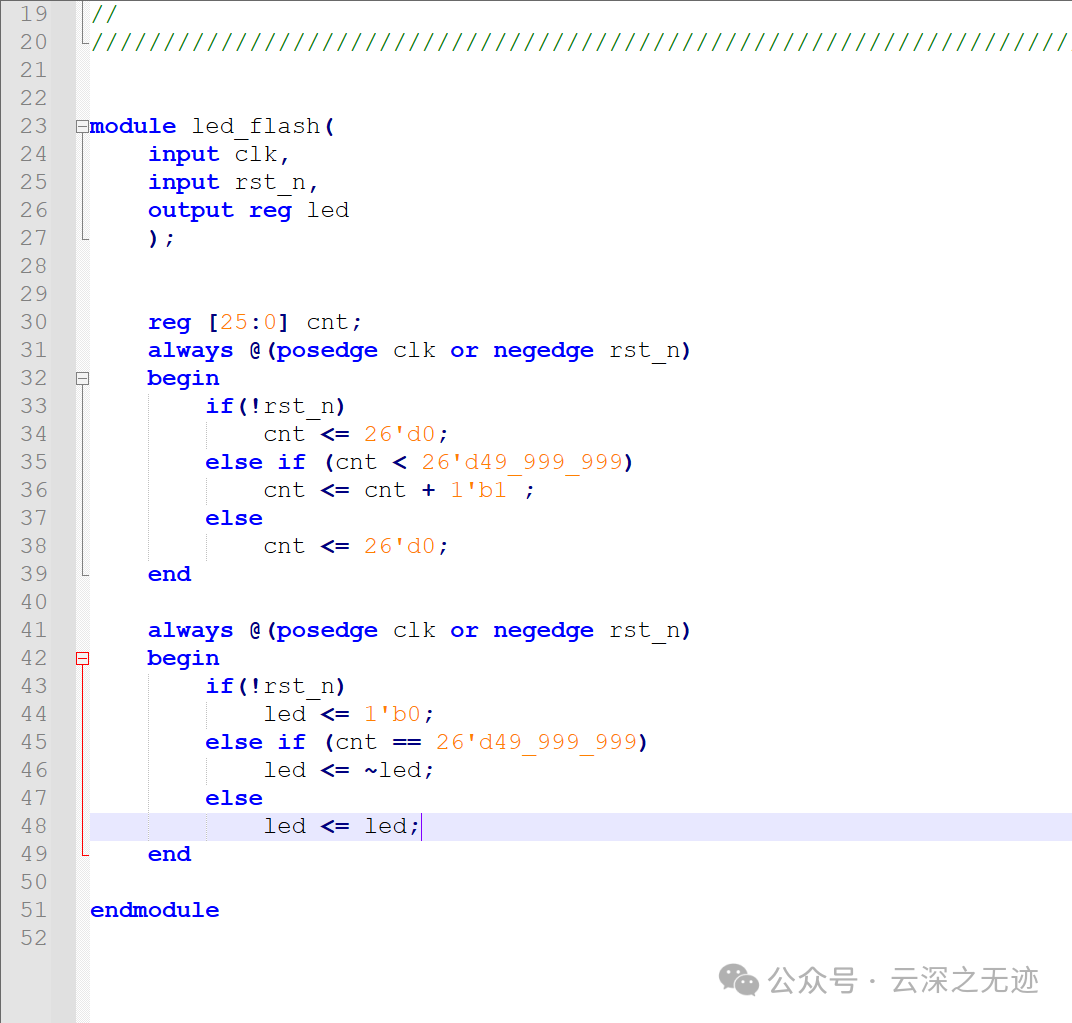

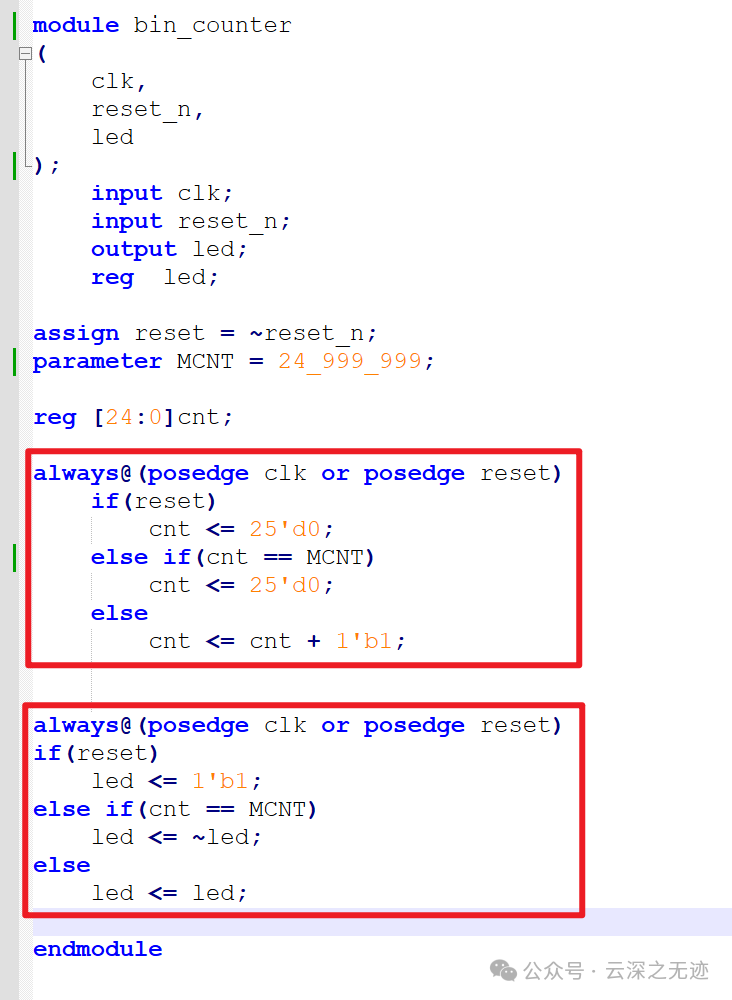

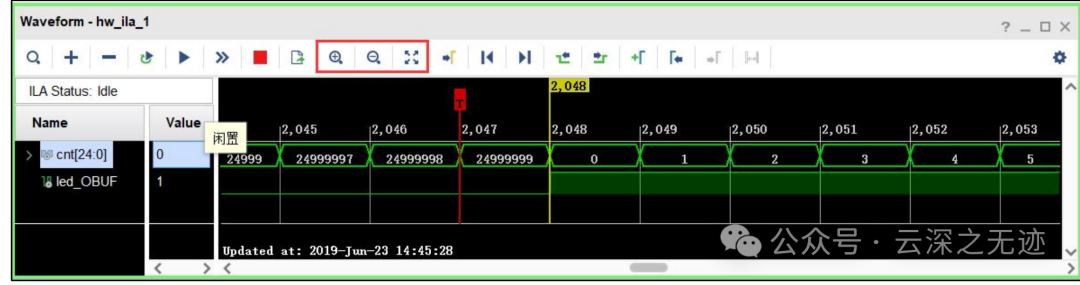

这是一个计数器,属于时序电路,不过我这个写的emmmmm,倒是不报错,就是时序不对。

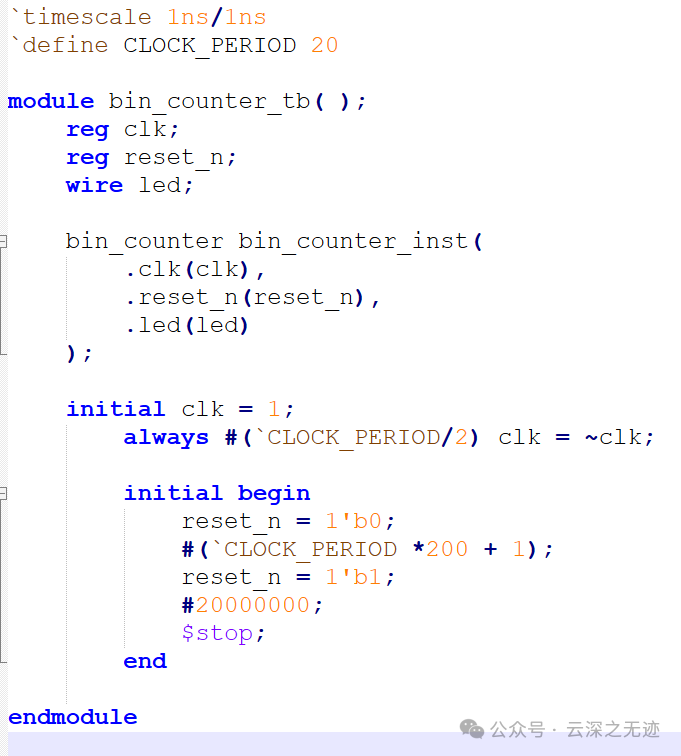

这是仿真文件

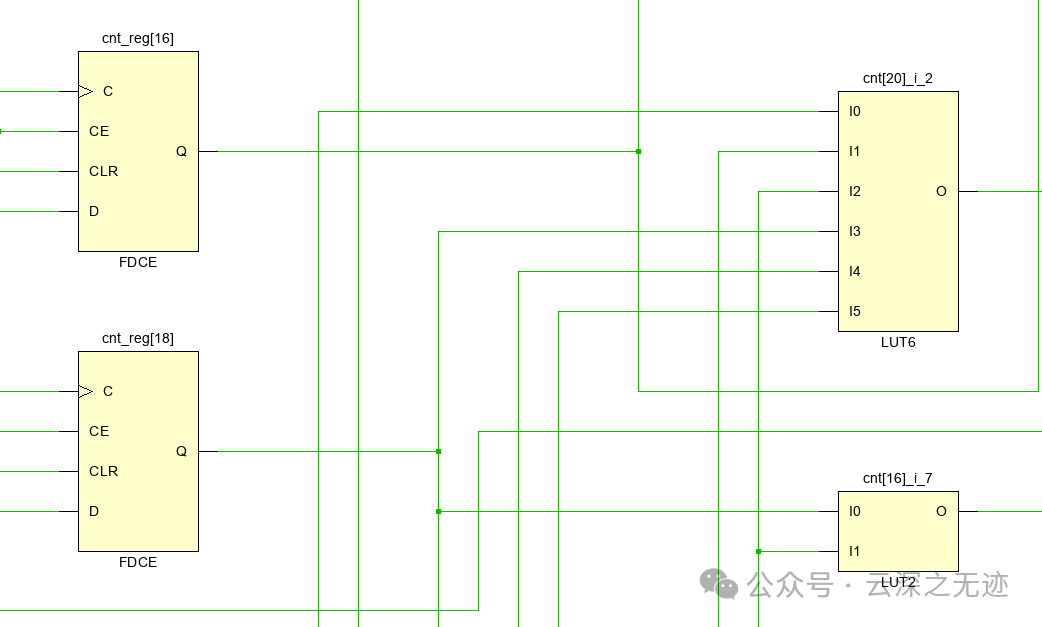

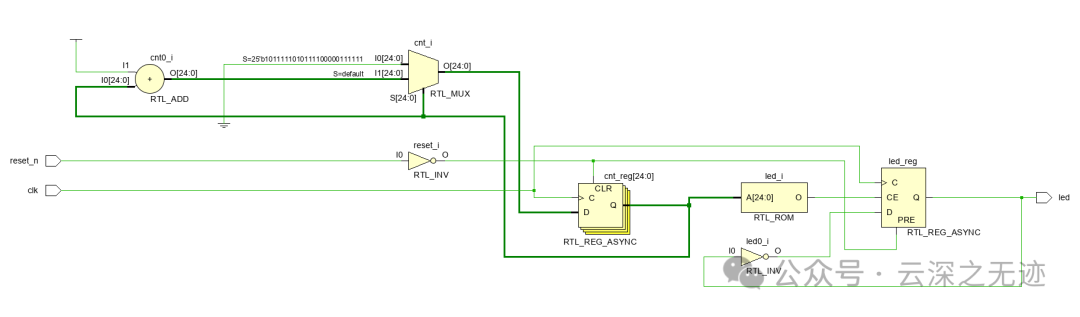

RTL的电路

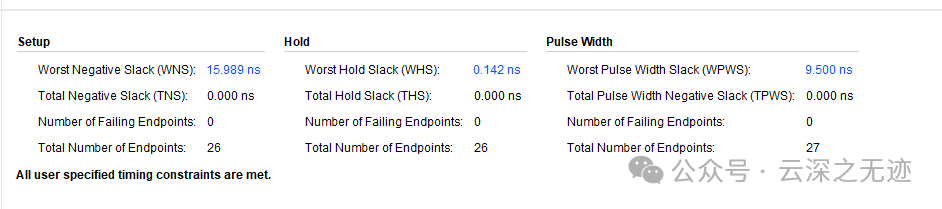

因为加了时钟,我没截图,这个是时钟报告

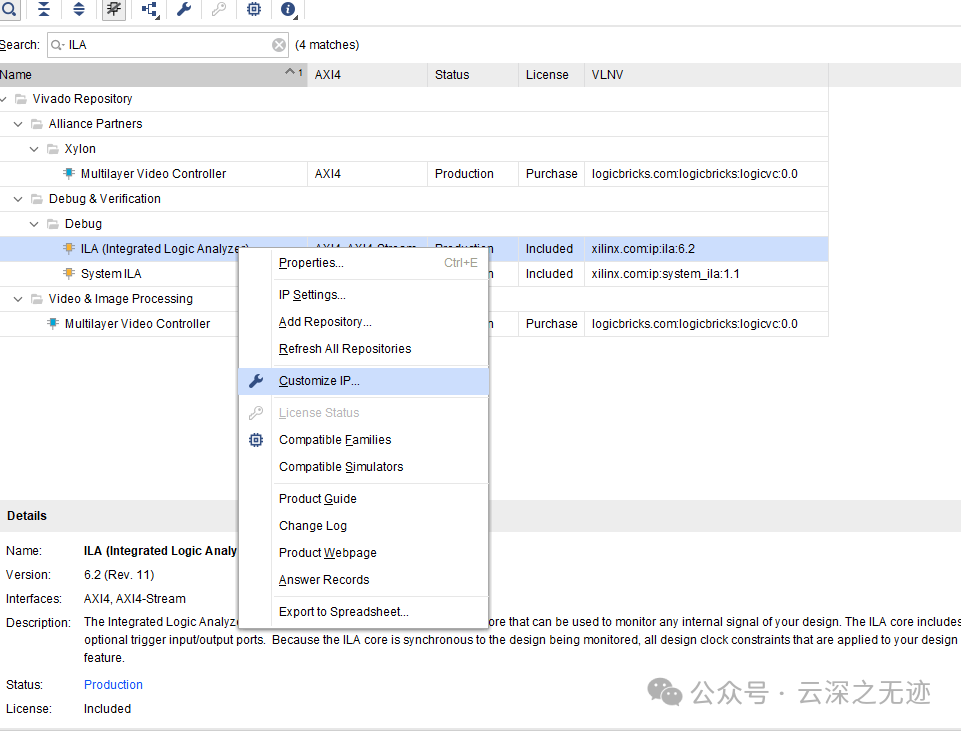

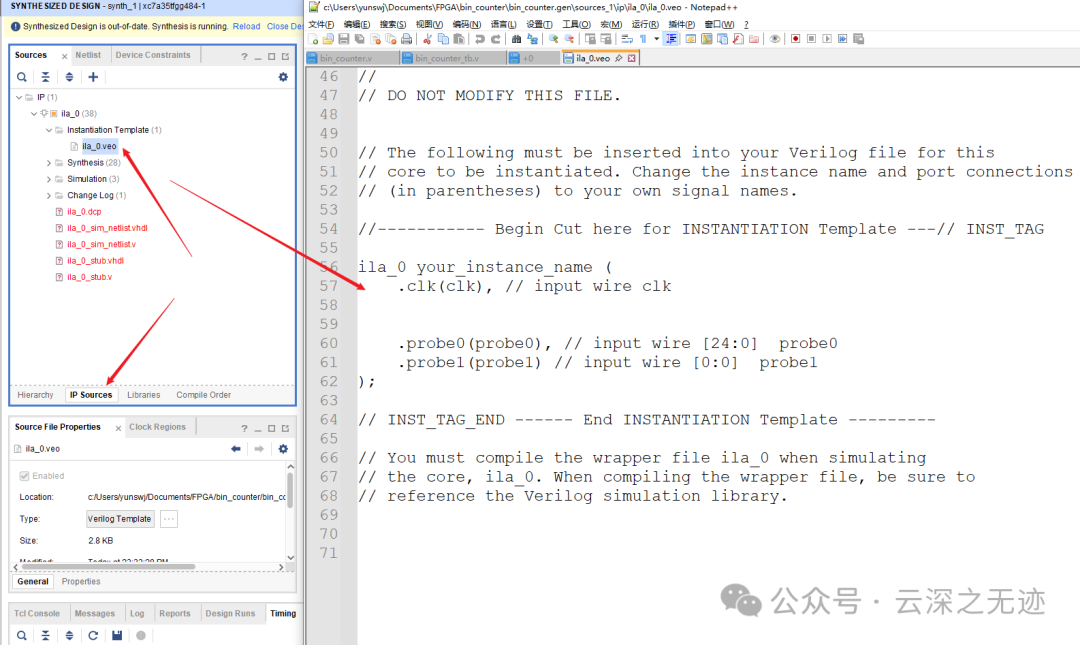

当然了,也可以使用IP,ILA这个东西是一个在线的逻辑分析仪

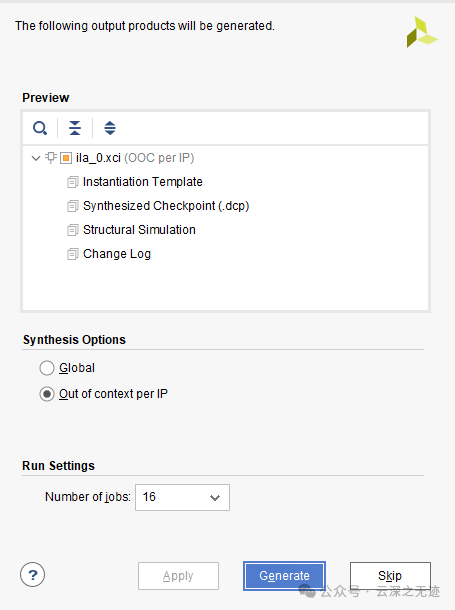

生成

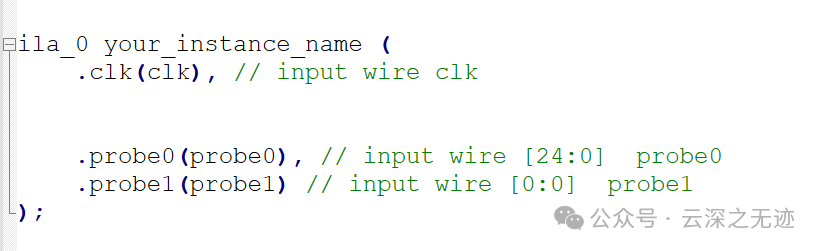

双击打开demo,复制出来

在自己的模块里面例化一下

按照小梅哥的教程学的,他的是2018的版本,我是2021,差不多,不过也有些不一样。写的非常详细,感谢前辈奉献。

FPGA写下来居然觉得比MCU好学,一个MCU拿来得看半天数据手册,参考手册啥的,还有demo。

反而FPGA有种大道没型的感觉。大多数教程都是组合逻辑说说,下面配一个时序电路,就是我文中的。后面马上开始串口。和所有的技术一样,只有动起来,实践才知道,坑是有多少。