(本文编译自ElectronicDesign)

碳纳米管为防止极紫外光刻(EUV lithography)中的缺陷提供了一种颠覆性的解决方案,助力半导体行业朝着极致微型化发展,并提升芯片可靠性。

在人工智能和高度互联技术普及的推动下,半导体行业规模预计在未来十年内将翻倍。然而,尽管微型芯片作为支撑从智能手机到救生医疗设备等一切产品的微小动力源,正面临着前所未有的需求增长,但它们也面临着迫在眉睫的技术瓶颈。

High-NA EUV光刻面临小型化挑战

晶体管不断向3纳米及更小尺寸发展,这要求其制造过程必须完美无缺。在21世纪前十年,这种惊人的尺寸缩减趋势(90 纳米缩小到7纳米甚至更小)开启了技术进步的新时代。

在过去十年里,我们见证了将500亿个晶体管集成在单个芯片上这一惊人之举。这一成就得益于极紫外(EUV)光刻这一前沿工艺,它使用了EUV光刻。EUV光刻能够印制出比以往精细得多的集成电路(IC)图案,因为其波长(13.5纳米)比传统深紫外(DUV)光刻中常用的波长(193纳米)短得多。

半导体制造领域的领军企业正竞相将这些系统应用于大规模生产中,首批高数值孔径(High-NA)EUV光刻设备已安装到位。这些复杂的设备有望在进一步缩小特征尺寸的同时提高生产效率。然而,尽管取得了这些进步,在EUV光刻过程中实现零缺陷这一关键挑战依然存在。

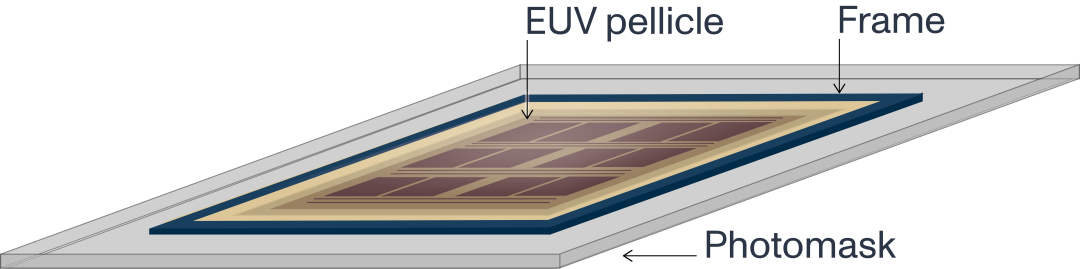

制造商们认识到,EUV光罩保护膜(图1)——一种覆盖在光罩上以防止其沾染污染物的薄而透明的薄膜——对于克服这一障碍至关重要。EUV光罩保护膜能够在颗粒落到包含芯片蓝图的EUV光罩上之前将其拦截,从而显著降低缺陷率,使行业更接近实现零缺陷的目标。

图1:用于EUV光刻的碳纳米管EUV光罩保护膜和光罩示例。

EUV芯片制造中的缺陷难题

目前,缺陷对芯片的性能和可靠性持续产生负面影响。在芯片制造的每一个步骤中尽量减少误差至关重要。EUV光罩是半导体制造过程中使用的一种高精度模板,用于在硅片上创建复杂图案。它就像一个模板,阻挡硅片的某些区域暴露于EUV光下,从而在硅片上蚀刻出所需的图案。

在初始阶段,甚至在EUV光罩进入光刻机之前,可能会出现三种常见类型的缺陷:表面缺陷,它是众多可见缺陷的主要类型,由分层过程中底层材料暴露所导致。其次,层内可能夹带微小颗粒,这些颗粒可能来自初始材料或在构建过程中的操作。最后,分层过程可能会在光罩表面无意地造成缺陷,这些缺陷可能完全或部分被覆盖。

在下一阶段,光罩也可能产生缺陷,因为EUV光刻机本身可能就是缺陷的来源。光刻机内部的极端条件,如高温和高功率水平,在曝光过程中可能会使光罩产生缺陷。

在高功率EUV光刻过程中,温度接近1000°C,传统的EUV光罩保护膜虽能提供一定保护,但在处理过程中,它们会因热变形或污染物释放等机制而逐渐损坏,这会对光罩和光刻机都造成损害。除此之外,如果由传统金属硅化物制成的光罩保护膜破裂,它们会像玻璃一样破碎,导致不必要的、代价高昂的停机。

碳纳米管(CNT)薄膜在过滤污染物以保护光罩方面表现出色,专为EUV光罩保护膜设计的超薄碳纳米管网络,在保持出色颗粒过滤能力的同时,能最大限度地提高EUV光的透射率,而更厚、更坚固的碳纳米管薄膜还可用作光罩检查中的碎片过滤器。这种特殊技术用于在EUV光罩进入光刻机之前对光罩进行检查。

尽管目前的半导体制造技术已经取得了诸多进步,但防止光罩上有害颗粒造成的缺陷仍然是制造过程中的一大挑战。理想情况下,通过控制和减少杂质的存在,晶圆厂可以提高良率,使芯片性能更加稳定。然而,这一领域的进展一直极为缓慢。

碳纳米管在提升EUV光刻效率中所扮演的角色

近年来,碳纳米管用于EUV光罩保护膜以在EUV光刻过程中保护光罩免受缺陷影响的潜力愈发受到关注。事实上,碳纳米管保护膜是提高EUV光刻良率和性能的关键因素:由于其具有更高的透光率,碳纳米管保护膜预计可将生产效率提高7%至15%,从而推动半导体性能迈向新台阶。

Canatu公司研发了一款用于EUV保护膜的先进碳纳米管薄膜(如图2所示),该薄膜具备一系列独特的性能组合。未涂层的Canatu碳纳米管薄膜在EUV光下具有高透光率(透光率>97%)、极低的杂散光(<0.2%)以及在真空中的高热稳定性(>1500°C)。

图2:碳纳米管可用于EUV保护膜、X射线窗口及其他EUV应用场景。

高透光率意味着更多EUV光能够透过保护膜到达晶圆,从而提高生产效率。低杂散光(散射)特性确保即使是极其微小的图案也能高精度地印制在晶圆上,而不会出现图案变形。高耐热性、化学惰性以及对压力差的高耐受性,保证了基于碳纳米管薄膜的EUV保护膜能够承受下一代高功率光刻机环境中强烈的抽真空和排气循环,同时保持其光学性能。

据阿斯麦(ASML)公司称,最先进的高数值孔径EUV光刻机将采用超过500瓦的高功率水平,提升光学系统聚焦和聚光的能力(即数值孔径[NA]从0.33提升至0.55),实现更高分辨率的成像功能。功率水平的提升直接带来每小时处理晶圆数量(WPH)的增加。例如,400瓦的光源每小时可处理160片晶圆,而500瓦的光源每小时能印制超过185片晶圆。

然而,更高的功率水平和光罩应力会产生高热量负载,这是传统材料无法承受的,可能导致保护膜变形,在其他情况下,甚至会使保护膜像玻璃一样破碎。

正如ASML在2023年国际光学工程学会(SPIE)会议上所提到的,碳纳米管(如图3所示)正成为用于高功率光刻机的EUV保护膜最具潜力的材料。持续开展基于碳纳米管薄膜的EUV保护膜技术研发,对于充分挖掘其潜力至关重要,而且它为芯片制造的未来所带来的前景是不可否认的。

图3:碳纳米管具有诸多特性。

碳纳米管保护膜:助力精密芯片的纯净制造

随着EUV光刻技术给半导体制造业带来的变革,碳纳米管薄膜成为在光罩检查和EUV光刻过程中保护光罩免受污染的理想选择,可确保芯片生产更洁净、更精确。

碳纳米管的卓越特性使其成为适用于EUV光刻的多功能且面向未来的材料,有望减少缺陷,提高良率,并最终实现更小尺寸、更快速度且更可靠芯片的生产,而这些芯片正是我们不断发展的技术领域的基石。

END