在栅氧化层某处存在损坏,栅源时间存在一定程度的虚接,栅(漏)源之间的电流存在泄放路径,导致阈值电压系统显示测试值较大。另外,在测试过程中,如果存在测试错误(如电极断等),复测数据即使合格,测试过程也会对芯片造成一定的损伤。

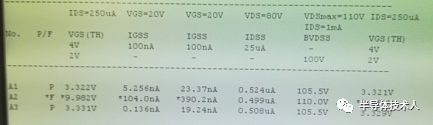

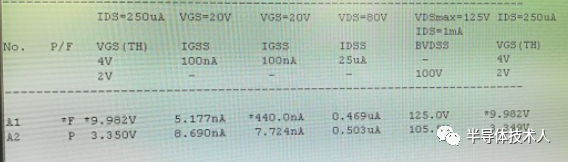

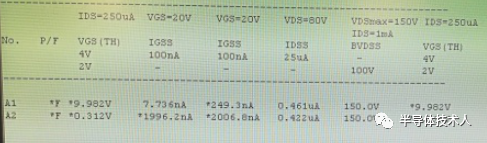

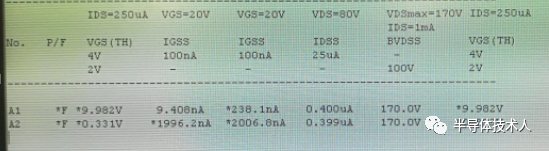

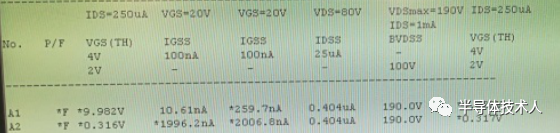

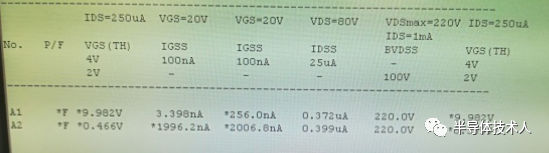

取PMOSFET(型号IRFCXXXX)芯片,利用系统测试得到的原始数据如图1所示,A1为正常测试,表明该芯片电参数正常,A2为将源极断开进行测试,A3为正常测试,表明一次断开源极测试并未导致该芯片损坏(但不排除一定的损伤)。

图1 芯片原始数据及一次断源测试对芯片的影响

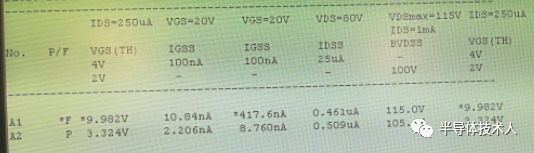

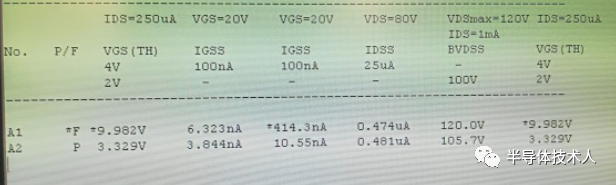

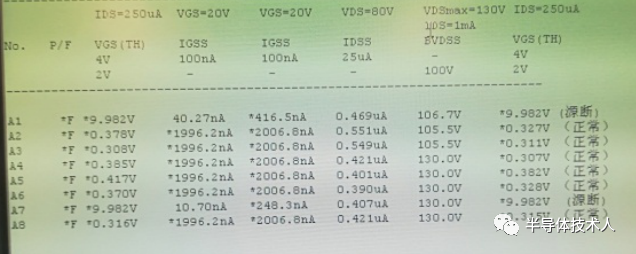

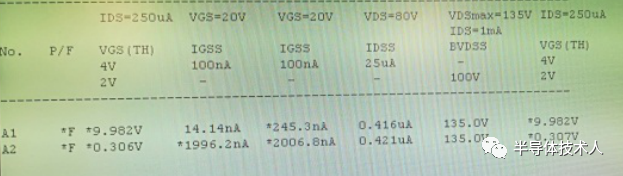

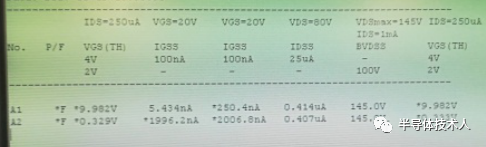

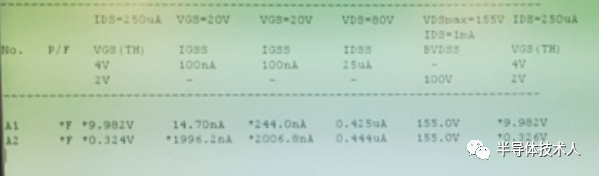

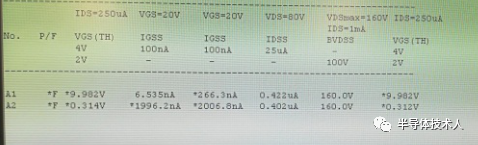

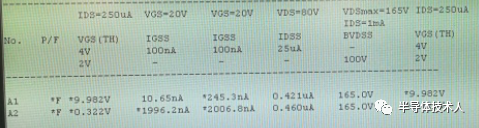

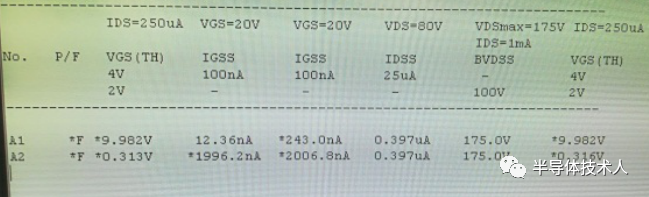

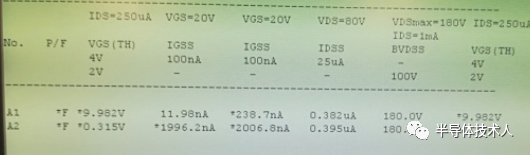

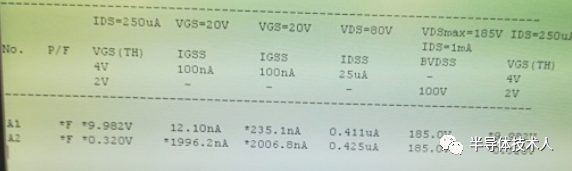

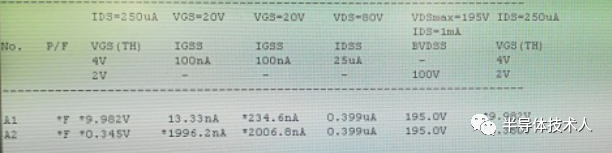

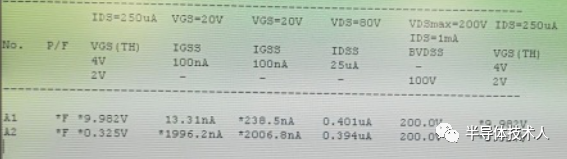

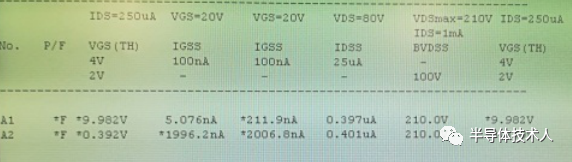

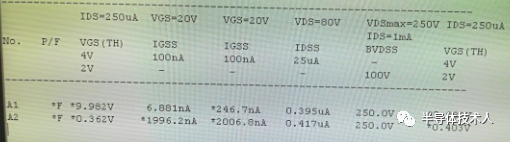

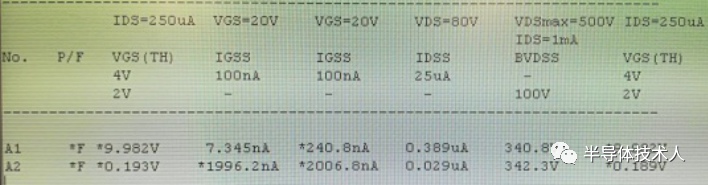

由于该(型号)芯片,一次断源测试后正常测试结果并未与前期xxxx失效数据吻合,为了进一步验证对于不同导电类型MOS芯片采用相同测试条件是否会出现相同的测试结果,以及对比不同导电类型的MOS芯片抗漏栅击穿损坏能力,将该芯片的漏源击穿电压测试条件中的上限电压值增大,步进电压为5V。测试数据如图2所示,其中A1为源极断开测试结果,A2为正常测试结果。由图2可见:当击穿电压上限值加到130V(漏栅电压加到130V)时,经过断源测试后正常测试数据中的阈值电压、栅源正反向漏电流出现严重劣化,而其他电参数几乎没有变化(当时关注的是漏源击穿电压项,但该项没有变化)。表明当漏源击穿电压上限值更改到130V时,栅源之间的氧化层间发生了穿通,而漏源结及漏栅氧化层之间并未被损坏(但有可能存在一定程度的损伤)。将漏源击穿电压的上限提高到500V,断开源极测试的数据中漏源击穿电压参数并未显示500V,显示的是340.8V,正常测试数据中漏源击穿电压显示值未342V,表明漏栅间并未穿通,但漏源结存在问题(正常测试值应约为100V)。

图2 增大漏源击穿电压测试上限对芯片电参数的影响

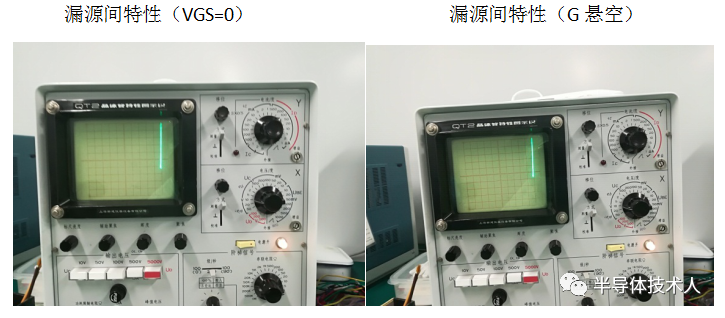

利用图示仪对该芯片的极间特性进行测试,测试曲线如图3所示。由测试曲线可见:沟道区栅氧化层击穿,P区结烧毁,漏栅未损坏。并且还得到不是所有类型的MOS芯片断源测试会将漏栅穿通,以及在测试过程中合理设置漏源击穿电压测试上限值电压可降低芯片损坏的可能。