击左上方蓝色“一口Linux”,选择“设为星标”

第一时间看干货文章 ☞【干货】嵌入式驱动工程师学习路线 ☞【干货】Linux嵌入式知识点-思维导图-免费获取 ☞【就业】一个可以写到简历的基于Linux物联网综合项目 ☞【就业】找工作简历模版

作者:晏舒

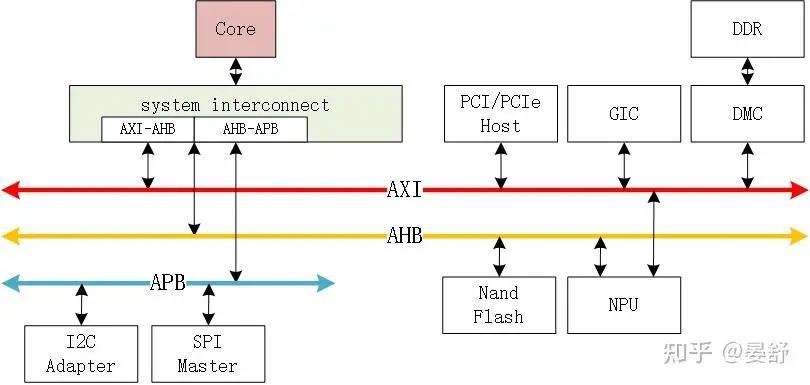

速率:APB

AXI支持读写并行操作;

AXI/AHB支持多主/从设备,有总裁机制,APB不支持;

Soc厂商会做好Address Mapping,当CPU对不同地址访问时,由内存控制器将地址或者数据发到对应的总线最终到达最终的设备上。

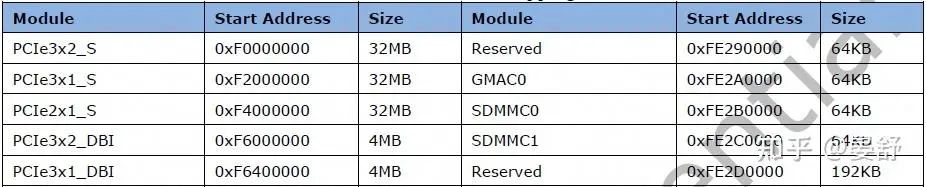

Example:From Rockchip SPEC

提高设备访问速率:硬件设计+协议;

提高扩展性;

设备访问方式的改变;

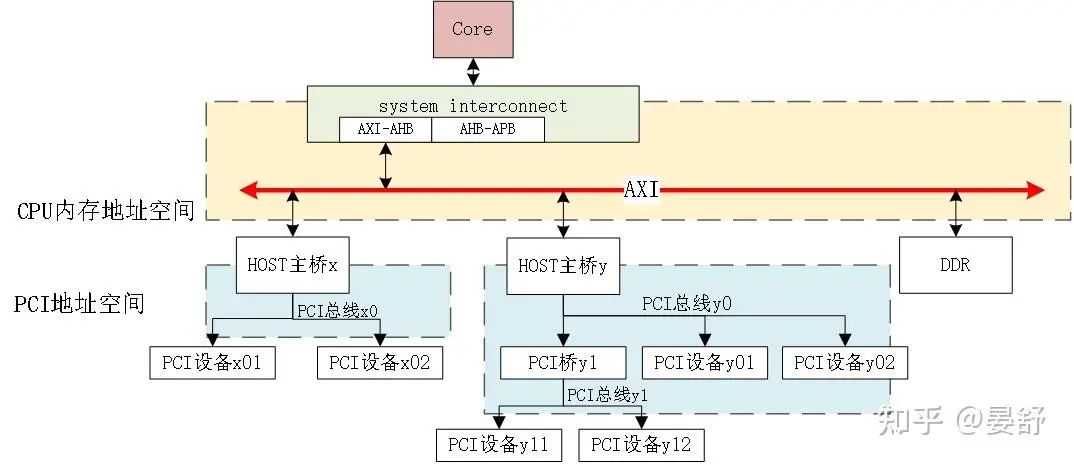

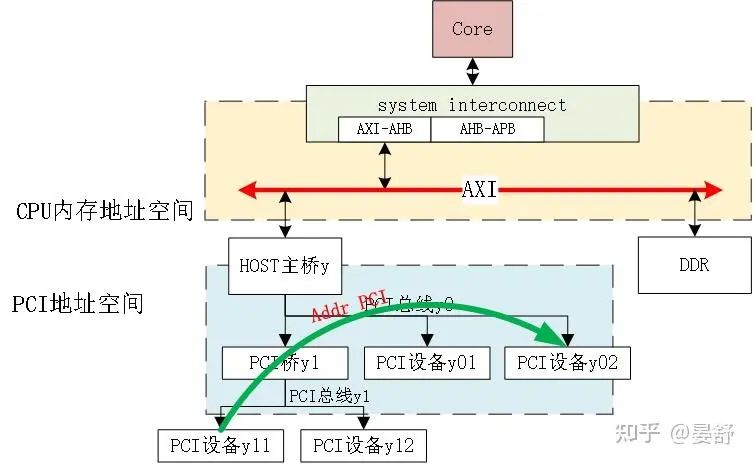

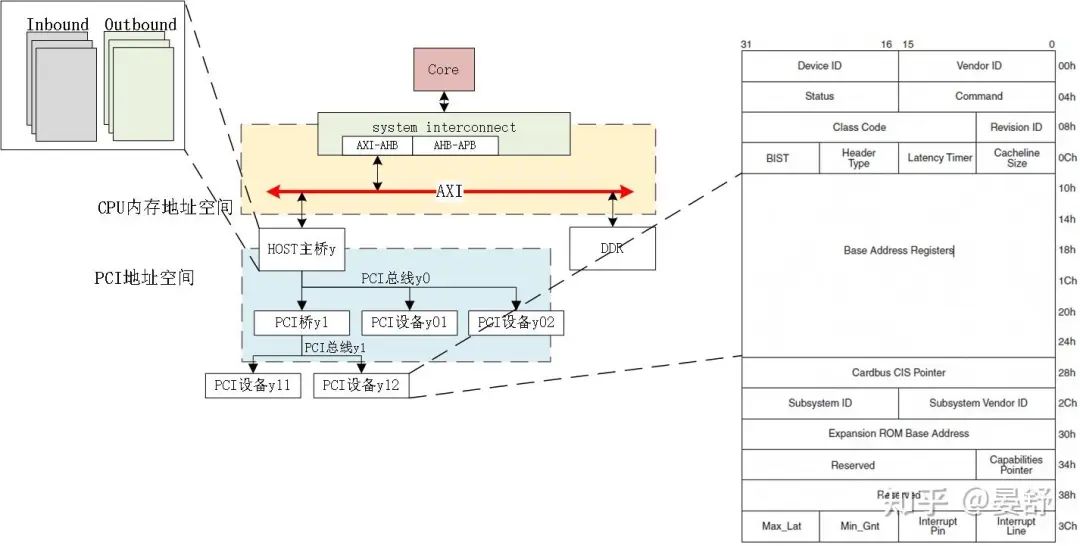

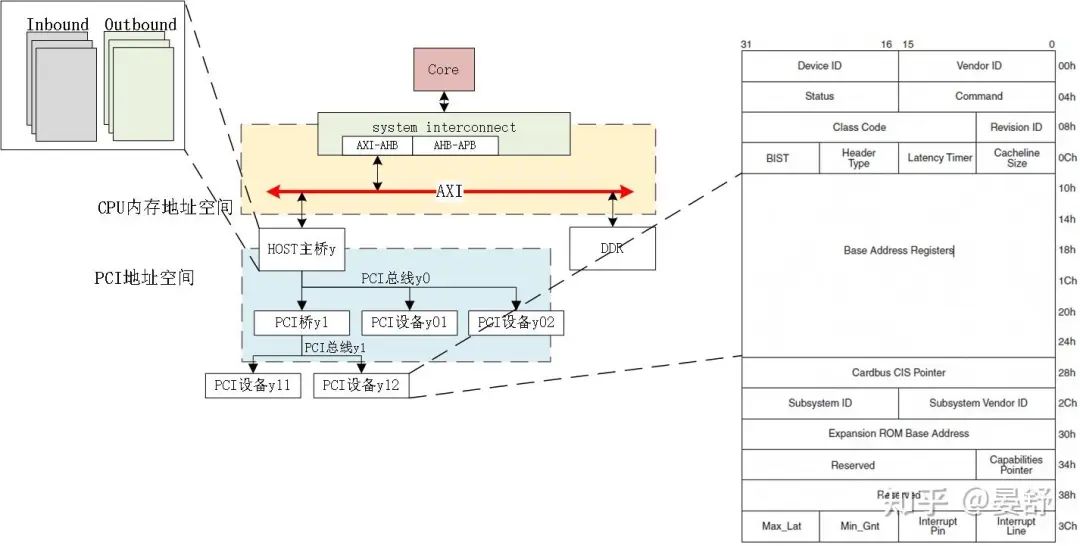

CPU发出CPU内存域地址;

HOST主桥y发现该地址属于自己内部内存域地址和PCI地址的转换范围;

HOST主桥y将该地址转换为PCI域地址;

根据该PCI域地址通过PCI桥y1最终找到PCI设备y12;

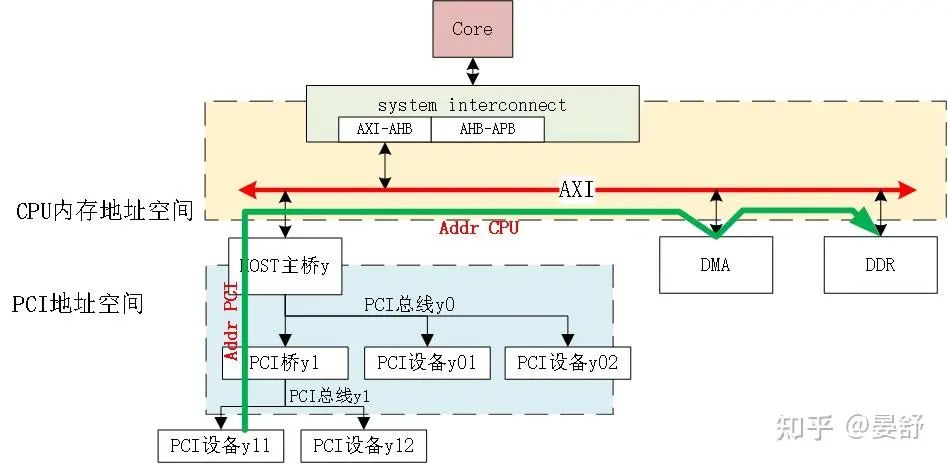

PCI设备y11发出PCI域地址;

该地址通过PCI桥y1找到挂载在PCI总线y0上的PCI设备y02;

PCI设备y11尝试将数据给到DDR地址空间;

HOST主桥y接收到PCI设备y11尝试访问的地址,并将其转换为CPU域地址;

DMA实现PCI设备数据到DDR的数据搬运(可以不使用DMA,通过CPU进行数据搬运,但效率低);

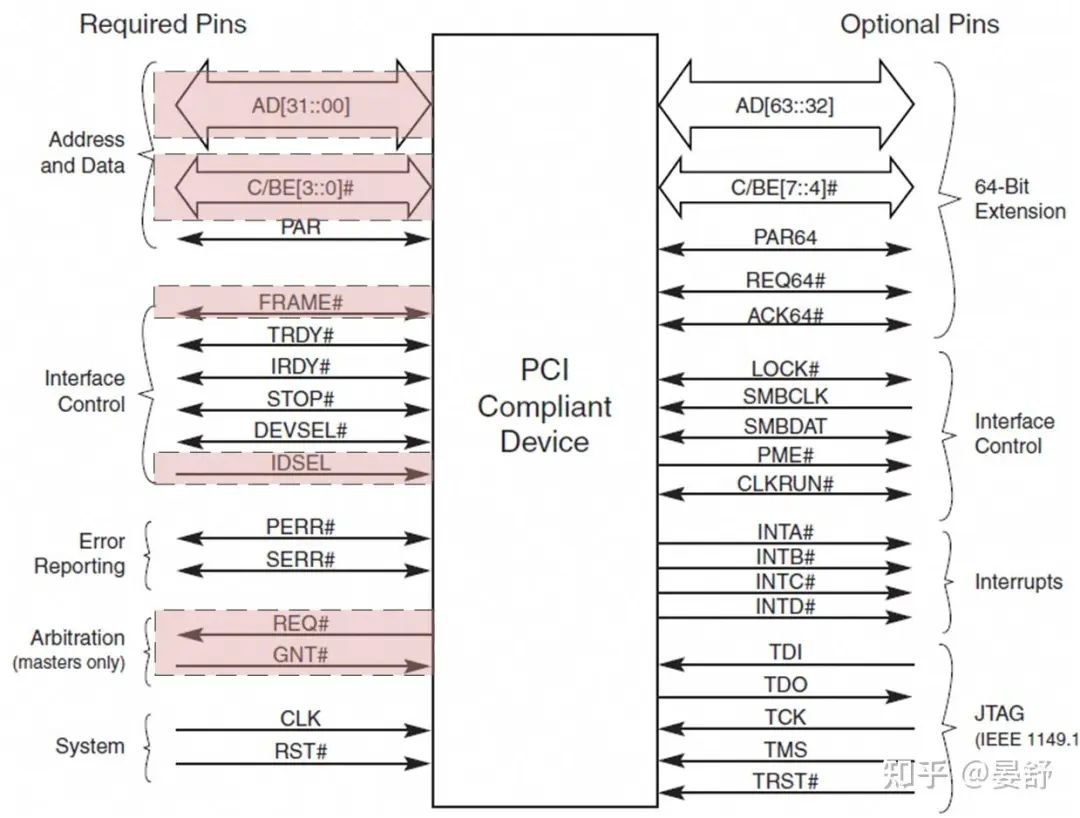

如果不是做PCI相关电路设计,则只需要关注上述几个关键信号管脚:

AD[31:0]:Address/Data 复用信号线,PCI总线事务在启动后的第一个时钟周期传送地址,下一个时钟周期传送数据;

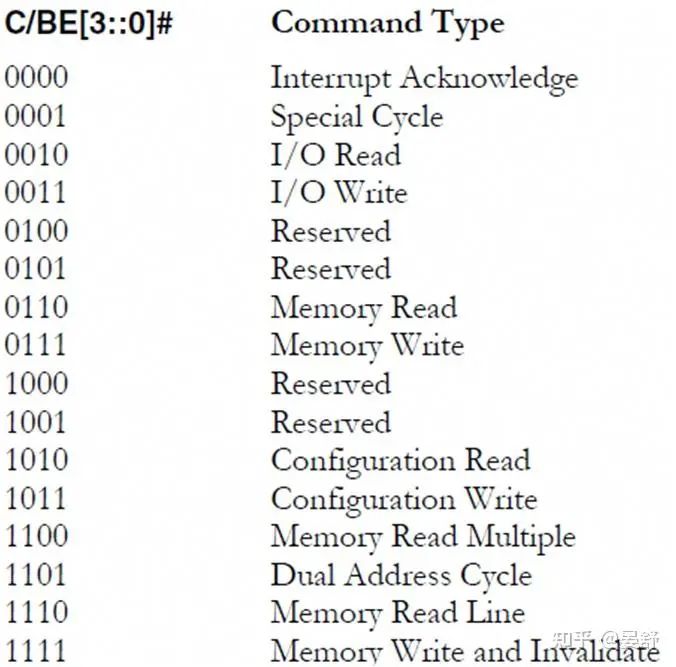

C/BE[3:0]#:Bus Command/Byte Enables,总线命令或者字节选通复用信号,地址周期表示命令,数据周期时输出字节选通信号,使用这组信号可以对PCI设备进行单个字节、字和双字访问;

FRAME#:指示PCI总线事务的开始和结束;

IDSEL信号:PCI总线在进行配置读写总线事务时,使用该信号选择PCI目标设备。

REQ#/GNT#:总线仲裁信号;

PCI设备的配置空间中,一共有6个BAR寄存器。BAR寄存器存放PCI设备使用的PCI总线域的物理地址,通过HOST主桥完成内存域地址到PCI域地址的映射关系。

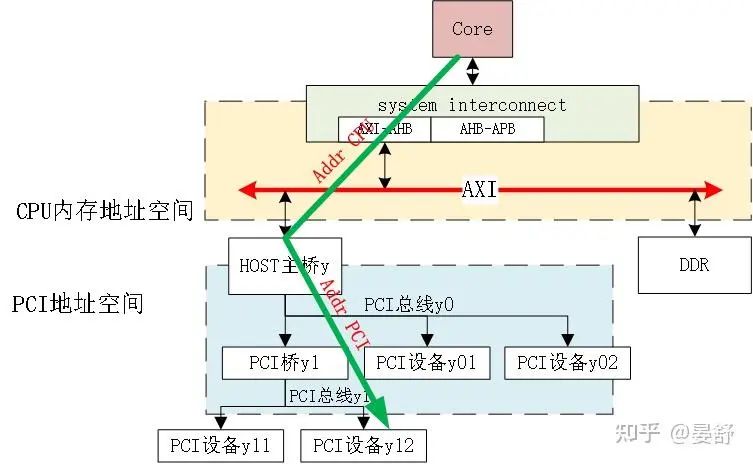

CPU将要传递的数据放入通用寄存器,之后向PCI设备y12映射到的CPU域地址进行写操作;

HOST主桥y接收来自处理器的存储器写请求,处理器释放总线,HOST主桥将CPU域地址转换为PCI总线域的PCI总线地址,并向PCI总线y0发起PCI写请求总线事务;

PCI总线y0上的PCI设备y01、y01和PCI桥y1同时监听这个PCI写总线事务,PCI桥y1接收这个写总线事务;

PCI桥y1上PCI设备同时监听这个PCI写总线事务,PCI设备y12通过地址译码接收这个写总线事务;

场景2:PCI设备y12向主存储器写数据,PCI设备进行DMA写操作。

PCI设备y12将存储器写请求发向PCI总线x1;

PCI总线y1上的所有设备监听这个请求;

PCI桥y1发现当前总线事务使用的PCI地址不是其下游设备使用的PCI总线地址,则接收这个数据请求,并推送到上游;

PCI总线y0上的所有PCI设备监听这个请求;

HOST主桥发现这个请求发向存储器,则将来自PCI总线y0的PCI总线地址转换为存储器地址,之后通过存储器控制器将数据写入存储器;

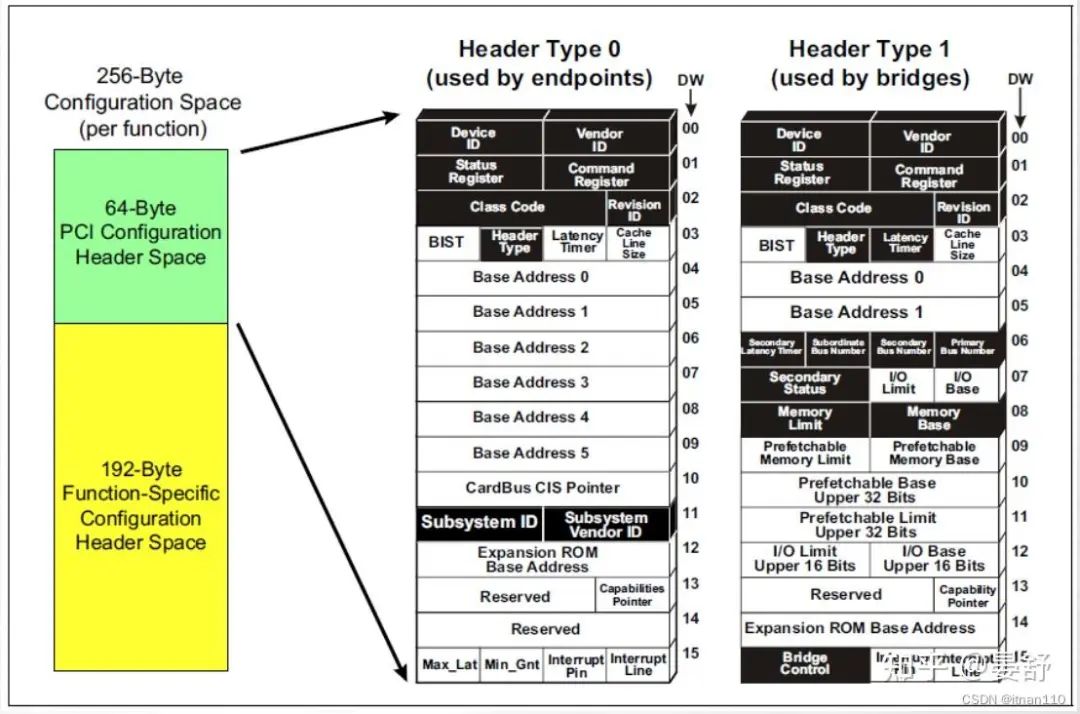

配置空间为PCI桥设备或者PCI Agent设备上的一块ROM区间。

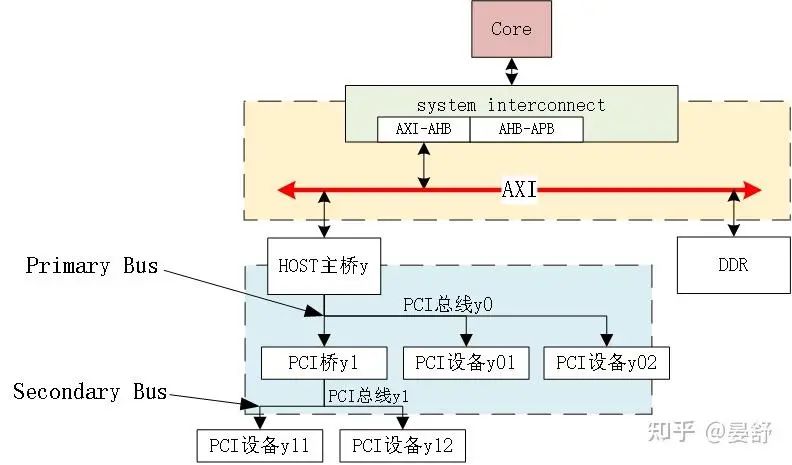

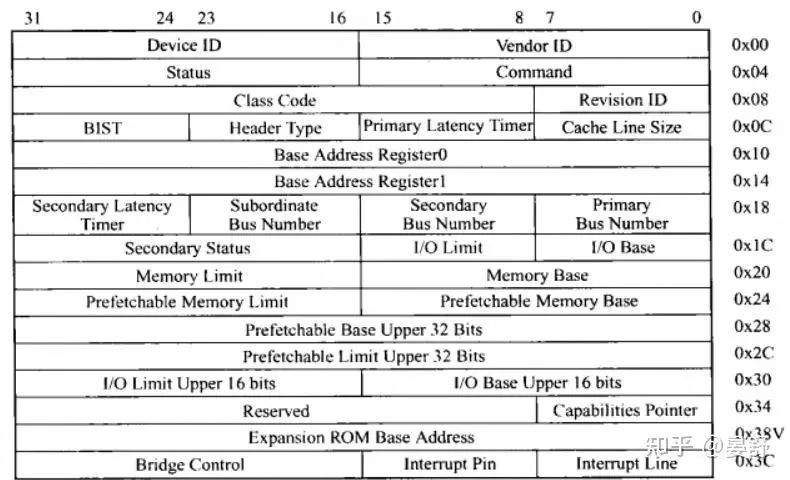

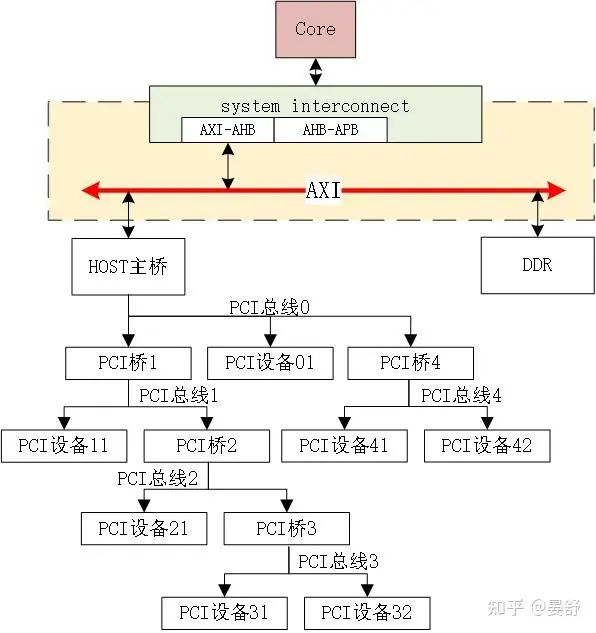

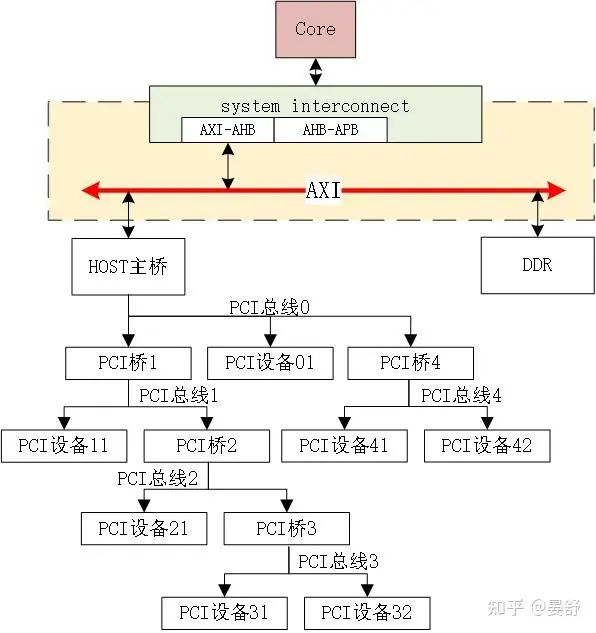

PCI桥跨接在两个PCI总线之间,其中距离HOST主桥较近的PCI总线称为该桥片的上游总线(Primary Bus),距离HOST主桥较远的PCI总线称为该桥片的下游总线(Secondary Bus)。

PCI桥y1的上游总线为PCI总线y0,下游总线为PCI总线y1。

通过PCI桥组成一个胖树结构,其中每个桥片都是父节点,而PCI Agent设备只能是子节点。

通过PCI桥可以扩展一条新的PCI总线,但是不能扩展新的PCI总线域。在上述PCI总线域y中,所有设备共享该总线域的地址空间大小。

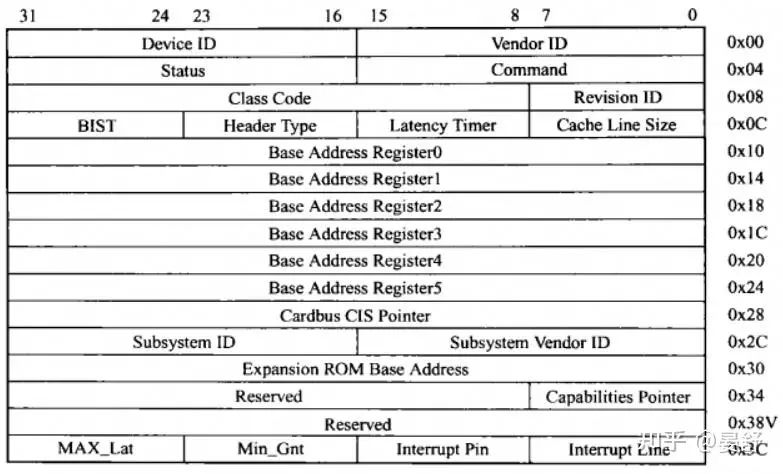

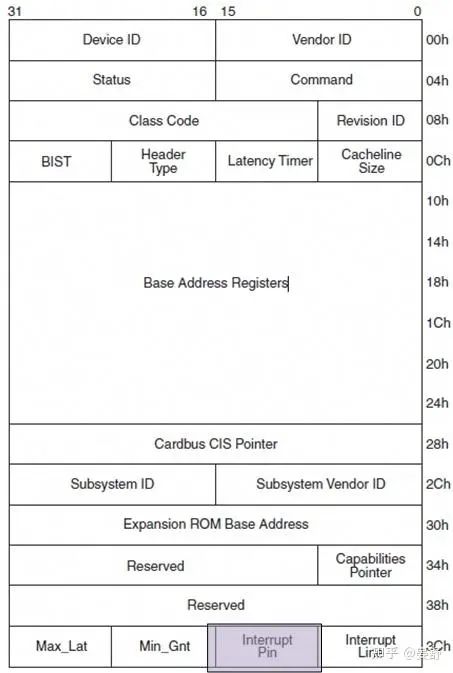

Device ID/Vendor ID:PCISIG分配,Vendor ID代表生产厂商,Device ID代表这个厂商所生产的具体设备;

Header Type:8位,第七位为1表示多功能设备,为0表示单功能设备。第6~0位表示当前配置空间的类型,0为PCI Agent,1为PCI桥;

Base Address Register 0~5寄存器:BAR寄存器组,保存PCI设备使用的地址空间的基地址,该基地址是该设备在PCI总线域中的地址。PCI设备复位后,该寄存器存放PCI设备需要使用的基地址空间大小;

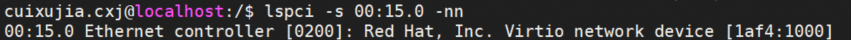

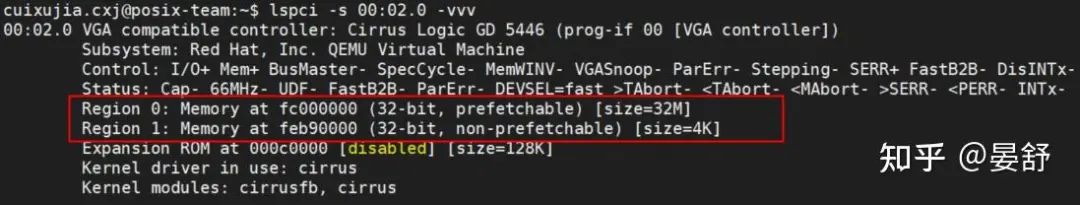

以上述VGS GD 5446为例,我们可以通过mmap映射BAR Region0来读取PCI设备BAR 1对应空间的内容,当然对BAR 1空间地址的读写具体代表什么含义要参考GD 5446的数据手册了:

示例代码:(我们可以通过内存访问的方式去和PCI设备打交道了)

#include

#include

#include

#include

#include

#include

#define MEMORY_REGION_SIZE 4096

#define READ_SIZE 100

int main() {

int fd;

off_t pci_addr = 0xfeb90000;

void *mmap_addr;

unsigned char *pci_data;

fd = open("/dev/mem", O_RDONLY);

if (fd == -1) {

perror("Error opening /dev/mem");

return EXIT_FAILURE;

}

mmap_addr = mmap(NULL, MEMORY_REGION_SIZE, PROT_READ, MAP_SHARED, fd, pci_addr);

if (mmap_addr == MAP_FAILED) {

perror("Error mmapping the device");

close(fd);

return EXIT_FAILURE;

}

pci_data = (unsigned char *)mmap_addr;

printf("Reading first 20 bytes of PCI BAR 0 at address 0xfc000000:\n");

for (int i = 0; i < READ_SIZE; i++) {

printf("%02hhx ", pci_data[i]);

}

printf("\n");

if (munmap(mmap_addr, MEMORY_REGION_SIZE) == -1) {

perror("Error unmapping memory");

close(fd);

return EXIT_FAILURE;

}

close(fd);

return 0;

}

sudo ./a.out

Reading first 20 bytes of PCI BAR 0 at address 0xfc000000:

20 20 00 00 07 f5 ff 00 00 00 00 00 67 00 06 01 00 00 00 00 1d 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

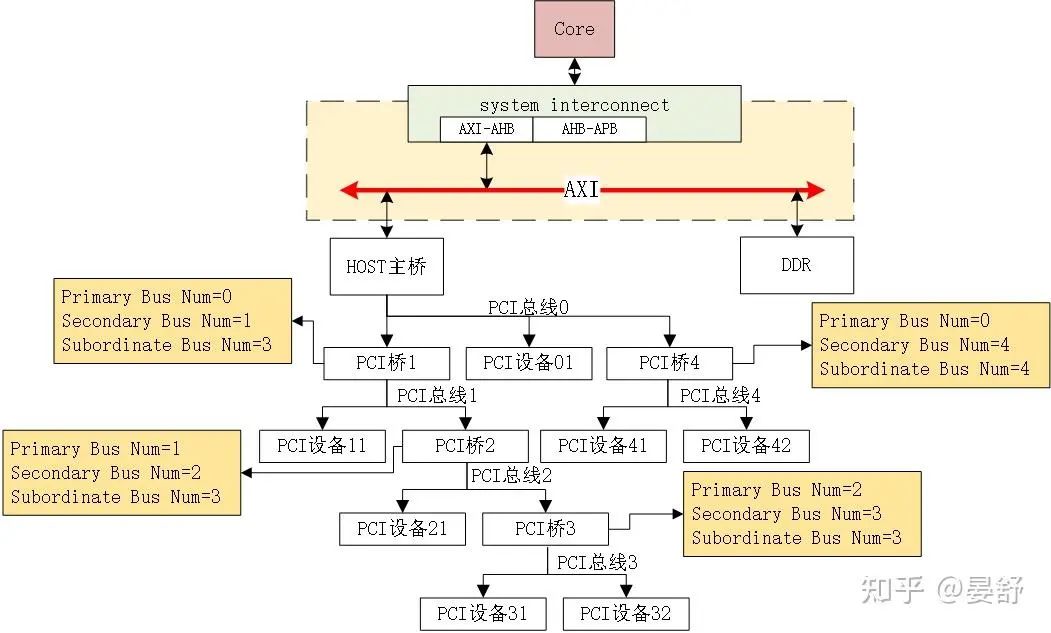

Subordinate Bus Number:存放当前PCI子树中,编号最大的PCI总线号;

Secondart Bus Bumber:存放当前PCI桥Secondary Bus使用的总线号,这个PCI号是该PCI桥管理的PCI子树中编号最小的PCI总线号;

Primary Bus Number:存放该PCI桥上游PCI总线号;

以X86为例,BIOS或UEFI会负责PCI总线树的遍历,查找所有PCI设备,分配所需资源,比如内存地址空间,IO空间和中断等。之前提到PCI设备配置空间的初始化是通过ID译码的,因此这里要讲一下BUS:Device.Function是如何被定义的。

示例:

cuixujia.cxj@posix-team:~$ lspci -tv

-[0000:00]-+-00.0 Intel Corporation 440FX - 82441FX PMC [Natoma]

+-01.0 Intel Corporation 82371SB PIIX3 ISA [Natoma/Triton II]

+-01.1 Intel Corporation 82371SB PIIX3 IDE [Natoma/Triton II]

+-01.3 Intel Corporation 82371AB/EB/MB PIIX4 ACPI

+-02.0 Cirrus Logic GD 5446

+-03.0 Red Hat, Inc. Virtio network device

+-04.0 Intel Corporation 82801I (ICH9 Family) USB UHCI Controller #1

+-04.1 Intel Corporation 82801I (ICH9 Family) USB UHCI Controller #2

+-04.2 Intel Corporation 82801I (ICH9 Family) USB UHCI Controller #3

+-04.7 Intel Corporation 82801I (ICH9 Family) USB2 EHCI Controller #1

+-05.0 Red Hat, Inc. Virtio block device

\-06.0 Red Hat, Inc. Virtio memory balloon如上docker所示,该系统只有一个PCI总线(总线0),该总线下共有6个Device,其中Device1/4有多个Function。

使用深度优先DFS算法遍历PCI总线树。

示例:

HOST主桥扫描PCI总线0上的设备,首先忽略这条总线上的所有PCI Agent设备;

HOST主桥发现了PCI桥1,并将桥1的Secondary Bus命令为PCI总线1,。系统软件初始化PCI桥1的配置空间,将PCI桥1的Primary Bus Number寄存器赋值为0,将Secondary Bus Number寄存器赋值为1,即PCI桥1的上游PCI总线号为0,下游PCI总线号为1;

扫描PCI总线1,发现桥2,并将PCI桥2的Secondary Bus命名为PCI总线2。系统软件将初始化PCI桥2的配置空间,将PCI桥2的Primary Bus Number寄存器赋值为1,将Secondary Bus Number寄存器赋值为2;

扫描PCI总线2,发现PCI桥3,并将桥3的Secondary Bus命名为PCI总线3。系统软件初始化PCI桥3的配置空间,将PCI桥3的Primary Bus Number寄存器赋值为2,将Secondary Bus Number寄存器赋值为3;

扫描PCI总线3,没有发现桥设备,表示PCI总线3下不能有新的总线,系统软件将PCI桥3的Subordinate Bus Numer寄存器赋值为3。系统软件在完成PCI总线3的扫描后,将回退到PCI总线3的上一级总线,即PCI总线2,继续扫描;

在重新扫描PCI总线2时,系统软件发现PCI总线2上除了PCI桥3之外没有发现新的PCI桥,而PCI桥3下所有设备已经扫描完成,此时系统软件将PCI桥2的Subordinate Bus Number寄存器赋值为3,回退到PCI总线1;

PCI总线1上除了PCI桥2外,没有其他桥片,于是继续回退到PCI总线0,并将PCI桥的Subordinate Bus Number寄存器赋值为3;

在PCI总线0上,系统软件扫描到PCI桥4,则首先将PCI桥4的Primary Bus Number寄存器赋值为0,将Secondary Bus Number寄存器赋值为4,即PCI桥4的上游总线号为0,下游总线号为4;

系统软件发现PCI总线4上没有PCI桥,结束对PCI总线4的扫描,将PCI桥4的Subordinate Bus Number寄存器赋值为4,回退到PCI总线4的上游总线PCI总线0;

系统软件发现在PCI总线0上的两个桥片都已经扫描完成,结束对PCI总线的遍历;

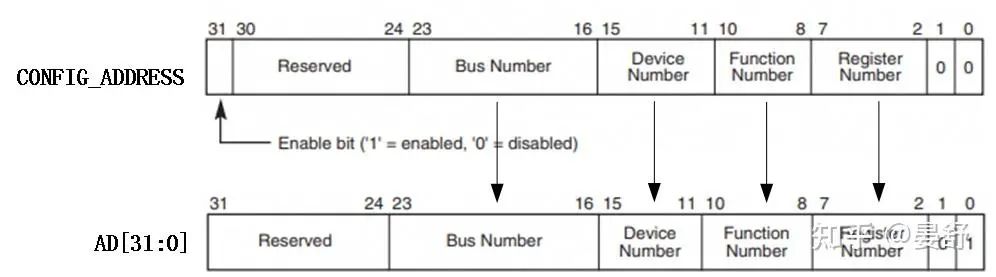

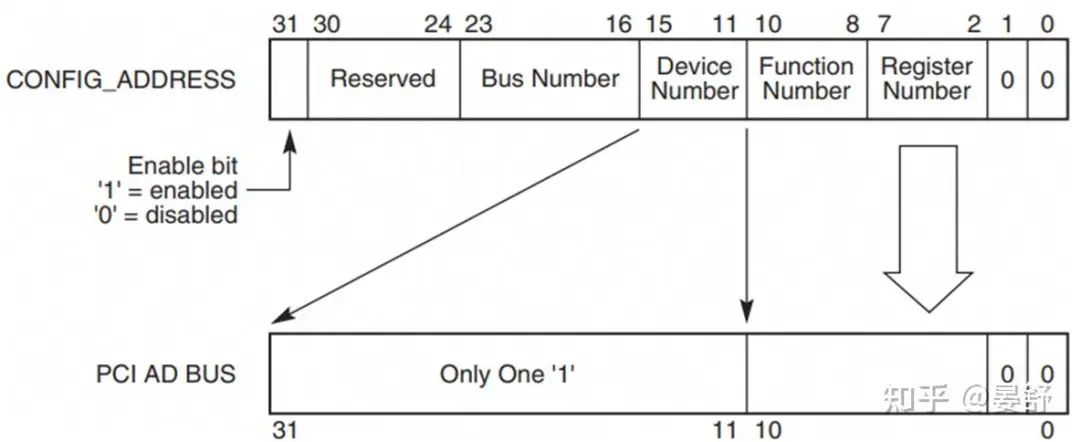

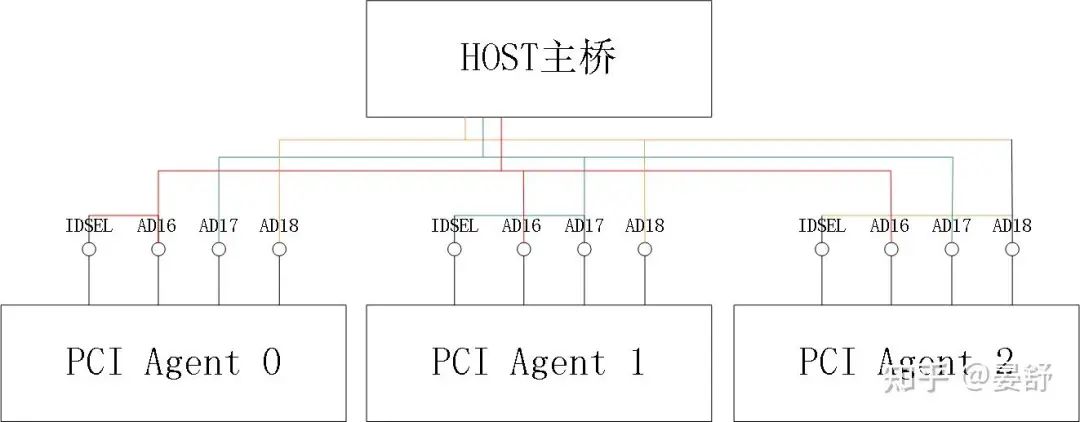

Device号的确定是通过IDSEL信号确定,但是这部分就和硬件相关了,而且在将IDSEL是如何确定Device号之间,必须要先看一下PCI的配置读写事务是如何工作的:

PCI总线定义了两类配置请求,一类是Type 01配置请求,另一类是Type 01配置请求。

HOST主桥或者PCI桥使用Type 00h配置请求,访问与HOST主桥或者PCI桥直接相连的PCI Agent设备或者PCI桥。

HOST主桥或者PCI桥使用Type 01h配置请求,访问没有与其直接两连的PCI Agent或者PCI桥;

处理器首先将目标PCI设备的ID号保存在CONFIG_ADDRESS(x86方式)寄存器中,之后HOST主桥根据寄存器的Bus Number字段,决定是产生Type 00h还是01h配置请求。当Bus Number字段为0,将产生Type 01h配置请求,当Bus Number大于0时,产生Type 01配置请求;

CONFIG_ADDRESS寄存器与Type 01h配置请求:

CONFIG_ADDRESS寄存器与Type 00h配置请求:

继续回到Device号的分配,在Type 00h配置请求中,Device Number会给到地址线的[31:11]管脚上,如果在PCI插槽的硬件设计中,将同一PCI总线下的PCI设备的IDSEL管脚和不同该PCI设备的AD管脚相连,就可以确定Device号了。

PCI Agent 0的IDSEL和AD16相连,PCI Agent 1的IDSEL和AD17相连,PCI Agent 2的IDSEL和AD18相连,这样在Type 00h配置请求中AD信号就可以选中不同的PCI设备。

通过X86 IO Port操作CONFIG_ADDRESS和CONFIG_DATA来扫描PCI总线树,获取所有PCI设备及其配置空间的内容:

#include

#include

#include

#include

#define PCI_MAX_BUS 255

#define PCI_MAX_DEV 31

#define PCI_MAX_FUN 7

#define PCI_BASE_ADDR 0x80000000L

#define CONFIG_ADDR 0xcf8

#define CONFIG_DATA 0xcfc

typedef unsigned long DWORD;

typedef unsigned int WORD;

int main()

{

WORD bus, dev, fun;

DWORD addr, data;

printf("\nbus#\tdev#\tfun#\tvendor#\t\tdevice#\n");

iopl(3);

for (bus = 0; bus <= PCI_MAX_BUS; bus++) {

for (dev = 0; dev <= PCI_MAX_DEV; dev++) {

for (fun = 0; fun <= PCI_MAX_FUN; fun++)

{

addr = PCI_BASE_ADDR | (bus << 16) | (dev << 11) | (fun << 8);

outl(addr, CONFIG_ADDR);

data = inl(CONFIG_DATA);

if (((data & 0xFFFF) != 0xFFFF) && (data != 0))

{

printf("%02d \t%02d \t%02d \t", bus, dev, fun);

printf("%04x \t\t%04x", (data & 0xFFFF), (data & 0xFFFF0000) >> 16);

printf("\n--------------------------------------------\n");

}

}

}

}

iopl(0);

return 0;

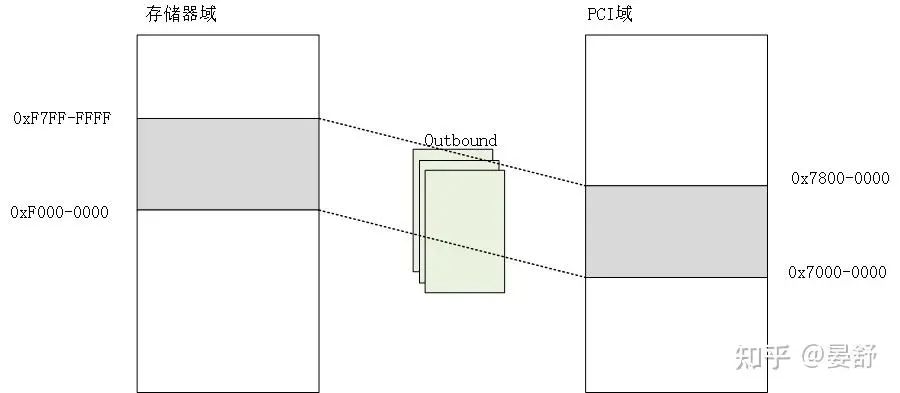

}假设,存储器域的0xF000-0000 ~ 0xF7FF-FFFF(128M)物理地址空间与PCI总线的地址空间存在映射关系。

当处理器访问这段储存器地址空间时,HOST主桥会认领这个存储器访问,通过outbound将该存储器访问使用的物理地址空间转换为PCI总线地址空间,并于0x7000-0000 ~ 0x77FF-FFFF这段PCI总线地址空间对应。

反过来也一样,但是使用Inbount寄存器实现PCI总线地址到存储器域地址的转换,这里就不画了。

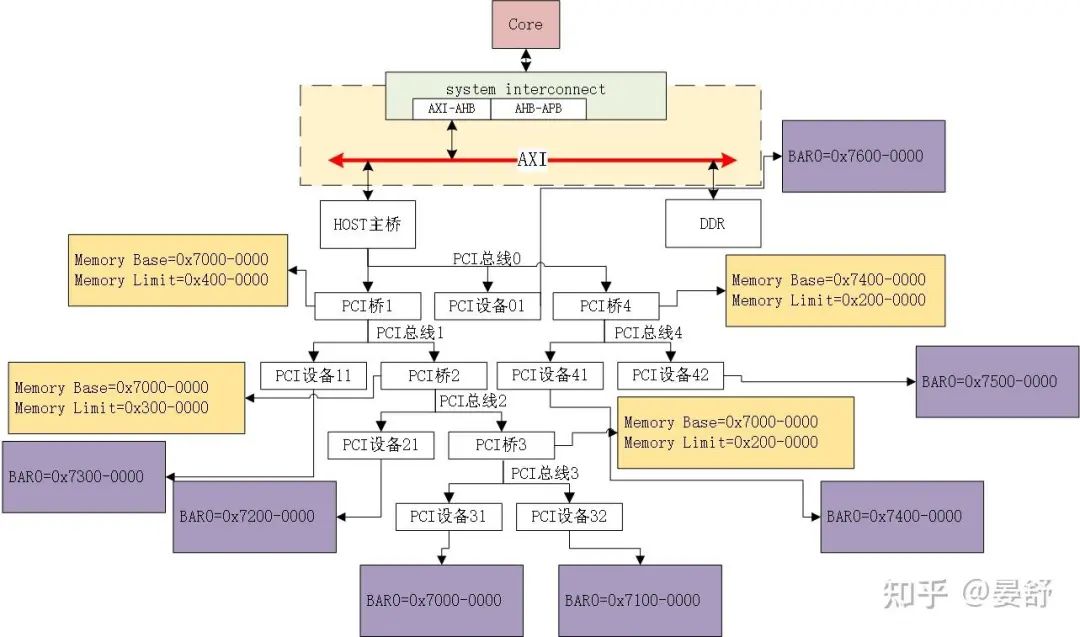

假定所有PCI Agent只使用BAR0寄存器,申请的数据空间大小为16M(0x1000000B)。

根据DFS算法,首先寻找第一组PCI设备,分别为PCI设备31和PCI设备32,并根据这两个设备需要的PCI空间大小,从PCI总线地址中(0x7000-0000 ~ 0x77FF-FFFF)为这两个PCI设备的BAR0寄存器分配基地址,分别为0x7000-0000和0x71000-0000。

当系统软件完成PCI总线3下所有设备的BAR空间分配后,初始化PCI桥3的配置空间,这个PCI桥的Memory Base寄存器保存其下所有PCI设备使用的PCI总线域地址空间的基地址,Memory Limit寄存器保存其下PCI设备使用的PCI总线域地址空间的大小。系统软件将Memory Base寄存器赋值为0x7000-0000,而将Memory Limit寄存器赋值为0x200-0000。

系统软件回朔到PCI总线2,并找到PCI总线2上的PCI设备21,并将PCI设备21的BAR0寄存器赋值为0x7200-0000。

完成PCI总线2的遍历后,系统软件初始化PCI桥2的配置寄存器,将Memory Base寄存器赋值为0x7000-0000,Memory Limit寄存器赋值为0x300-0000。

系统软件回朔到PCI总线1,并找到PCI设备11,并将这个设备的BAR0寄存器赋值为0x7300-0000。并将PCI桥1的Memory Base寄存器赋值为0x7000-0000,Memory Limit寄存器赋值为0x400-0000。

系统软件回朔到PCI总线0,并在这条总线上发现另外一个PCI桥,即PCI桥4。并使用DFS算法继续遍历PCI桥4。首先系统软件将遍历PCI总线4,并发现PCI设备41和PCI设备42,并将这两个PCI设备的BAR0寄存器分别赋值为0x7400-0000和0x7500-0000。

系统软件初始化PCI桥4的配置寄存器,将Memory Base寄存器赋值为0x7400-0000,Memory Limit寄存器赋值为0x200-0000。系统软件再次回到PCI总线0,这一次系统软件没有发现新的PCI桥,于是将初始化这条总线上的所有PCI设备。

PCI总线0上只有一个PCI设备,PCI设备01。系统软件将这个设备的BAR0寄存器赋值为0x7600-0000,并结束整个DFS遍历过程。

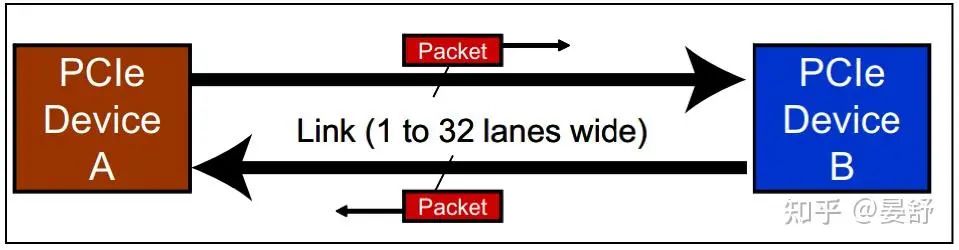

PCIE使用差分信号进行数据的串行传输以提高最大的传输速率,因此发送和接收共使用4条传输线,这4条传输线共同组成一个Lane:

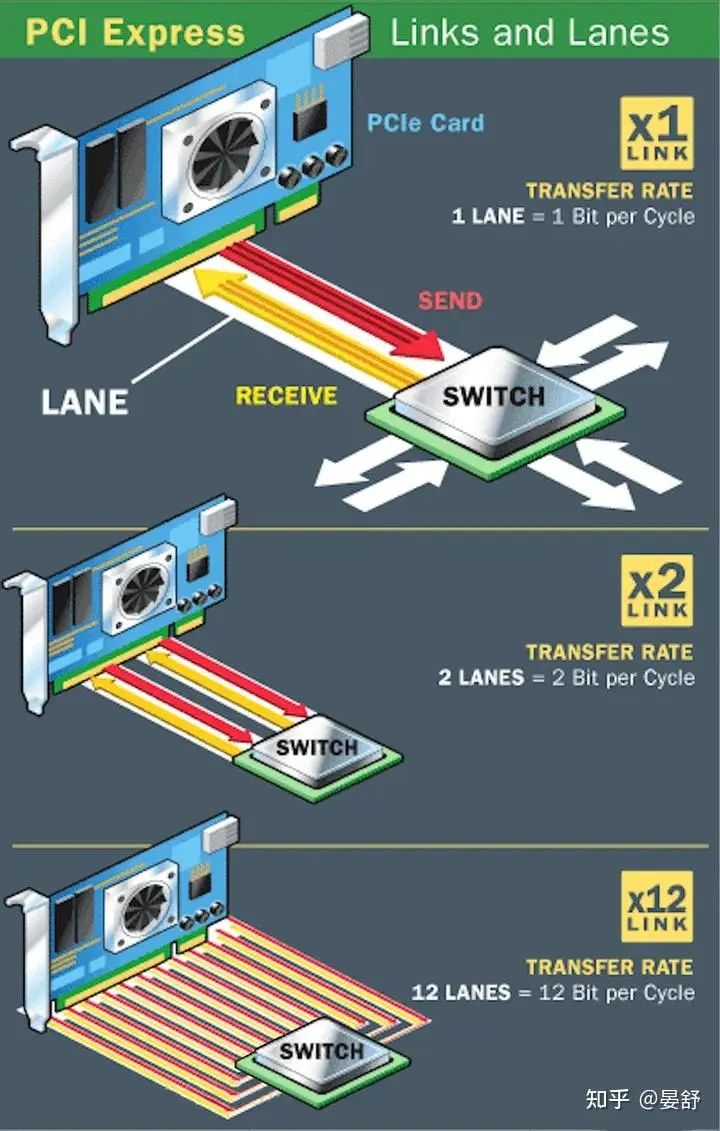

可以根据具体的PCIe外设,将PCIe链路配置成X1、X2、X4...、X32 Lane:

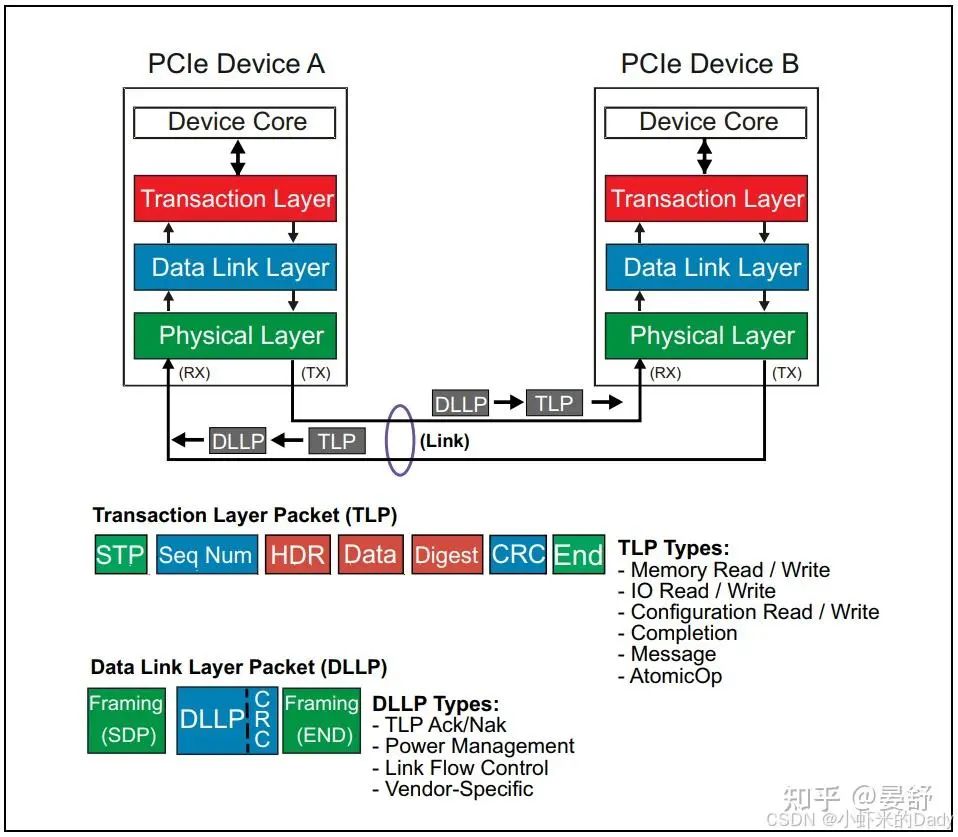

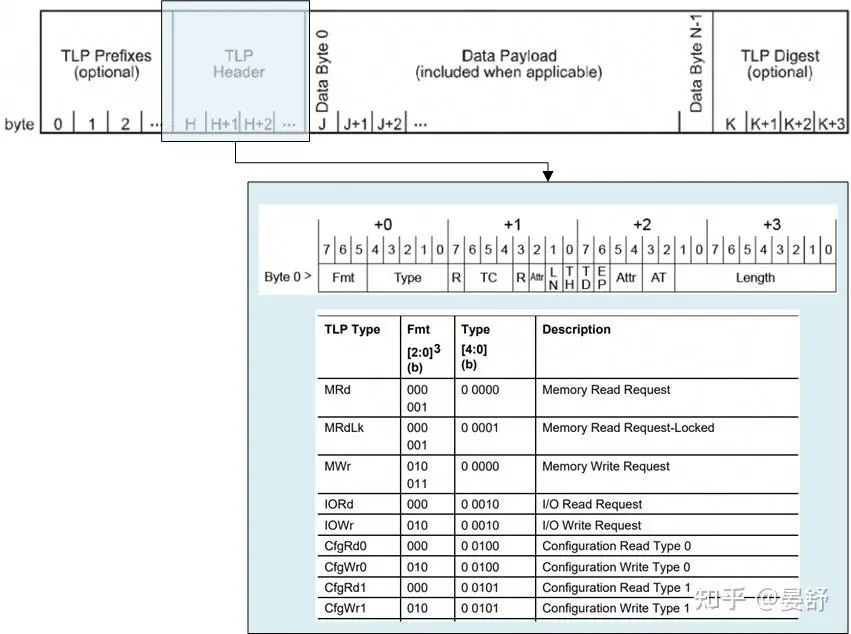

相比于并行传输接口,使用串行数据传输方式,就只能使用数据包的方式进行数据传输,同时需要定义数据传输协议:

通过事务层的TLP Header决定当前发送的TLP的总线事务:

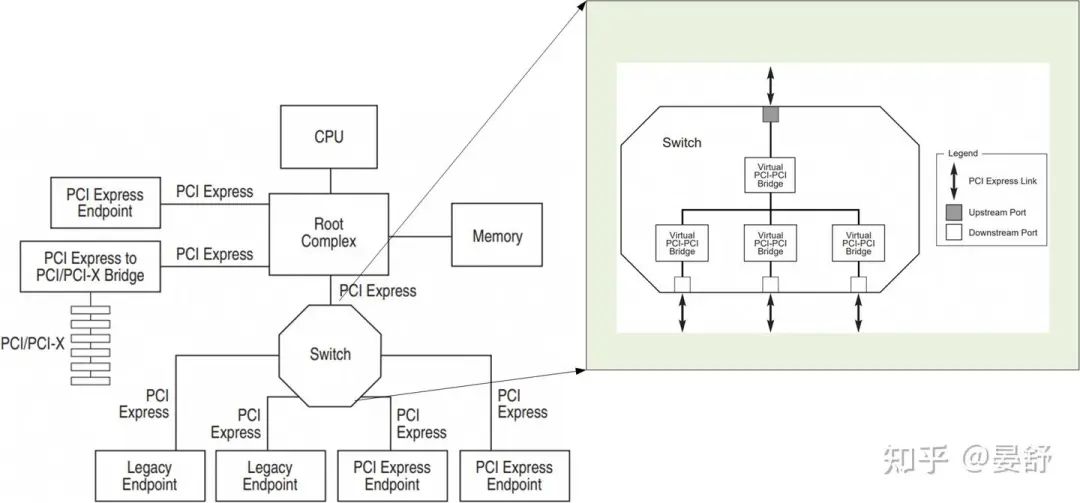

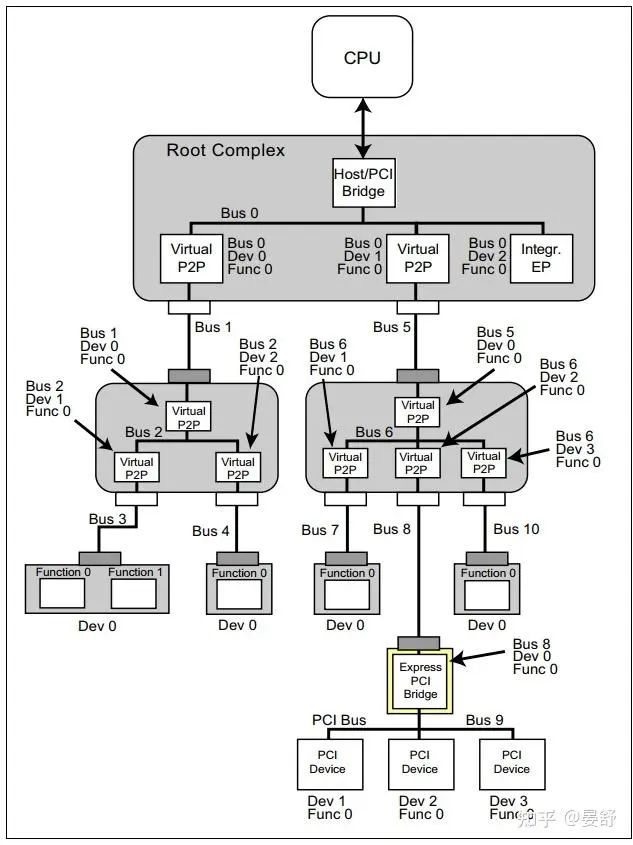

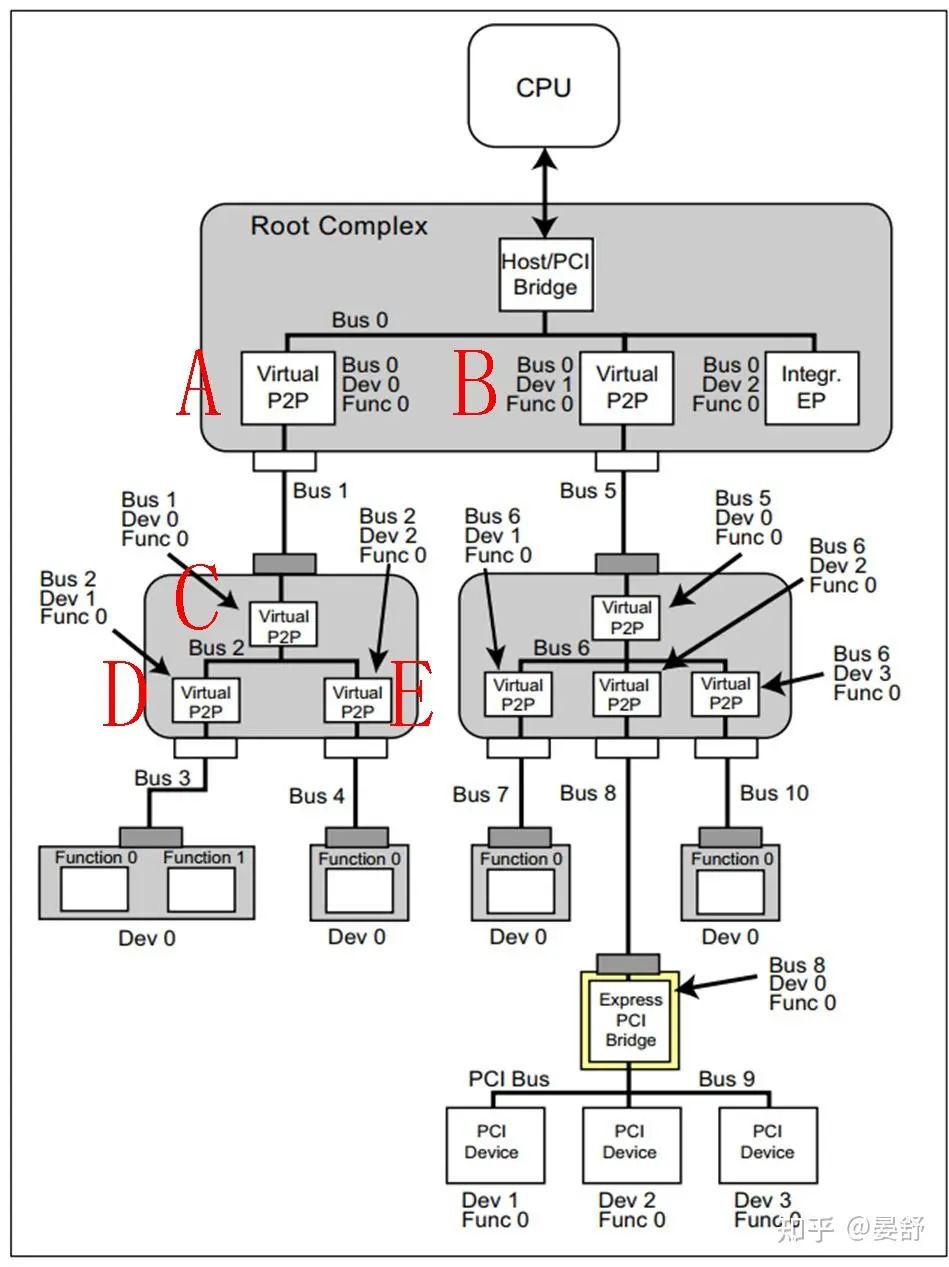

从Bus 0开始扫描,首先尝试读到0:0.0设备的Vendor ID,如果不成功表示没有这个设备,就尝试下一个设备0:1.0。一个桥下面最多可以连接32个设备。

读到了设备0:0.0的Vendor ID,表明设备存在,再读取其配置空间的Header Typer,发现是01h,表明它是一个桥设备;

发现了设备A是一个桥设备,然后配置其:

Primary Bus Number Register = 0:上游总线是0;

Secondary Bus Number Register = 1:它自身发出的总线是1;

Subordinate Bus Number Register = 255:先设置最大,因为还不知道其下游总线的最大值;

发现桥A,执行深度优先搜索:先去枚举A下面的设备,再回来枚举跟A同级的设备B;

读取设备1:0.0(设备C)的Vendor ID,ID存在,表明设备存在;

读取其配置空间的Header Type,发现为01h,表明这是一个桥设备;

配置桥C:

Primary Bus Number Register = 1:上游总线是1;

Secondary Bus Number Register = 2:它自身发出的总线是2;

Subordinate Bus Number Register = 255:先设置最大,因为还不知道其下游总线的最大值;

继续从桥C执行深度优先配置,枚举Bus 2下面的设备,从2:0.0开始;

读取设备2:0.0(设备D)的Vendor ID,ID存在,表明这个设备存在;

读取其配置空间Header Typer是01h,表示这是一个桥设备;

配置桥D:

Primary Bus Number Register = 2:上游总线是2;

Secondary Bus Number Register = 3:它自身发出的总线是3;

Subordinate Bus Number Register = 255:先设置最大,因为还不知道其下游总线的最大值;

继续从桥D执行深度优先配置,枚举Bus 3下面的设备,从3:0.0开始;

读取设备3:0.0的Vendor ID,ID存在,表明这个设备存在;

读取其配置空间Header Typer是80h,表示这是一个Endpoing,并且是一个多功能设备;

软件枚举这个设备的所有8个Function,发现它有两个Function0和1;

软件继续枚举Bus 3上其他设备,没有发现更多设备;

现在已经扫描完桥D下的所有设备,它下面没有桥,所有桥D的Subordinate Bus Number等于3。扫描完Bus 3后,回退到上一级Bus 2,继续扫描其他设备,从2:1.0开始;

读取2:1.0设备的Vendor ID,ID存在,即设备存在;

其Header Typer为01h,表明它是一个桥设备;

配置桥E:

Primary Bus Number Register = 2:上游总线是2;

Secondary Bus Number Register = 4:它自身发出的总线是4;

Subordinate Bus Number Register = 255:先设置最大,因为还不知道其下游总线的最大值;

继续从桥D执行深度优先配置,枚举Bus 4下的设备,从4:0.0开始;

读取4:0.0设备的Vendor ID,ID存在,设备存在;

其Header Typer是00h,表明是一个Endpoing设备,且是一个单功能设备;

软件继续枚举Bus 4上其他设备,没有发现更多设备;

已经枚举完设备E即Bus 4下所有设备,更新设备E的Subordinate Bus Number为4,然后继续扫描E的同级设备,没有发现新的设备;

软件更新设备C即Bus 2的桥,把它的Subordinate Bus Number设置为4,然后继续扫描设备C的同级设备,没有找到新的设备;

软件更新设备A即Bus 1的桥,把它的Subordinate Bus Number设置为4,然后继续扫描设备A的同级设备,发现桥设备B;

配置桥B:

Primary Bus Number Register = 0:上游总线是0;

Secondary Bus Number Register = 5:它自身发出的总线是5;

Subordinate Bus Number Register = 255:先设置最大,因为还不知道其下游总线的最大值;

从桥B开始,继续执行上述过程,知道全部遍历完成;

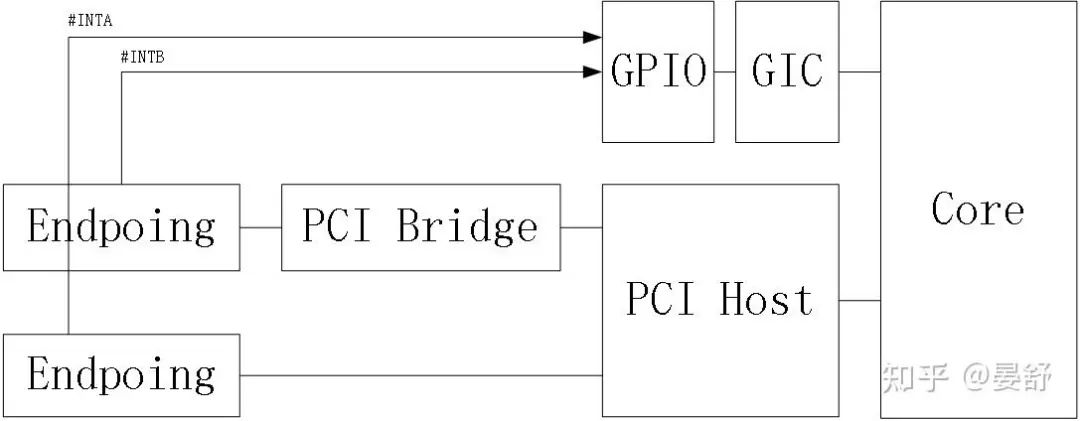

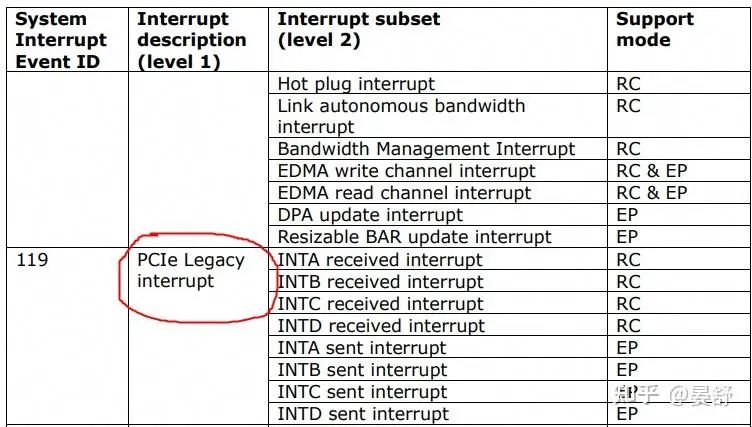

在讲MSI和MSI-X中断机制之前,需要先了解一下Legacy的中断方式,即使用INTx的中断。

PCI设备存在物理中断线INTA~INTD,使用边带信号将INTx和SOC GPIO相连,并配置GIC中断向量。

通过对PCI设备的配置空间中Interrupt Pin配置来决定该PCI设备触发中断时使用的中断线。

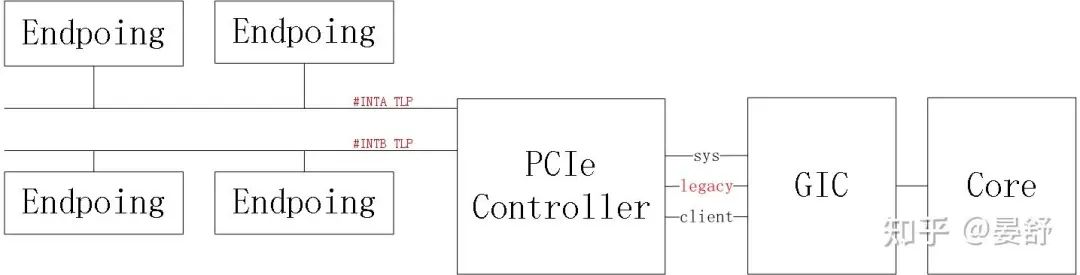

PCIe不存在INTx中断线,中断信号通过TLP发送给PCIe controller。

配置Endpoing的配置空间,决定其发送中断时使用的INTx;

Endpoing发送中断,中断发送通过TLP的方式给到PCIe控制器;

PCIe控制器收到INTx中断包,PCIe控制器通过Legacy中断引脚通知GIC中断控制器;

CPU处理中断,调用rockchip_pcie_legacy_int_handler,处理PCIe设备发来的INTA/INTB/INTC/INTD中断;

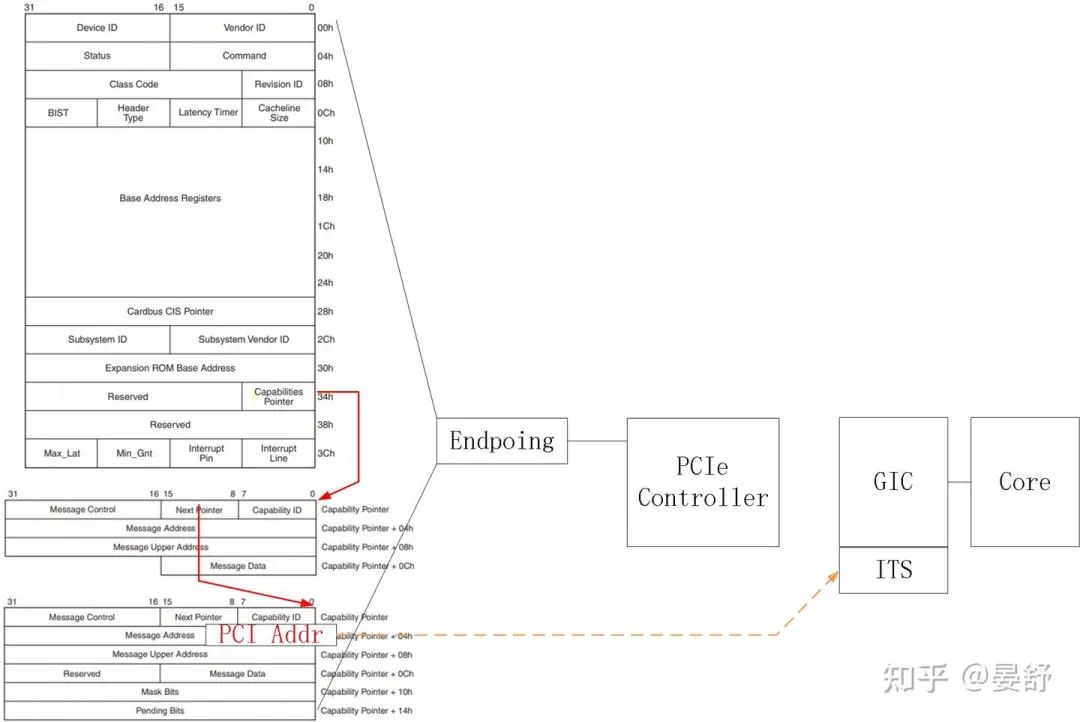

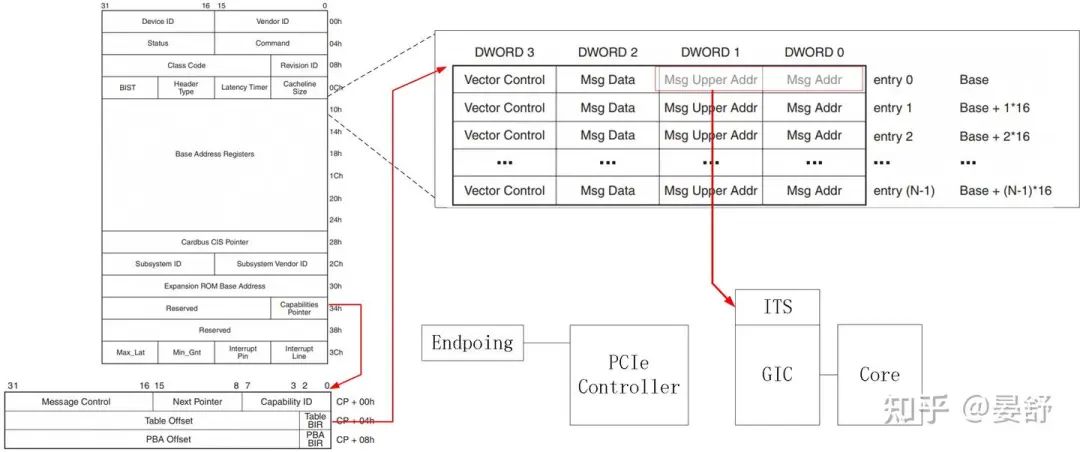

MSI可以使PCI/PCIe设备直接通过PCI/PCIe控制器的内存写事务向GIC发起ITS中断请求。

配置空间0x34的位置,存放第一个Capability的位置A;

在配置空间A位置,找到第一个Capablility:

第一个字节表示ID,如果是MSI中断,则ID为05H;

第二个字节表示下一个Capablility位置,为0表示这是最后一个;

Message Address:表示PCI/PCIe设备触发中断时向哪个地址进行内存写事务,这个地址由系统软件在初始化PCI设备时分配;

Message Data:可以理解为发出的中断ID,或者EventID;

MSI中断机制有一些缺陷:

每个设备只能最大支持32个中断;

中断需要连续分配;

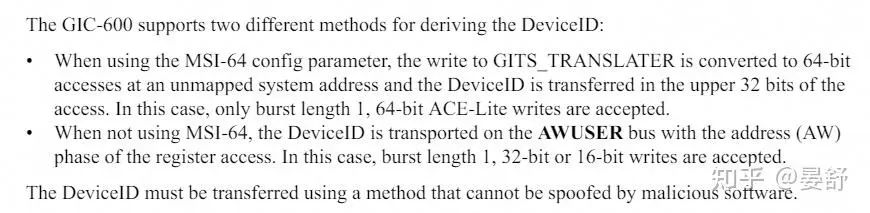

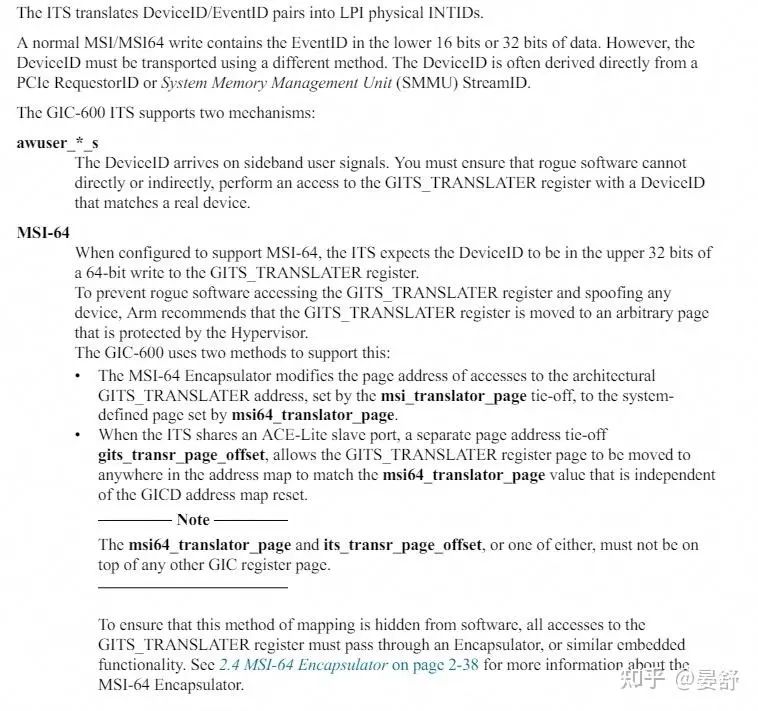

其实到上面都比较好理解,但是唯独有一个困惑,就是GIC ITS在转换时还需要一个DeviceID,但是MSI Message里并没有传输这个DeivceID,那么ITS如何知道这次LPI中断时的设备呢?

这部分资料很少很少,找了大量资料,从以下文档找到这这段话:

corelink_gic600_generic_interrupt_controller_technical_reference_manual_100336_0106_00_en.pdf

其实按照我的理解就是我们在配置ITS的DeviceID时,这个DeviceID是由BDF以规定的规则组成一个Requester ID(这也解释了为什么我们在ITS中注册的DeviceID也必须是RID),在PCIE触发MSI中断时,这个Requester ID也会跟随总线传输到比如AXI总线上,ITS在硬件设计中可能会使用比如AWUSER信号来获取DeviceID。上述设计都是soc在设计时决定的,Requester ID的传递对用户是透明的。

end

一口Linux

关注,回复【1024】海量Linux资料赠送

精彩文章合集

文章推荐