随着AI智算、HPC超算、AD/ADAS智驾、5G技术和超大规模网络等应用领域的快速发展,芯片设计正面临设计规模增长、功能集成度增加以及软硬件系统复杂度显著提升等多方面的变化。这些趋势不仅对芯片设计和验证工作的精确性和效率提出了更高的要求,也使得系统级设计和软硬件协同配合变得更加复杂。

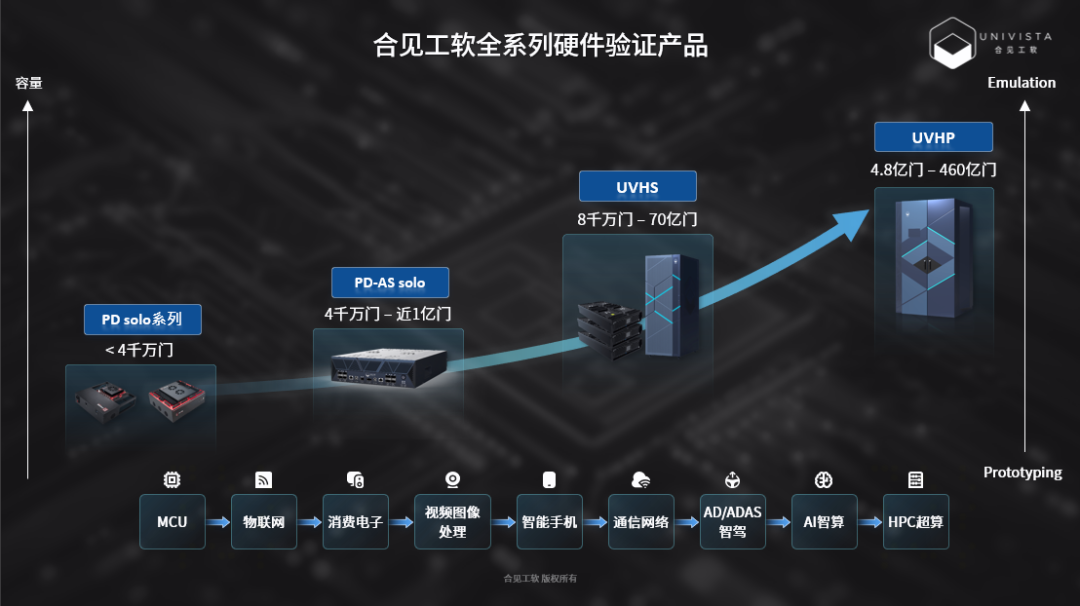

以合见工软的数字验证硬件平台来看,自成立以来历经了多代产品的演进与迭代,现如今已具备完整的全系列硬件验证产品线,包括了针对中小规模原型验证的Phine Design 系列(PD SOLO)、搭载AMD新一代Versal™ Premium VP1902 的单系统先进原型验证平台PHINE DESIGN Advanced Solo Prototyping(简称“PD-AS”)、适用于大规模ASIC/SOC 软硬件验证的全场景验证硬件系统UVHS、以及数据中心级超大容量硬件仿真加速验证平台UVHP系列,产品全线覆盖了从4千万到460亿逻辑门级别的原型验证及硬件仿真,可广泛应用于MCU、物联网、消费电子、视频图像处理、智能手机、通信网络、AD/ADAS智驾、AI智算、HPC超算等领域。

UVHS集成了自主研发的全局时序驱动的全自动化流程智能编译软件UVHS Compiler,能在单一系统中运行原型验证和硬件仿真两种不同模式,来应对复杂多样的SoC软硬件验证场景。还可以通过多台系统级联来支持多用户、多主机的多模式混合使用,有效解决了其他不同模式方案之间相互切换跨度大、难度高、效率低、时间久的难题,由此实现更高效、灵活的软硬件协同仿真,助力大规模芯片验证项目的快速收敛。UVHS适用于追求卓越运行性能的软件密集型的项目,其灵活的拆装组合功能便于进行性能调优,同时配备了丰富的硬件外设,使得在实验室或本地机房的部署更加便捷。

2024年推出的另一款重磅产品是数据中心级的硬件仿真加速平台UVHP,其主要特点是高密度,能够支持更大容量的硬件仿真需求。UVHP特别适合部署在异地远端机房、数据中心、公有云或私有云等场景中。通过合见工软针对本土客户需求的技术创新,UVHP能够更好地支持多用户,并实现灵活的动态资源分配。此外,UVHP的编译和运行过程是解耦的,即使项目中使用了众多物理形态的速率适配器或子卡,用户在编译时也不会受到接口物理位置的限制,运行时可以动态灵活地安排资源。

同时, UVHP使用了和UVHS相同的编译器软件,其流程和脚本都是通用的,包括高速接口速率适配器、存储模型套件、XTORs、接口子卡在内的外设也都可以通用的,因而用户的设计数据与环境可以在UVHS和UVHP间灵活迁移。

UVHP基于合见工软自主研发的新一代专有硬件仿真架构,采用先进的商用FPGA芯片、独创的高效能RTL综合工具UVSyn、智能化全自动编译器,以及丰富的高低速接口和存储模型方案,总体而言,其具备以下几方面的优势:

该平台将硬件仿真系统的算力提升至数据中心级别,为国产自研硬件仿真器中首家可扩展至 400亿逻辑门规模级别以上的产品,性能可与国际先进产品相媲美。

系统规模支持1.6亿门到460亿门资源灵活扩展调配。

编译与运行解耦,通过动态资源分配映射,已编译好的工程可灵活分配可用资源来运行。

支持多用户,最多可支持150个用户并发。

高效能的编译设计方法学,通过全自动高并发编译技术及参考增量编译技术,实现高效率编译及迭代。

支持多样化调试手段,包括Record & Replay, Save & Restore, RTP Trigger FVD(Full Visibility Debug), Fast FVD(FFVD)等。

同时,UVHP在配套的外设方案上,支持UV XTOR系列协议交易器、UV SA系列高速接口速率适配器、UV DC系列低速子卡等接口。此外,UVHP通过高达9TB的片外扩展存储来支持HBM3e、DDR5、LPDDR5、GDDR6、UFS4、eMMC5.1等丰富的UV MMK系列存储模型。为了满足硬件仿真中大量的调试需求,UVHP还提供了高达18TB的调试存储器,确保在各种使用模式下都能满足验证需求。

UVHP支持多种验证模式,包括纯硬件ICE环境、XTOR和Hybrid等方案,为芯片系统级软硬件协同设计及验证提供了强大的算力支持。结合合见工软的虚拟原型、数字仿真器、验证管理等既有产品组合,UVHP已全面覆盖数字芯片验证全流程的全场景需求,显著提升了项目的收敛效率。

除了UVHP,合见工软2024年还推出了另一款重要产品——商用级单系统先进原型验证平台PHINE DESIGN Advanced Solo Prototyping(PD-AS)。该平台搭载AMD新一代超大自适应SoC——AMD Versal™ Premium VP1902 Adaptive SoC,满足单片原型验证系统在亿门级产品领域的用户需求,能够灵活适应各种验证场景的需求。

从UVHS全场景硬件验证平台到最新的超大容量数据中心级硬件仿真平台UVHP,合见工软始终致力于解决用户面临的各种实际挑战。曹梦侠指出,合见工软的UVHS/UVHP旨在通过核心技术创新,缩短客户芯片验证项目的时间,从而加快产品上市进程。具体来说,合见工软主要从以下五个方面着手:

缩短功能验证的时间:Time-to-Functional-Signoff;

优化编译时间:Time-to-Bitfile;

提升运行性能以缩短任务执行时间:Time-to-Task;

缩短波形获取时间以加速调试收敛:Time-to-Waveform;

软件及系统开发左移,以缩短项目周期:Shift-Left。

在Time-to-Functional-Signoff方面,因为合见工软本身也是国内主流的IP供应商,提供了当前主流设计需要的各种高速接口IP和存储IP。

同样的,合见工软也有世界一流的存储控制器IP和存储模型开发团队,在合见工软成立以来陆续开发了DDR5/4/3、LPDDR5/4/3、HBM3e/3/2e、GDDR6等先进方案,用户群体广泛,也是合见工软主要的技术优势之一。

另外,合见工软在硬件平台上提供集成了IP和验证方案的Demo,客户可直接沿用方案作为参考设计,从而大幅降低集成的时间成本。

在Time-to-Bitfile方面,UVHS/UVHP共用了强大的智能编器译软件,其内置先进的时序分析引擎,可以从各个维度提升编译效率。

首先,采用并行编译技术,通过大量任务并行处理来缩短整体编译时间,这一策略贯穿整个编译流程。

其次,引入了Bringup模式,适用于项目初期。该模式允许硬件平台团队快速打通流程并生成bitfile,虽然在此过程中可能会牺牲部分性能和硬件资源,但能够在更短的时间内得到bitfile,使软件团队能够尽快启动任务。合见工软的研发团队突破了传统FPGA芯片的边界,深入到芯片内部的die级别,开发了多种die级别的算法。

第三,Performance模式在Bringup模式的基础上进一步优化,进行性能和面积的调优,从而提升硬件平台的运行效率。在这两种模式中,合见工软的编译器都配备了强大的自动分割引擎,使得大容量系统也可以从全局视角求解到最优的分割结果。

最后,参考增量编译技术能够更多地复用前次编译的结果和方法,从而进一步缩短编译时间。

在Time-to-Task方面,UVHS/UVHP开发了存档与恢复功能,显著提高了验证项目的整体运行效率。一方面,用户可以在特定的运行节点进行存档,之后重载之前的存档后,可加载不同的测试项,从而节省总体运行时间;另一方面,可以将较长的系统测试场景拆分成更小的段落,以更小的时间颗粒度进行分时复用,最大化硬件平台的使用效率。

在Time-to-Waveform方面,通过存档&恢复、录制&回放、实时触发和快速全波形等一系列高效调试组合拳,大幅缩短有效波形的获取时间,从而缩短整个调试周期。运行过程使能全信号可见模式能够直接生成波形,无需重新编译,大幅提升了调试效率。

在Shift-Left方面,统一的编译器可以让Emulation到Prototyping更丝滑的切换,在项目早期和中期使用Emulation模式进行RTL调试的快速收敛,初期的软件开发及测试任务在这个阶段即可进入。待中后期软硬件联调的任务量进一步加重后,Emulation的性能已然不够,这时候使用Prototyping模式可以更高性能运行,提升效率。如果遇到需要深度debug RTL的场景,又可以切回到Emulation去抓RTL波形来深挖底层的问题,这样一体双模的形式可赋能软件开发及调试快速收敛,缩短整个项目的周期。

以上是硬件平台上合见工软的诸多创新。同时,合见工软自研的虚拟原型平台UniVista V-Builder/vSpace提供了更高阶的方法学工具,使软件团队能够在项目早期、RTL尚未完善时便开始开发工作。该套件突破了传统的基于真实硬件的软件开发与测试限制,解决了软硬件解耦难题。UniVista V-Builder/vSpace可以进一步与UVHS/UVHP相结合,构筑芯片级全功能验证的混合平台UV Hybrid,借助虚拟原型及混合原型,可以让用户在开发效率、验证精确度、硬件资源使用成本等诸多需求上找到优化平衡点,进一步推动芯片产品加速面市。

除了硬件验证工具不断整合迭代,合见工软软件仿真验证平台也在不断升级完善,包括数字仿真工具UniVista Simulator (UVS) 、数字调试工具UniVista Debugger (UVD)和验证效率提升平台UniVista Verification Productivity System (VPS)。这些工具在2021年和2022年已陆续面市,去年合见工软对这些工具进行了版本升级,主要在功能上补足了特定场景下的特性增强,使其支持度更加全面。同时,性能提升方面也做了大量升级,目前这些工具已达到国内领先技术水平,下一步目标是向世界级一流产品看齐并实现超越。

合见工软将持续通过数字验证全流程的创新,为芯片设计行业赋能,加速HPC超算、AI智算、AD/ADAS智驾、智能手机、5G通信等新质生产力的可持续发展和创新进程。

关于合见工软

上海合见工业软件集团有限公司(简称“合见工软”)作为自主创新的高性能工业软件及解决方案提供商,以EDA(电子设计自动化,Electronic Design Automation)领域为首先突破方向,致力于帮助半导体芯片企业解决在创新与发展过程中所面临的严峻挑战和关键问题,并成为他们值得信赖的合作伙伴。

了解更多详情

请访问www.univista-isg.com。

点击“阅读原文”,立即访问合见工软微官网~