FPGA学了好几天终于有点感觉了,就好像以往的所有事情一样,谜底就在谜面上。

就好像学任意一个MCU一样,一套完整的流程很重要。但是没有任何一个器件是FPGA这么看重流程的。

我们先不说FPGA这个事情,说和它连接的器件。

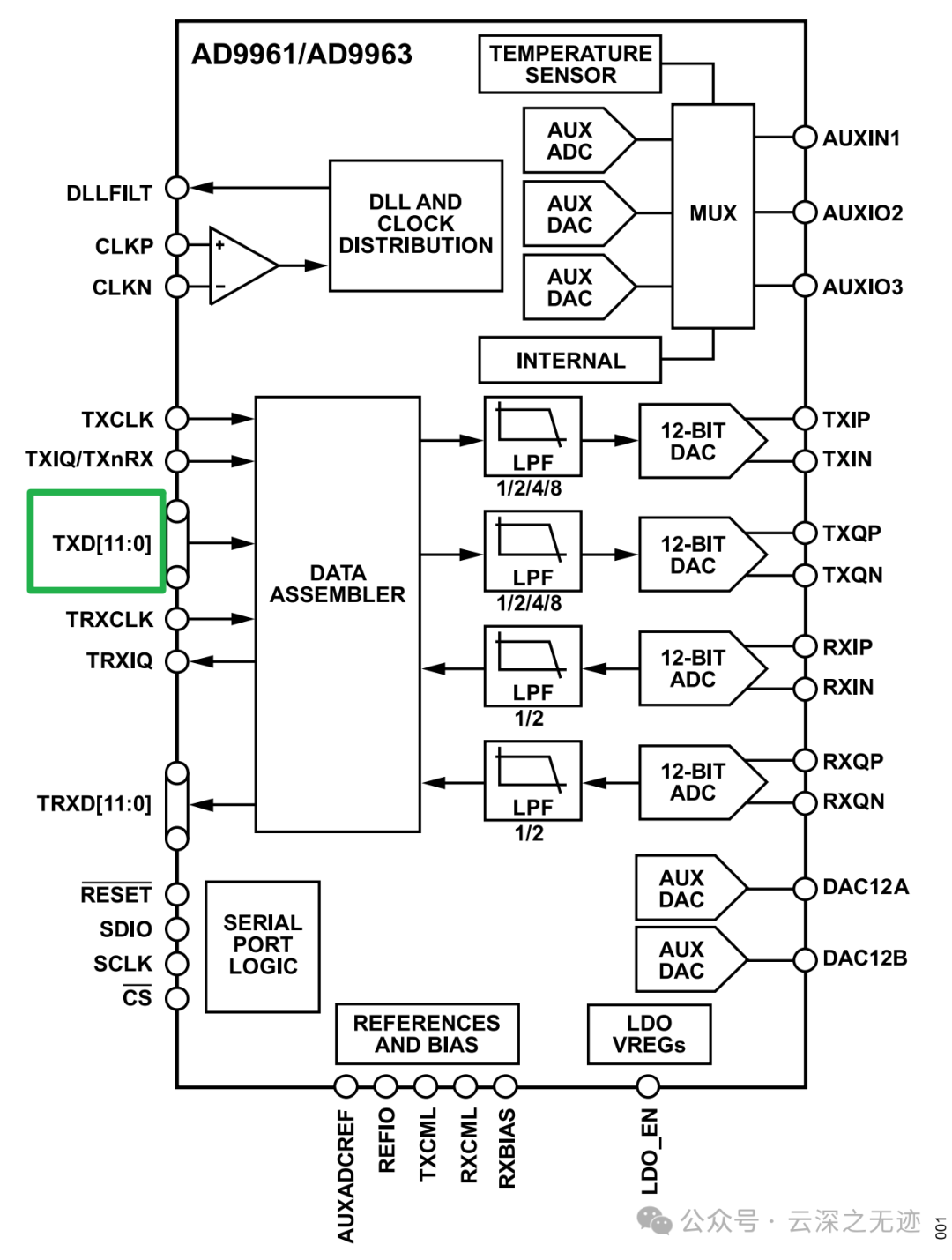

一个RF的器件

上层打交道的东西就是IO,这个IO关注两个部分。

1,电气性能,是输入还是输出,上面的电压,阻抗情况

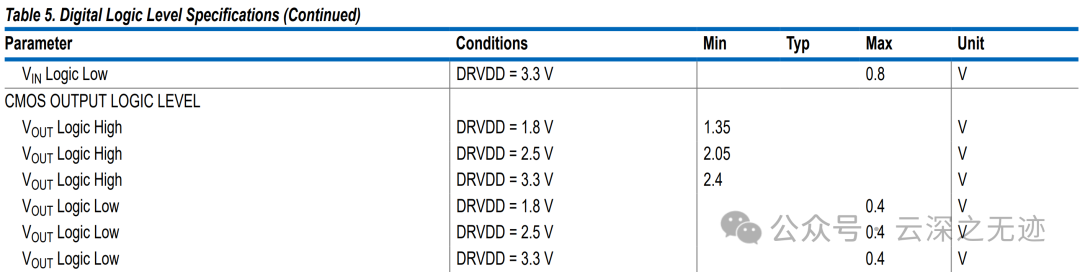

这就是所谓的CMOS电平,它规定了稍微的电压信号是什么样子的

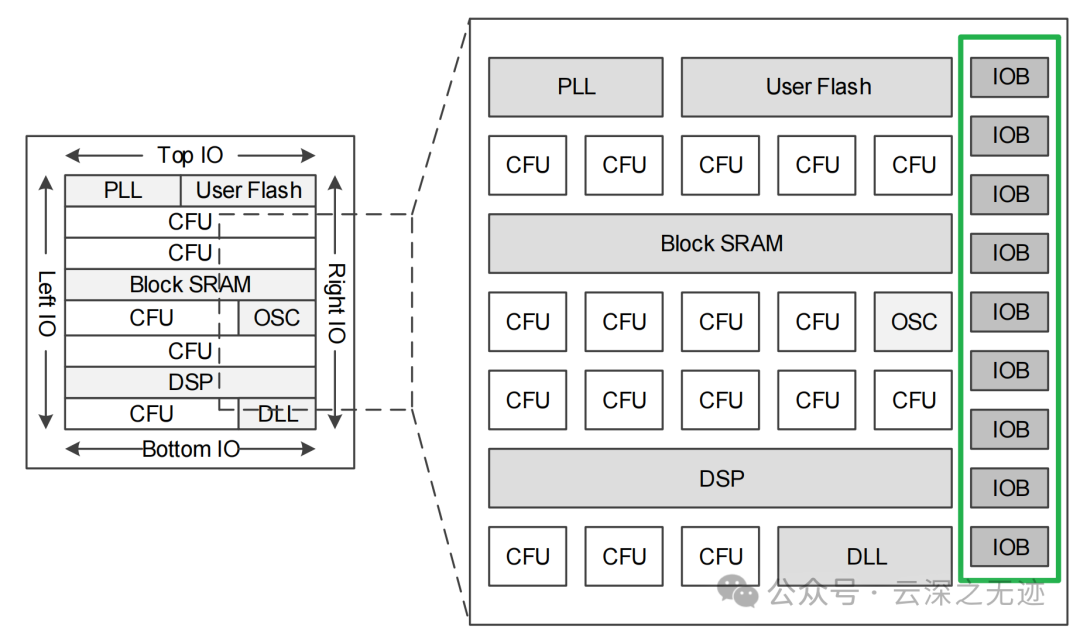

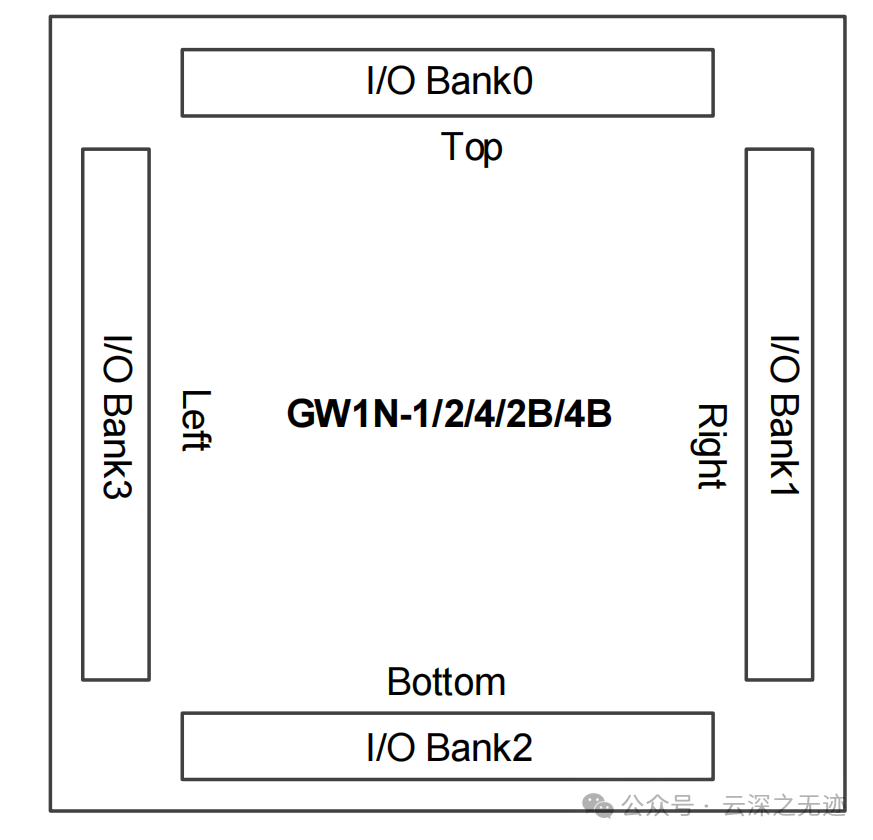

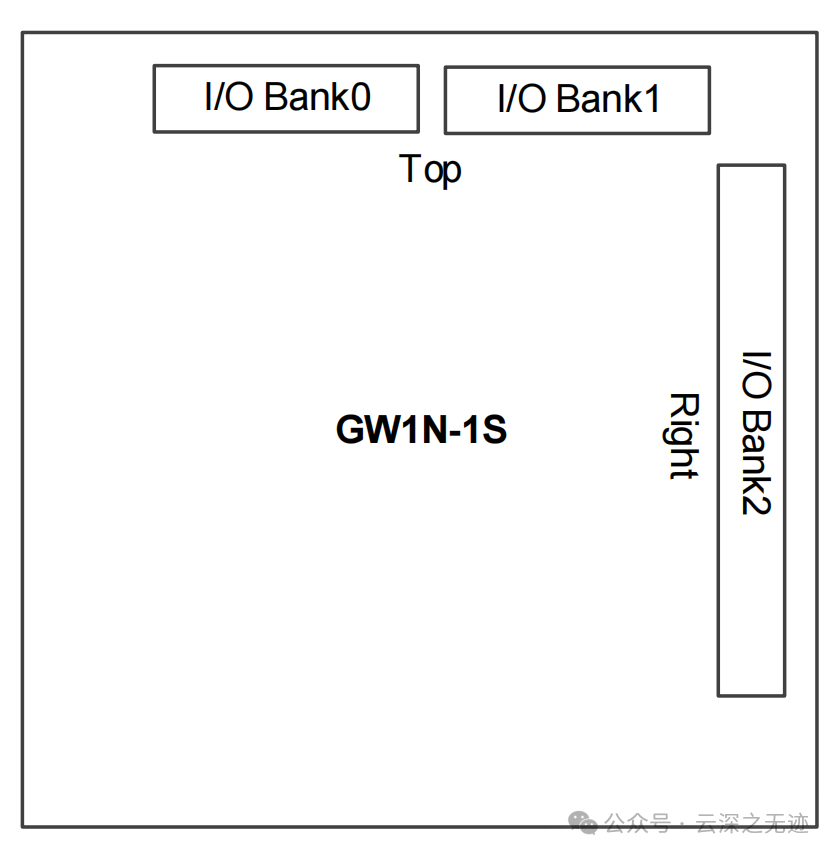

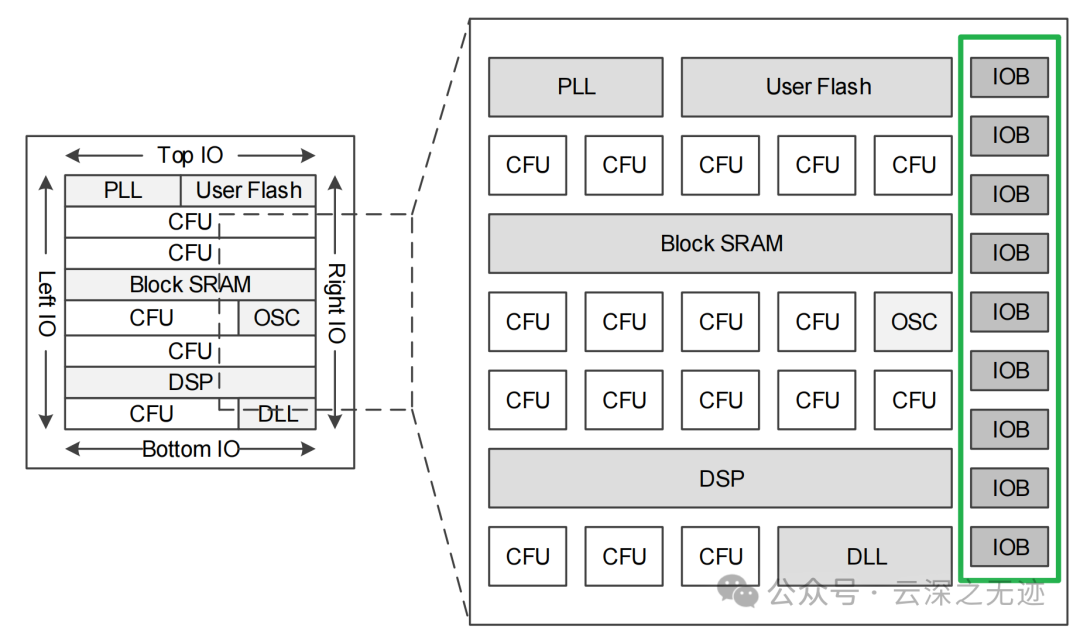

在FPGA里面和外部器件连接的就这些IO,因为是物理层面的事情,所以一定要FPGA的物理层面支持,一般在FPGA里面叫Bank,就是把有共性的IO放一起,也方便走线。

就是这样的

还有这样的

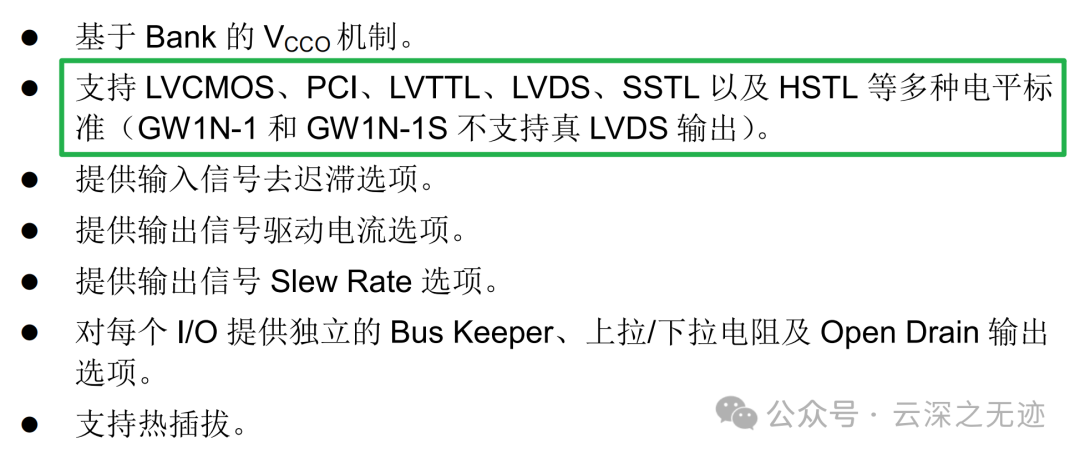

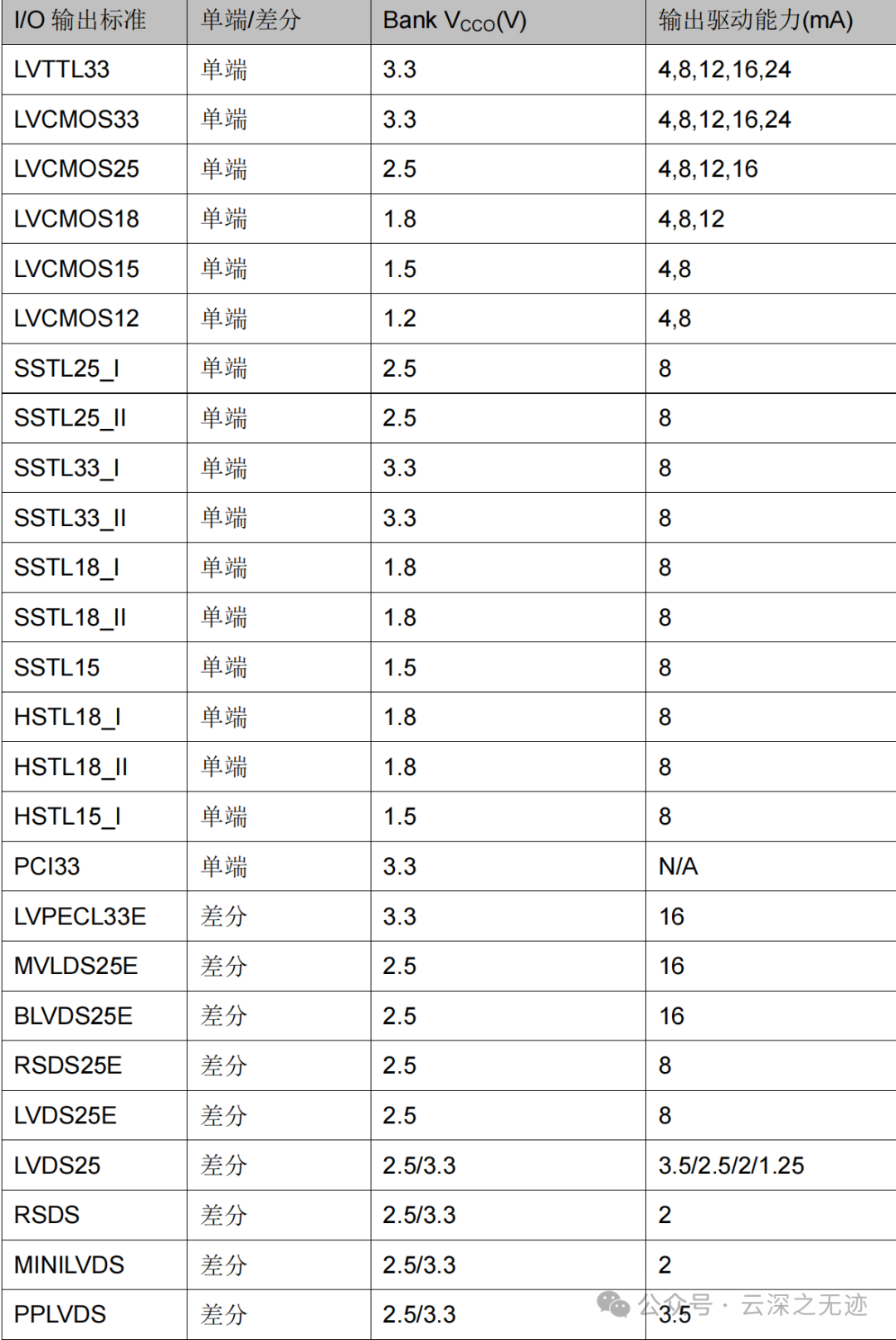

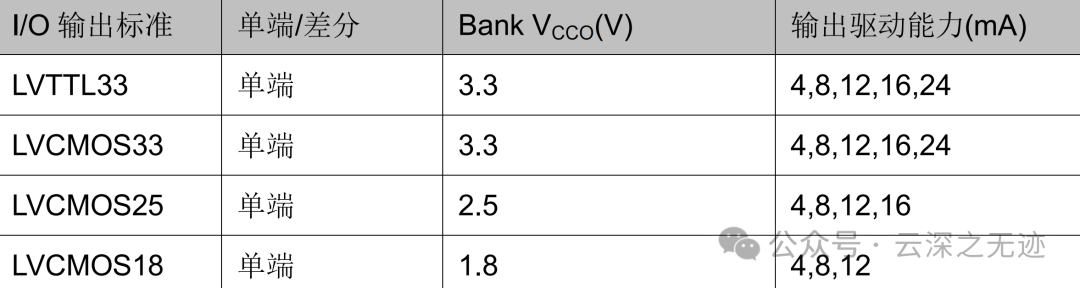

在数据手册一般都会说成这样,有各种特性,我画住的就是电平标准

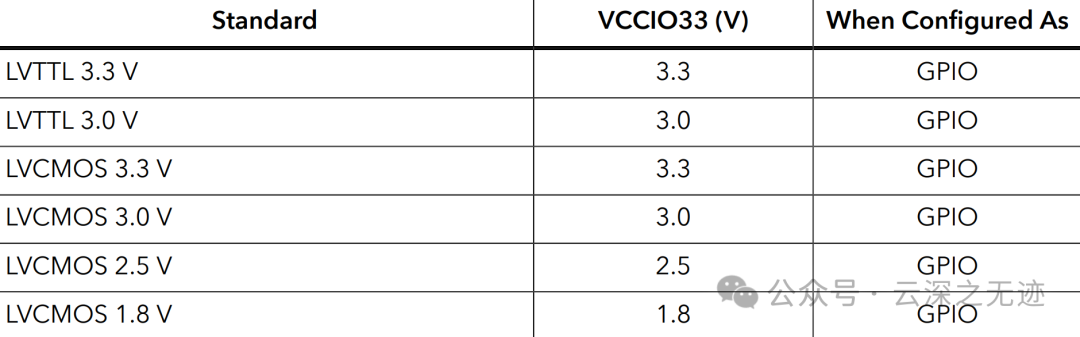

这个东西就是告诉你,FPGA上面的引脚支持什么样的电平标准,一定和驱动的电平标准一样。

TI60F100

各种各样

不同器件的电平标准不同: 不同的芯片或器件使用的电平标准可能不同,为了兼容这些器件,FPGA的IO引脚需要支持多种电平标准。

不同应用场景的需要: 不同的应用场景对信号的电平要求也不同。例如,高速数字电路可能需要LVDS等低压差分信号,而一些低速的模拟信号则可能需要更高的电压。

比如我们的SPI和IIC就是这样的

如果我们输出的信号的话,比如一些差分信号,就需要电流驱动,也就是驱动电流。驱动长线、高负载的器件需要更高的驱动能力。

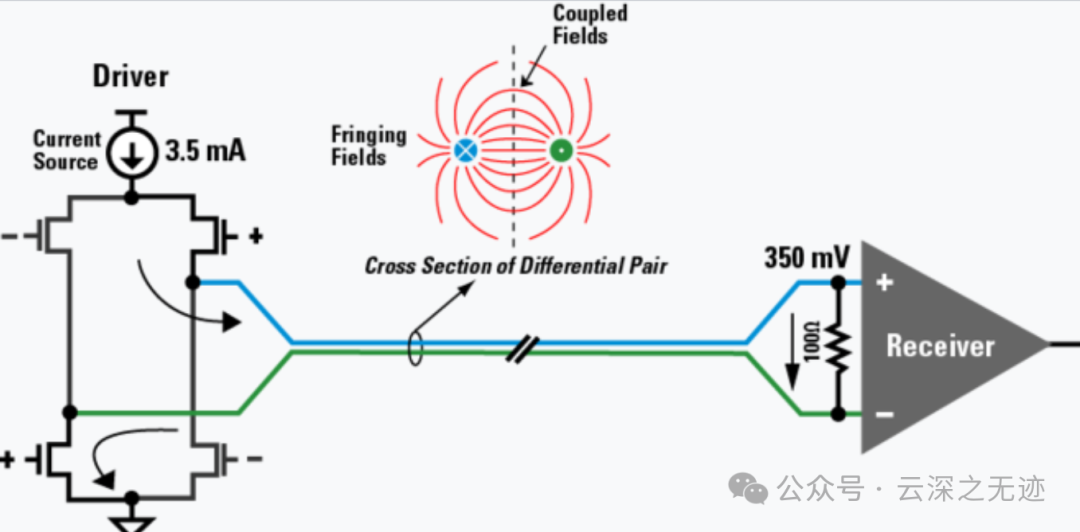

差分信号: 许多FPGA的IO引脚支持差分信号,如LVDS,这种方式可以有效地抑制噪声,提高信号的抗干扰能力。

单端信号: 对于一些对噪声要求不高的场合,可以使用单端信号,但需要注意抗噪措施。

LVTTL: 低电压TTL,是一种常用的TTL电平标准。

LVCMOS: 低电压CMOS,是一种低功耗的CMOS电平标准。

LVDS: 低电压差分信号,是一种高速、低功耗的差分信号标准。

HSTL: 高速传输标准逻辑,是一种高速串行接口标准。

PCI Express: 一种高速串行总线标准。

这些是常见的电平标准。

反正就是考虑的事情多

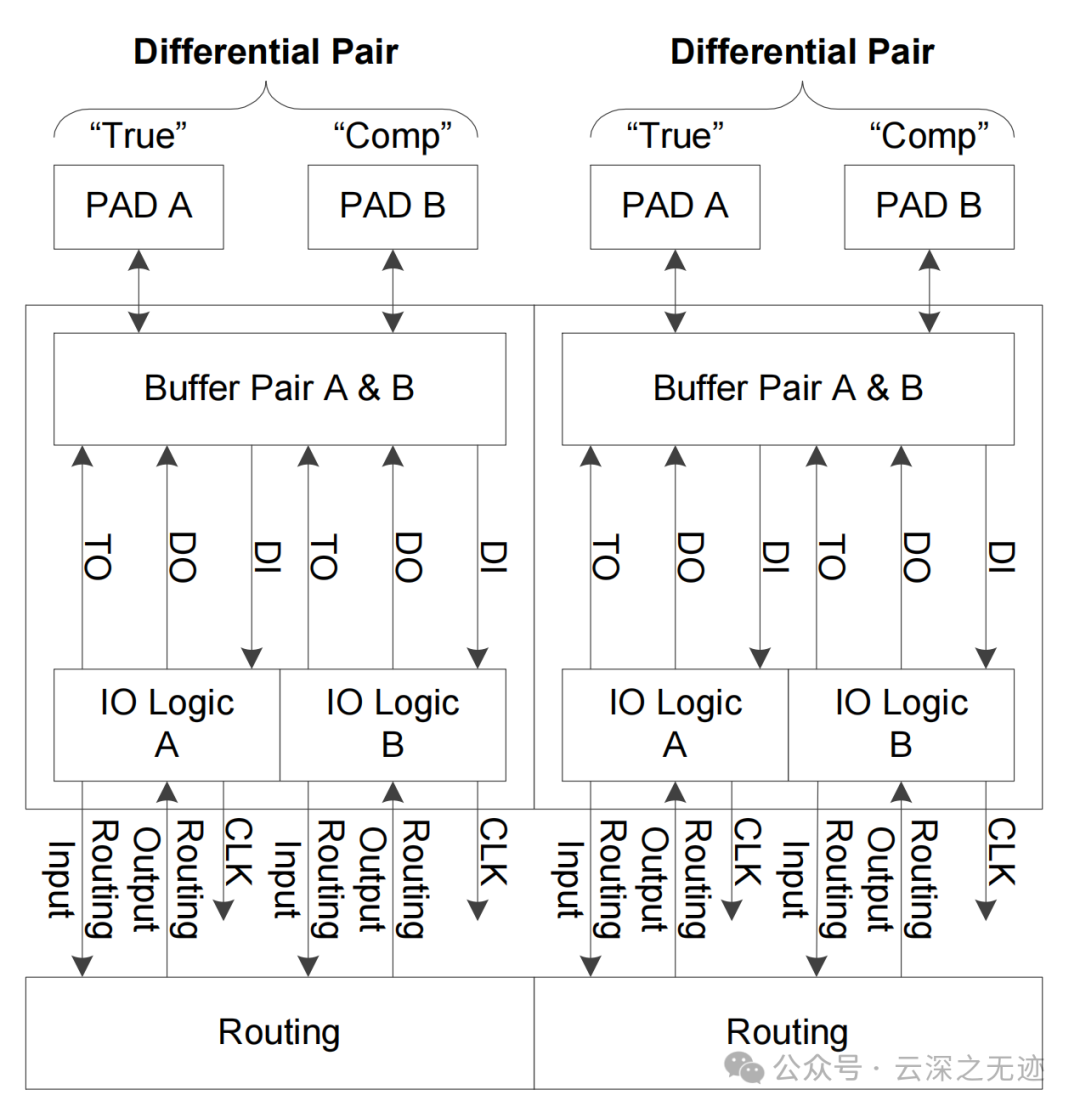

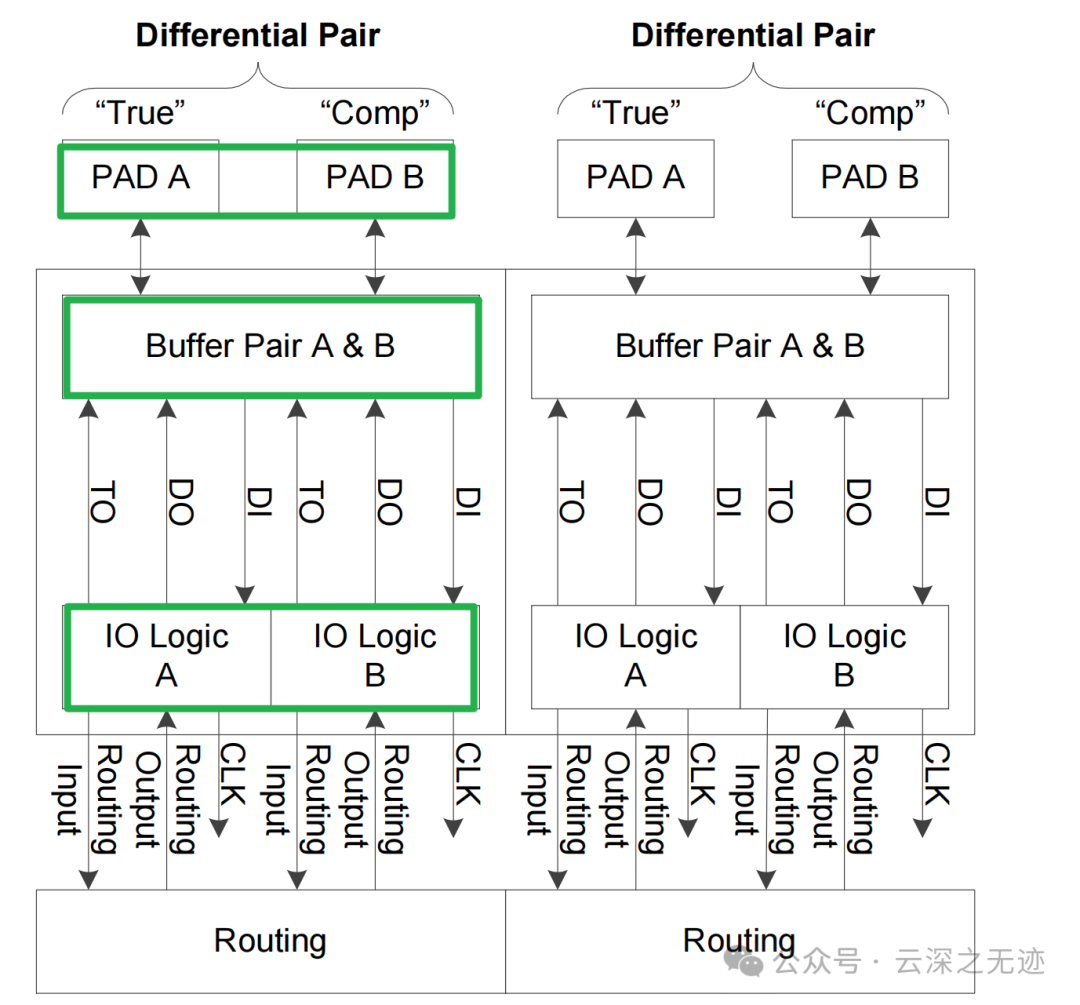

这么复杂的IO肯定在内部也是实现起来复杂的,但是都围绕着输出和输入两个事情设计的,它主要负责FPGA与外部电路之间的信号交换。

计算机里面分层这个哲学思想永不过时

实现FPGA里面最大的拦路虎就是线多(也就是信号),所以读懂上面的结果就一定要对这些信号有了解。

Differential Pair(差分对):

True 和 Comp:分别表示差分对的真值和补值。差分信号通过这两根线传输,具有较强的抗噪性。因为现在很多器件为了高速收发都要这样的差分结构。抗干扰是永恒的话题。

PAD A 和 PAD B:FPGA芯片的物理引脚,用于连接外部电路。就是PCB拉线时候的真引脚。

Buffer Pair A & B:缓冲对,用于驱动差分信号,提供足够的驱动能力。

IO Logic:输入输出逻辑,负责对输入信号进行处理,并产生输出信号。

Routing:路由,用于连接IO Logic与FPGA内部的逻辑单元。

DI, DO, TO, CLK:分别表示数据输入、数据输出、时钟输入、时钟输出。

现在看就清楚多了

信号输入: 外部差分信号通过PAD A和PAD B输入到FPGA。

缓冲放大: 信号经过缓冲对放大,提高驱动能力。

IO Logic处理: 信号进入IO Logic进行处理,可能涉及电平转换、缓冲、等化等。

内部路由: 处理后的信号通过内部路由连接到FPGA内部的逻辑单元。

信号输出: FPGA内部的信号通过IO Logic处理后,从PAD A和PAD B输出。

可以看到就是围绕我们的IO设计的,这些是细节。

更宏观一些呢?

差分信号传输: 采用差分信号传输,可以有效抑制噪声,提高信号的抗干扰能力。

灵活的配置: 通过配置IO Logic,可以实现各种各样的输入输出功能,如LVDS、LVTTL等。

高可靠性: 缓冲对和IO Logic的设计保证了信号的完整性。

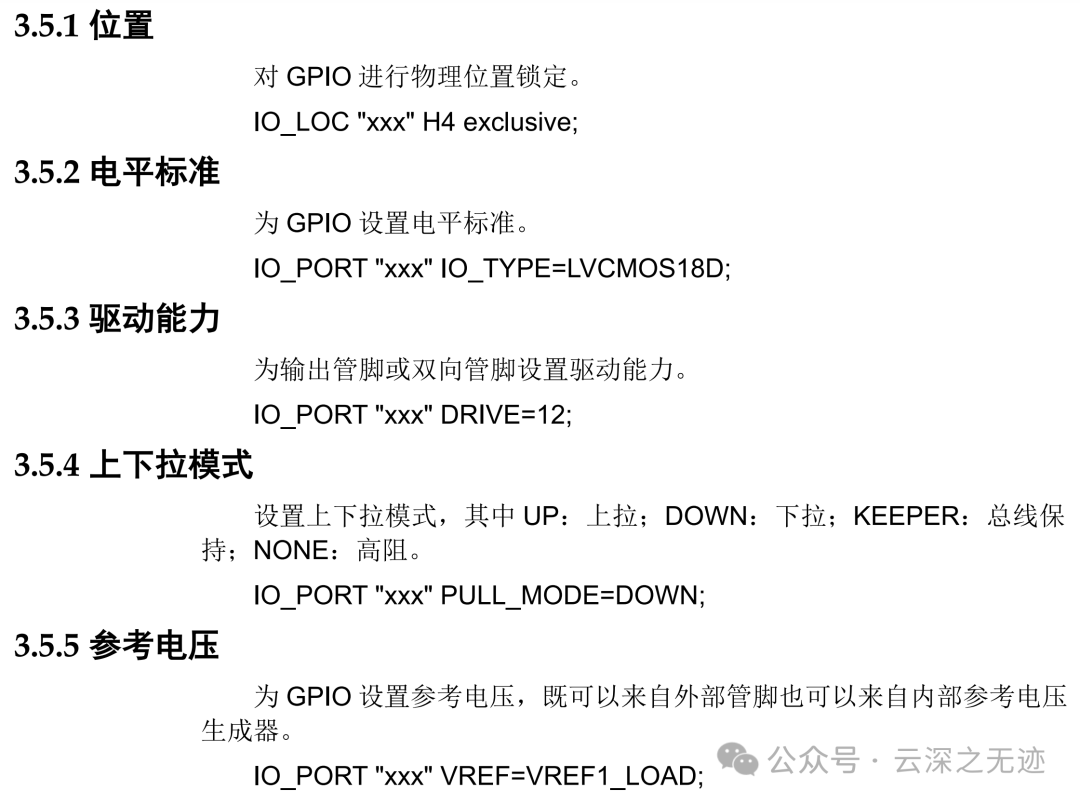

在FPGA的设计后面有一步骤是引脚的映射,因为内部处理的是数据,01而已,但是和物理打交道需要IO,所以要选择引脚(也就是电平标准)。

专业说法叫:物理约束通常被称为布局约束或物理约束文件。这些约束文件用于指导FPGA综合工具和实现工具,将设计中的逻辑单元和I/O引脚映射到FPGA芯片的物理位置上。

管脚约束: 指定设计中的信号与FPGA芯片的物理引脚的对应关系。

区域约束: 将设计中的模块或逻辑块约束到FPGA的特定区域。

时钟约束: 定义时钟信号的频率、相位等信息。

电气约束: 定义输入输出信号的电气特性,如电压、电流等。

就是做这个

OK,其实现在为止我们都知道了硬件的奥秘,再深入一些。

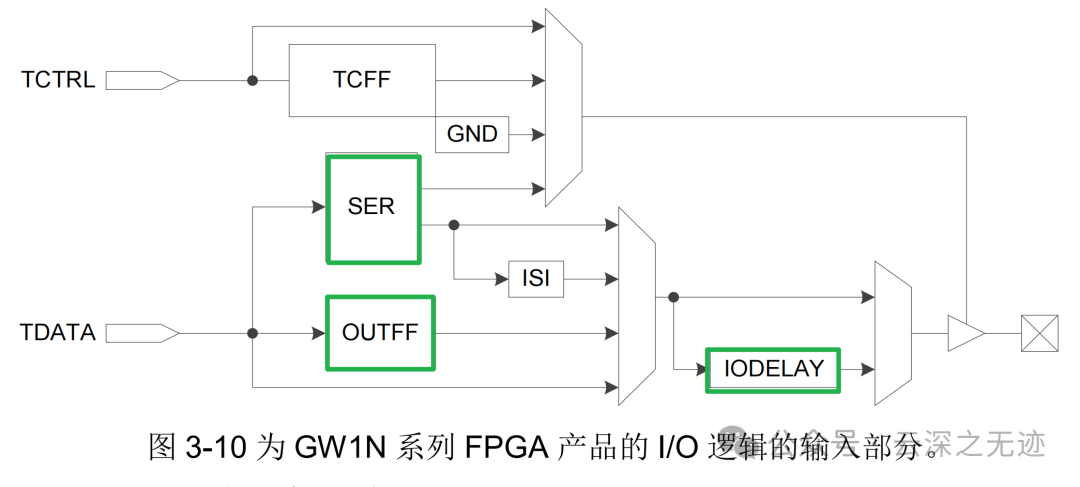

和单片机一样,也是输入的结构是什么样的

先看信号线!

TX: 外部输入信号

D: 外部输入信号

TO: 输出信号

DO: 输出信号

OTMUX: 输出多路复用器,选择输出信号的来源

TRIREG: 三态寄存器,用于控制输出信号的使能

Q1,Q0: 寄存器输出

OSER: 输出串行器,将并行数据转换为串行数据

ODMUX: 输出多路分离器,将多个信号源选择一个输出

ISI: 输入串行接口

OREG: 输出寄存器

IODELAY: 输入输出延迟单元

输入逻辑: 对输入信号进行处理的逻辑单元

因为信号进来可能太快,后面就需要延时一下,然后就是可以通过串并转换来转换信号:

这个就是并的信号进来了,要转换成一个串行的信号来处理

外部信号输入: 外部信号通过TX和D输入到FPGA。

信号处理: 输入信号经过输入逻辑处理,包括电平转换、缓冲等。

寄存器暂存: 处理后的信号可能被存储在寄存器中,如Q1和Q0。

多路选择: 通过OTMUX和ODMUX,可以对多个信号源进行选择,实现不同的功能。

串并转换: OSER将并行数据转换为串行数据,ISI将串行数据转换为并行数据。

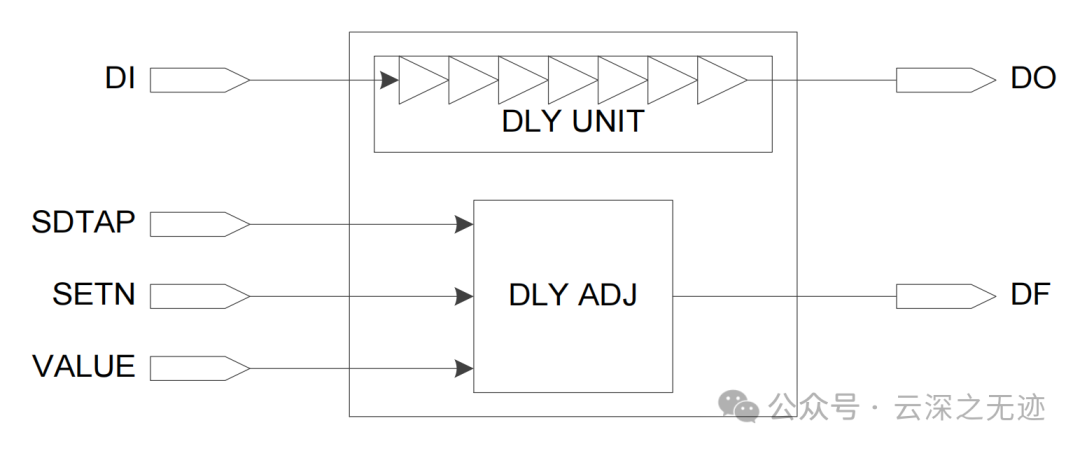

延迟调整: IODELAY可以对信号进行延迟调整,以满足时序要求。

输出: 最终的输出信号通过TO和DO输出。

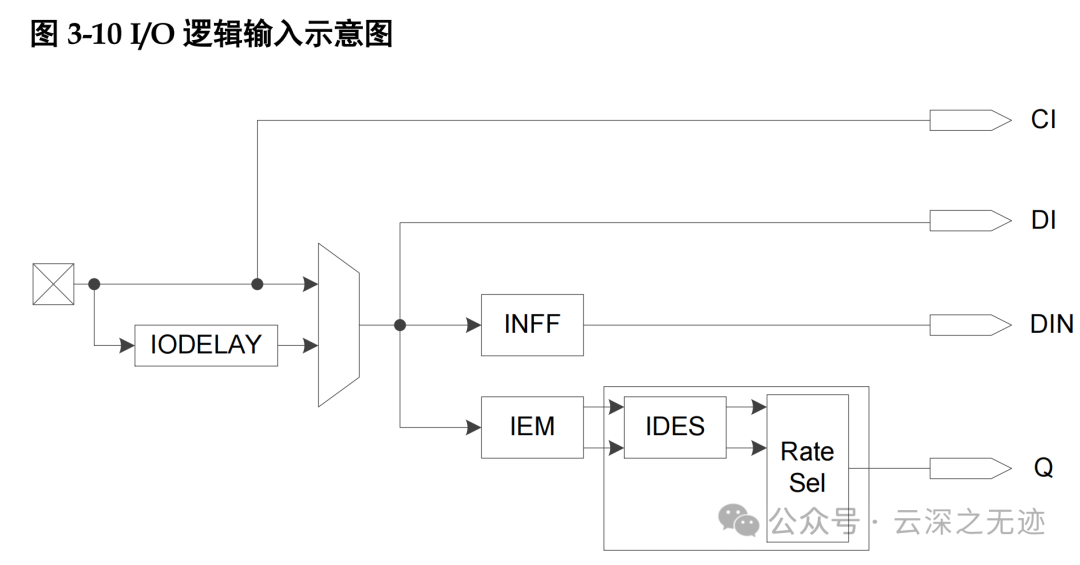

还有一个对偶的结构-输出

PAD: FPGA的物理引脚,用于连接外部电路。

IDELMUX: 输入数据多路复用器,可以从多个输入源选择数据。

IODELAY: 输入延迟单元,用于调整输入信号的延迟,以匹配FPGA内部的时钟。

IREG: 输入寄存器,用于锁存输入数据。

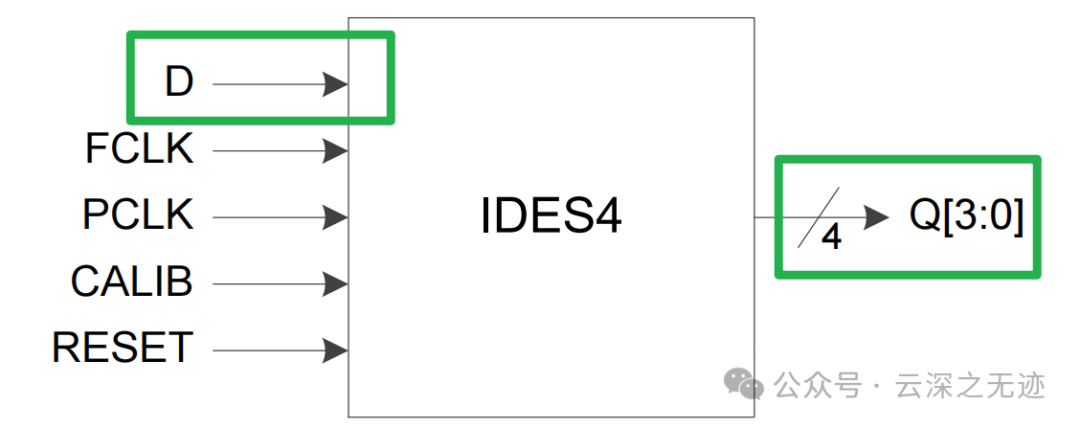

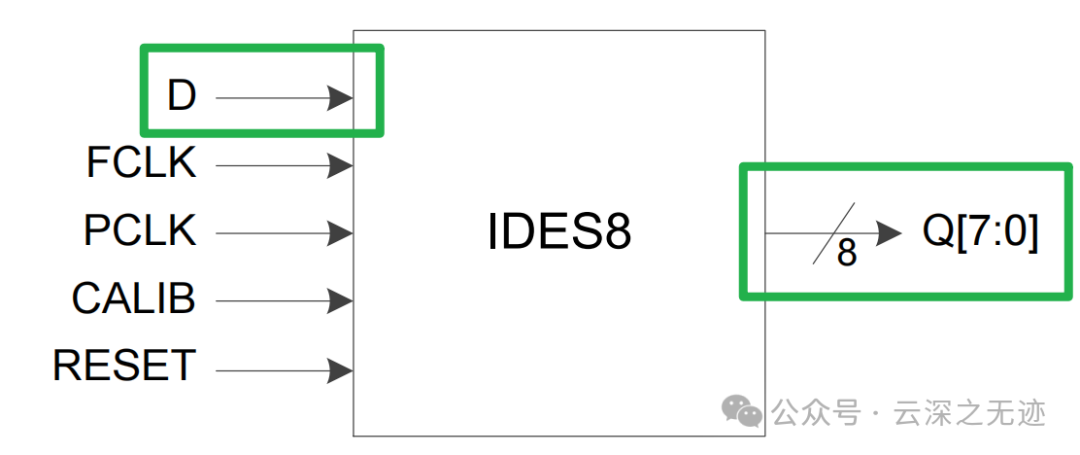

IDES: 输入数据选择器,用于选择多个输入数据源。

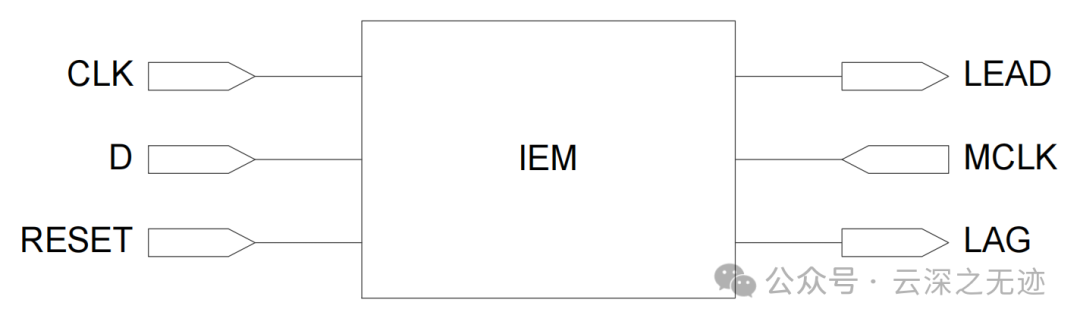

IEM: 输入使能,控制输入数据的有效性。

LAG/LEAD: 延迟单元,用于调整信号的相位。

CI: GCLK输入信号,不能直接连接到Fabric(FPGA内部逻辑),通常用于时钟信号。

DI: 数据输入信号,直接输入到Fabric。

Q: 寄存器输出,即经过处理后的数据。

反正就是这样的,信号进来或者粗去都会做一些处理,就是缓存,分流或者转换。

这个是里面的延迟模块

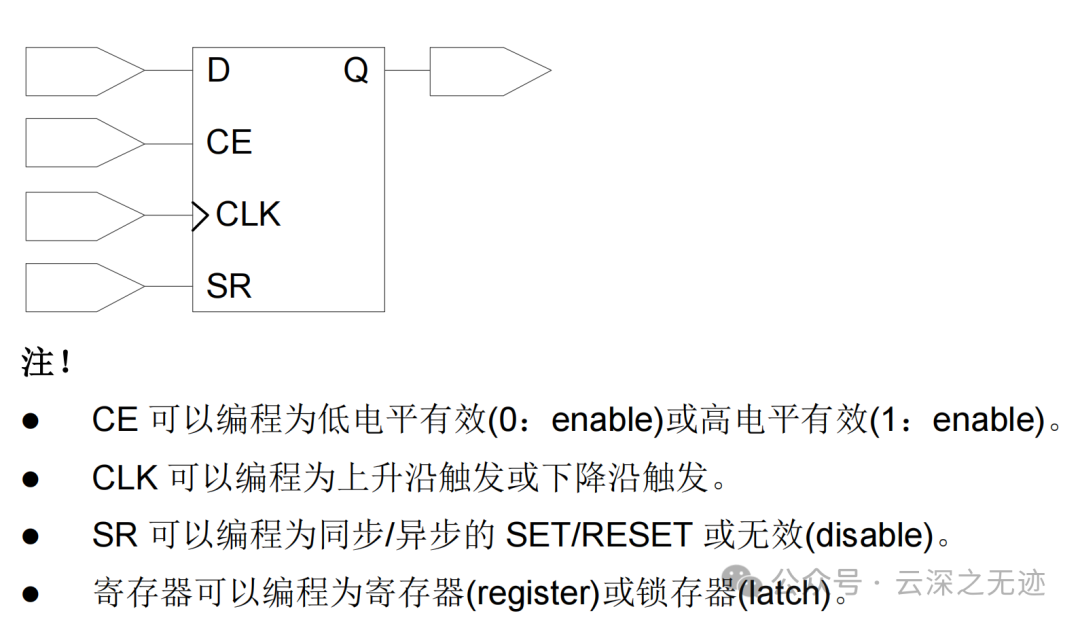

还有寄存器,可以备注成不同的用途

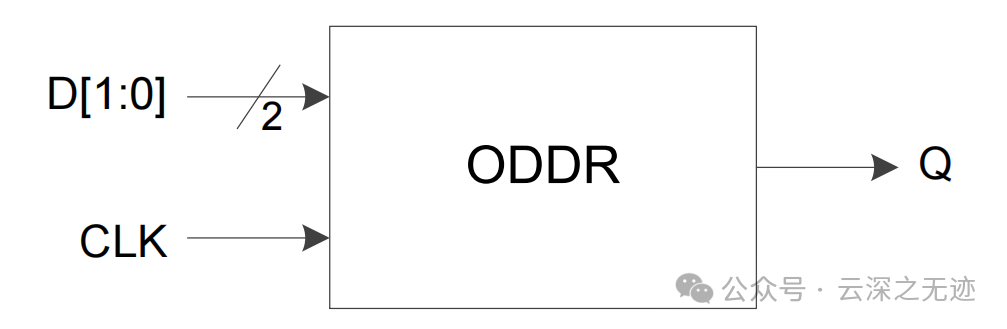

也可以把两个数据合成一路,就是双边沿取样

一段抽象的话

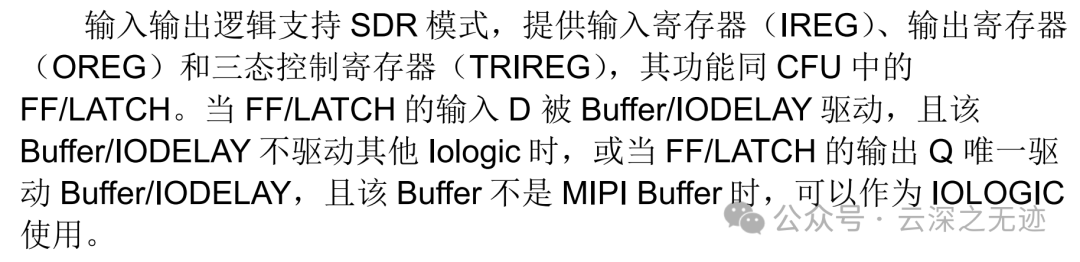

数据输入: 外部数据通过输入引脚进入FPGA,经过输入寄存器IREG锁存,确保数据在时钟沿的稳定性。

内部处理: 锁存后的数据在FPGA内部进行各种逻辑处理。

数据输出: 处理后的数据通过输出寄存器OREG输出,并通过三态寄存器TRIREG控制输出的使能。

上面出现了一个三态寄存器,三态寄存器是一种特殊的寄存器,除了常见的逻辑“0”和“1”两种状态外,还具有高阻态(High Impedance)这一状态。这种高阻态相当于断开了与外部电路的连接,使得该引脚对电路没有影响。

数据总线共享: 多个设备可以共享一条数据总线,当某个设备需要向总线输出数据时,其他设备的输出端置为高阻态,避免数据冲突。

信号隔离: 在某些情况下,需要将某个模块的输出与其他模块隔离,以避免相互干扰。

灵活控制: 通过控制三态寄存器的使能信号,可以动态地控制输出状态,实现不同的功能。

上面就是说了硬件的问题,可以通过IO把数据取回到FPGA内部,现在就要对这些数据做处理。

我们这里需要看一个概念叫原语!

逻辑门: AND、OR、NOT、XOR等基本逻辑门。

触发器: D触发器、T触发器等。

RAM/ROM: 用于存储数据的存储单元。

乘法器: 用于进行乘法运算。

比较器: 用于比较两个数的大小。

时钟相关组件: 时钟缓冲器、时钟分频器等。

I/O端口: 与外部电路连接的端口。

这些就是我们里面的积木块。

说一下为什么要有这些东西,比如我们外面有个8并的线,我们要采集串行的数据,那就找一个并转串的原语,硬件上面设置好电平标准。我们就可以在一个元语的信号线上面拿到数据。

使用的步骤:

例化: 在HDL代码中,通过例化原语来创建相应的硬件逻辑。

参数配置: 根据需要配置原语的参数,如宽度、深度、工作模式等。

连接: 将不同原语的输出和输入连接起来,形成完整的电路。

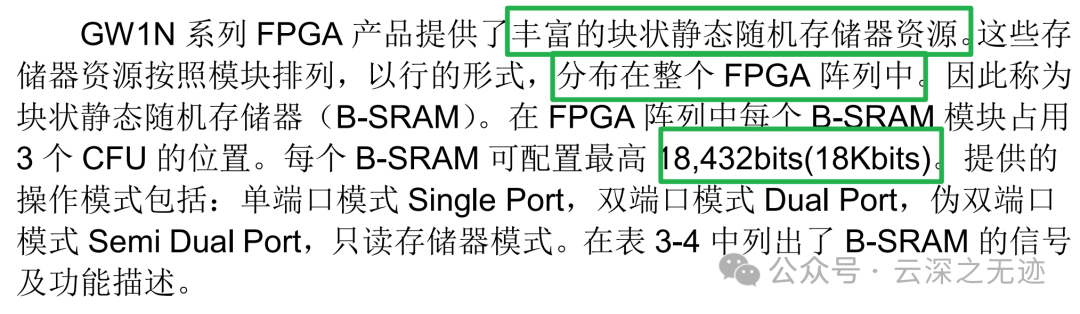

接下来说下一个资源,就是块SRAM

接下来说下一个资源,就是块SRAM

就是这个东西

小猪脑袋看不清

他就是一块固定的存储器

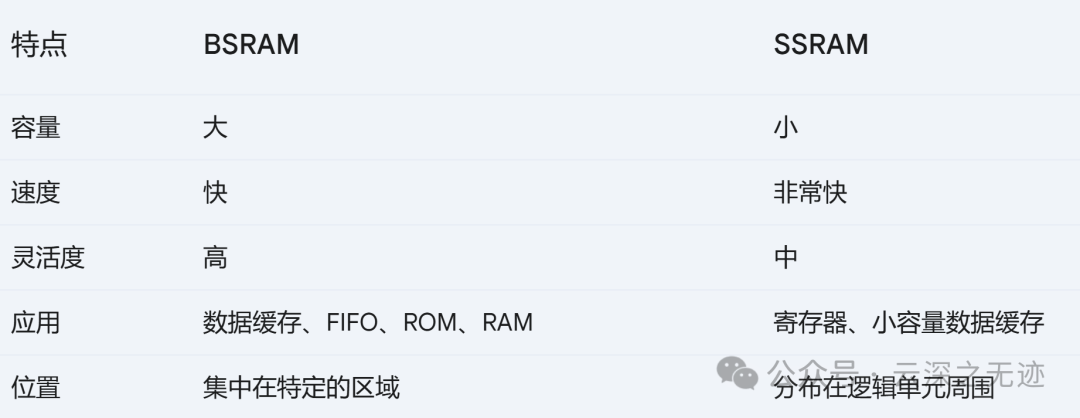

学学特性

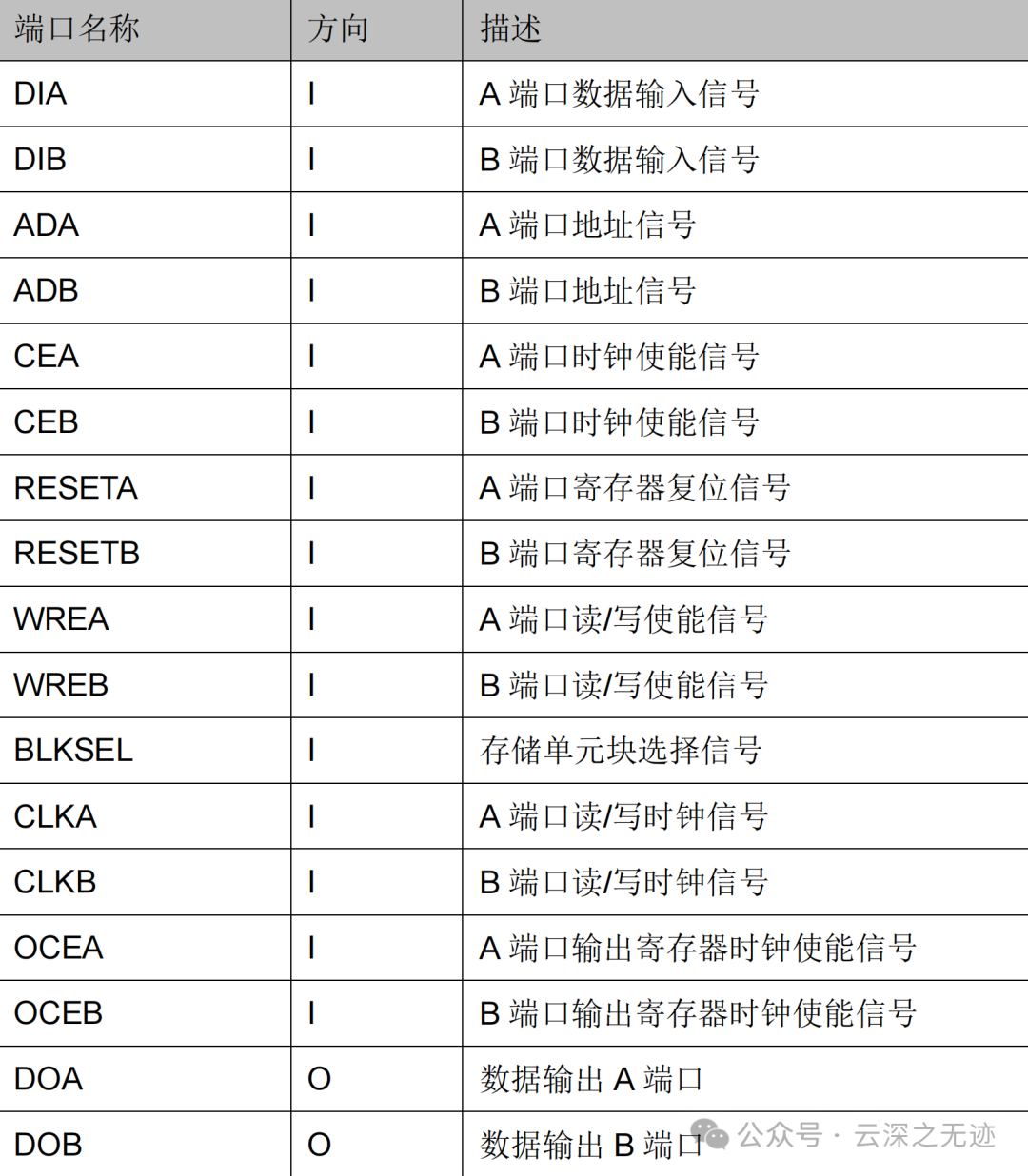

模块上面有很多信号线

数据输入输出: DIA、DIB为数据输入,DOA、DOB为数据输出。

地址选择: ADA、ADB用于选择要访问的存储单元。

时钟控制: CEA、CEB、CLKA、CLKB等信号用于控制读写时序。

复位控制: RESETA、RESETB用于将B-SRAM复位到初始状态。

块选择: BLKSEL用于选择要操作的存储单元块。

这个是对线的分类,说说原理:

地址寻址: 通过ADA或ADB信号指定要访问的存储单元地址。

数据写入: 当写使能信号(WREA或WREB)有效时,数据从DIA或DIB输入到指定的存储单元。

数据读取: 当读使能信号有效时,存储单元中的数据被读出到DOA或DOB。

时钟控制: 时钟信号控制数据的读写操作,确保数据的同步。

你有没有想过一个模块,为什么这么多信号线。

数据输入输出信号(DIA, DIB, DOA, DOB): 这些信号直接负责数据的输入和输出,是B-SRAM进行数据交换的通道。

地址信号(ADA, ADB): 用于指定要访问的存储单元的地址,就像内存中的地址一样,通过地址信号可以精确地定位到想要读写的数据。

时钟信号(CLKA, CLKB, OCEA, OCEB): 时钟信号控制数据的读写时序,确保数据的同步。不同的时钟信号可以实现异步操作或者不同时钟域之间的通信。

使能信号(CEA, CEB, WREA, WREB): 这些信号用于控制B-SRAM的读写操作。例如,写使能信号有效时,数据才会被写入B-SRAM。

复位信号(RESETA, RESETB): 用于将B-SRAM复位到初始状态,清除所有数据。

块选择信号(BLKSEL): 如果B-SRAM有多个存储块,则通过该信号选择要操作的存储块。

就是不同的功能就是不同的信号线,以将B-SRAM想象成一个多功能的仓库。每个信号就像是一个控制开关,控制着仓库门的开关、货物的进出、货物的存放位置等。通过合理地组合这些开关,可以实现对仓库的各种操作,如存货、取货、盘点等。

别的模块其实也是如此。

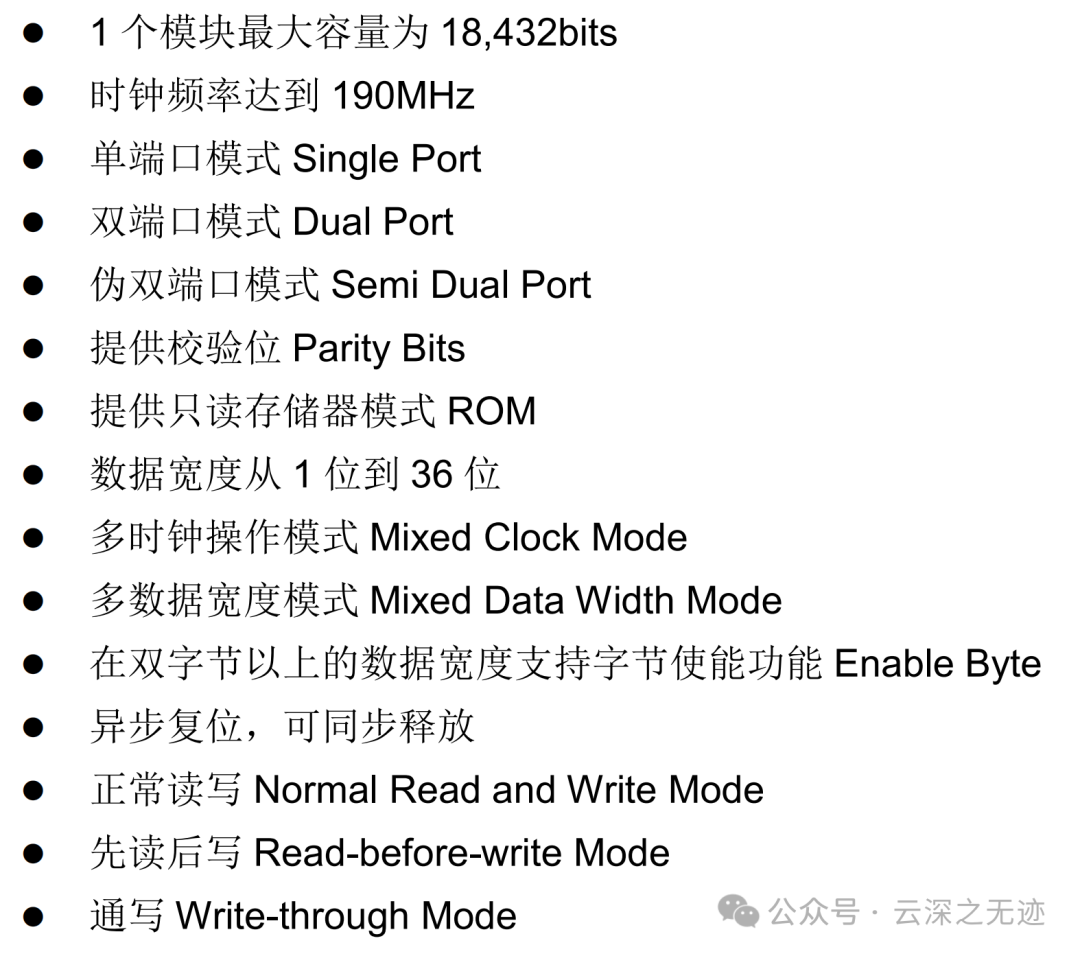

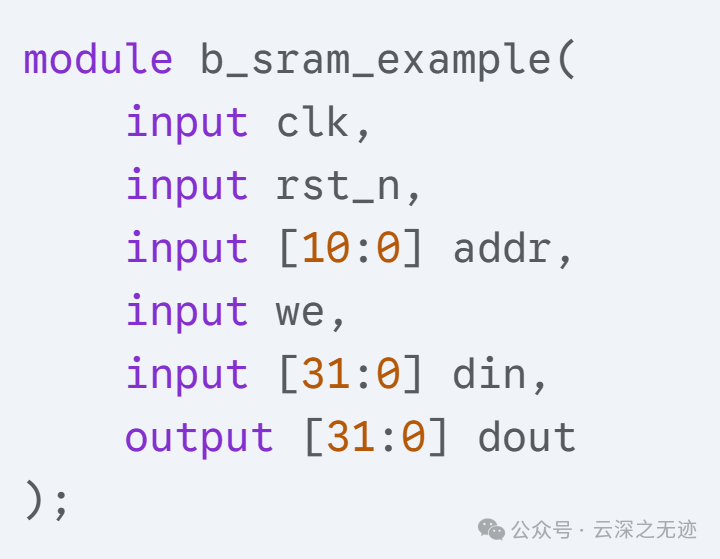

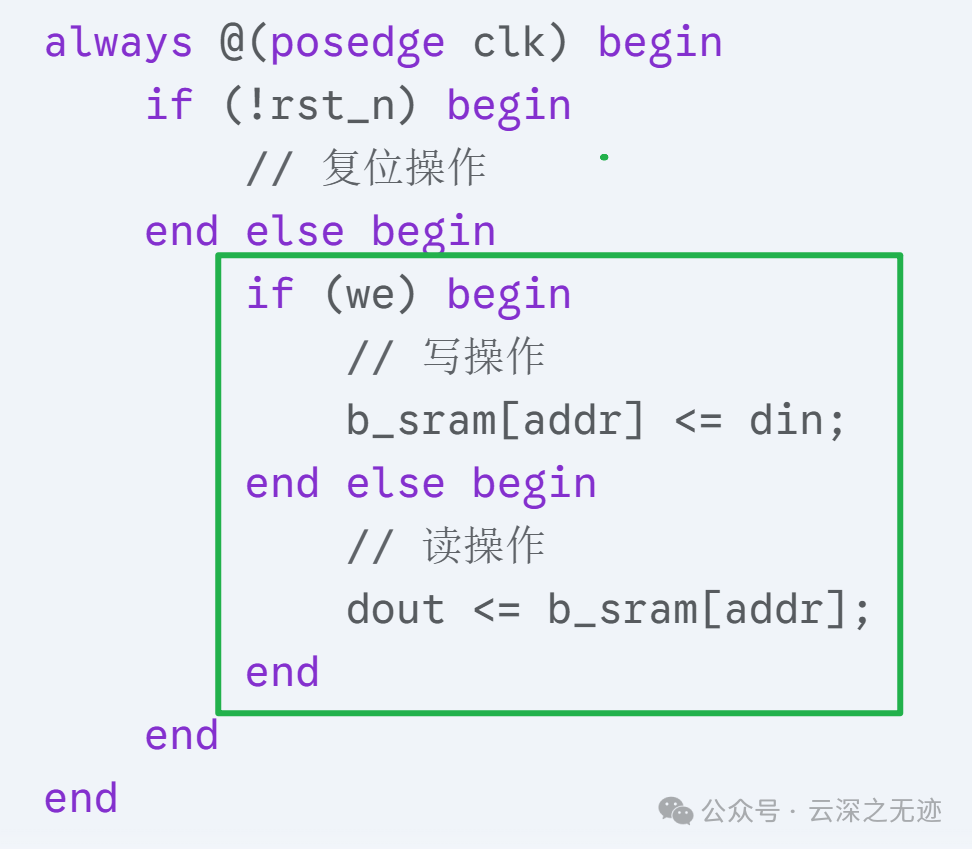

我们先把这个模块的输入和输出写好

这个意思就是说在一个时钟边沿来的时候,如果重启信号没有,如果有写信号,那就把这个din数据给到SRAM的ADDR处,下面也一样。

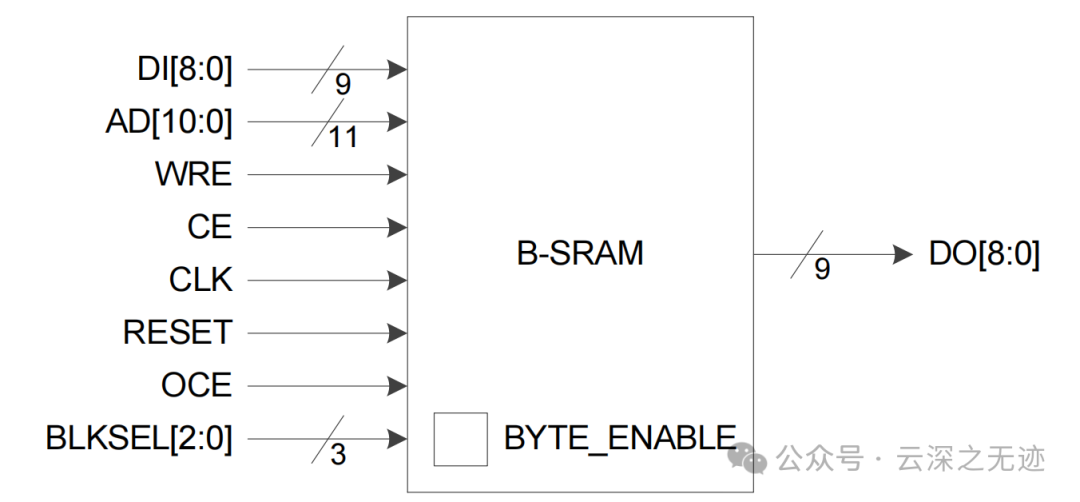

一个单端口的模块长这样

单端口模式意味着在同一时刻,只能对B-SRAM进行读或写操作,不能同时进行读写。也就是说,B-SRAM只有一个访问接口。

并发性较低: 无法同时进行读写操作,限制了系统的并发性。

数据输入输出:

DI[8:0]:9位数据输入端口,用于向B-SRAM写入数据。

DO[8:0]:9位数据输出端口,用于从B-SRAM读取数据。

地址输入:

AD[10:0]:11位地址输入端口,用于指定要访问的存储单元的地址。

控制信号:

WRE:写使能信号,高电平时有效,表示进行写操作。

CE:时钟使能信号,高电平时有效,表示允许读写操作。

CLK:时钟信号,控制读写操作的时序。

RESET:复位信号,用于将B-SRAM复位到初始状态。

OCE:输出寄存器使能信号,控制输出寄存器的使能。

BLKSEL:块选择信号,用于选择要操作的存储单元块。

BYTE_ENABLE:字节使能信号,用于对字节进行单独操作。

正常写模式(Normal-write Mode): 写入数据后,需要等待一个时钟周期才能读取出新数据。

通写模式(Write-through Mode): 写入数据的同时,数据也会立即出现在输出端。

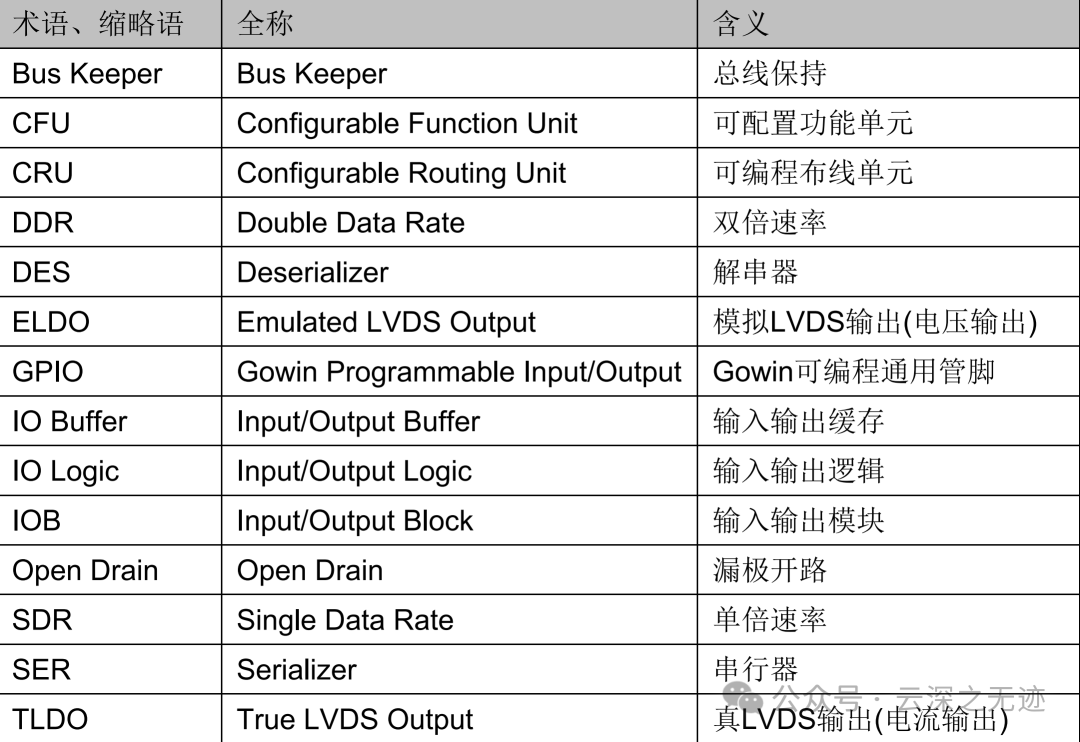

继续看,这是GPIO的一些术语

Bus Keeper: 总线保持器。用于在总线空闲时保持总线上的电平,防止噪声干扰,提高信号的完整性。

CFU:Configurable Function Unit 可配置功能单元。FPGA内部的基本逻辑单元,可以配置成不同的逻辑功能,如与门、或门等。

CRU:Configurable Routing Unit 可配置路由单元。用于连接FPGA内部的各个逻辑单元和I/O端口。

DDR:Double Data Rate 双倍数据速率。一种在时钟的上升沿和下降沿都传输数据的技术,可以提高数据传输速率。

SDR:Single Data Rate 单倍数据速率。只在时钟的一个沿传输数据。

DES:Deserializer 解串器。将串行数据转换为并行数据。

ELDO:Emulated LVDS Output 模拟LVDS输出(电压输出)。LVDS是一种低压差分信号传输标准。

GPIO:Gowin Programmable Input/Output Gowin可编程通用输入输出。FPGA的可编程输入输出引脚。

IO Buffer:输入输出缓冲器。用于缓冲输入输出信号,提高驱动能力和抗干扰能力。

IO Logic:输入输出逻辑。用于实现输入输出信号的各种逻辑功能。

IOB:Input/Output Block 输入输出模块。FPGA中负责输入输出的模块。

Open Drain:漏极开路。一种输出方式,输出端不接上拉电阻,需要外部电路提供上拉电阻。

TLDO:True LVDS Output 真LVDS输出(电流输出)。LVDS的一种实现方式,直接输出电流信号。

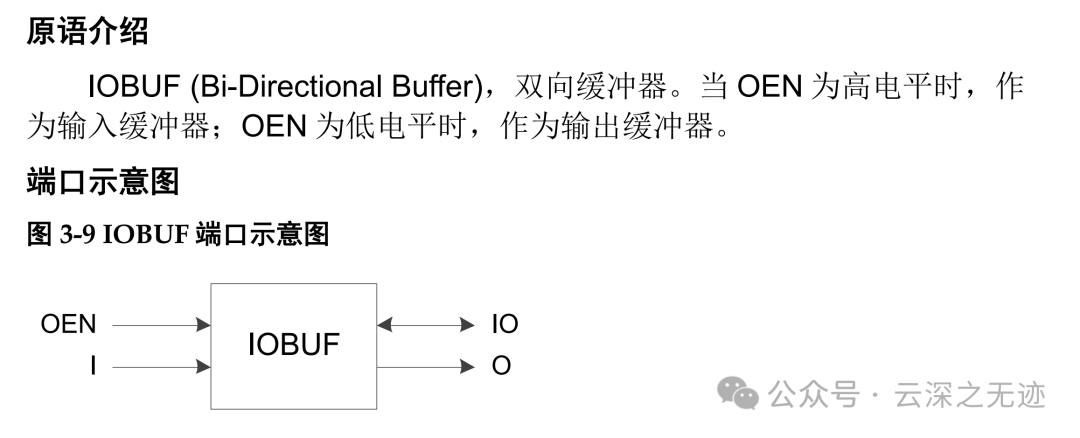

我们看一个缓冲器

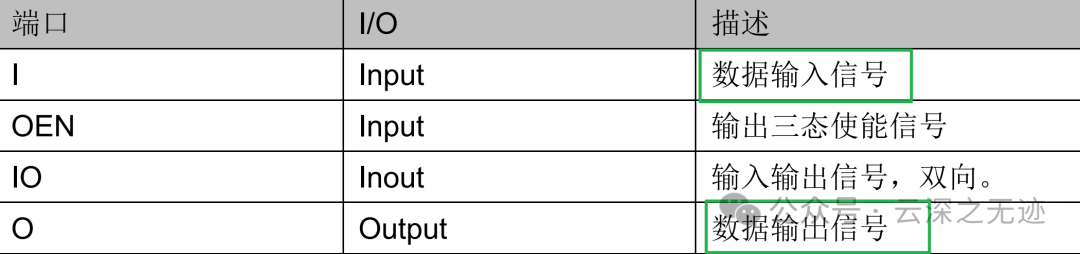

四个信号

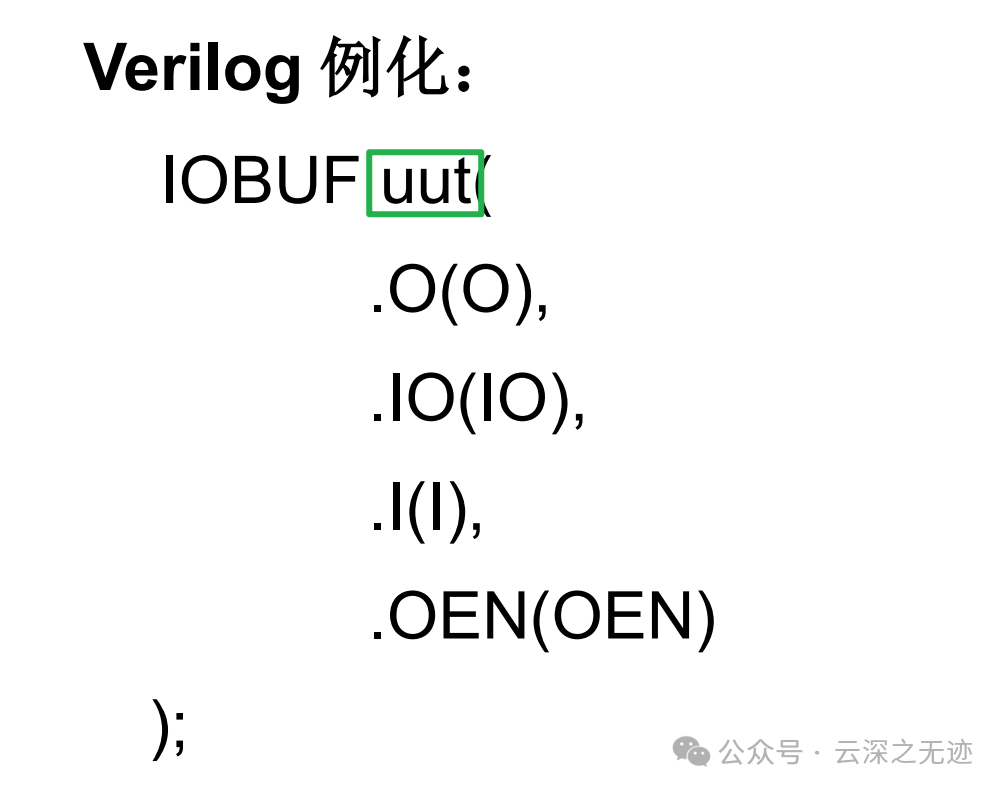

IOBUF uut;:声明一个名为uut的IOBUF实例。

.O(O), .IO(IO), .I(I), .OEN(OEN);:将实例的端口与外部信号连接。

O:输出端口

IO:双向端口,既可以输入也可以输出

I:输入端口

OEN:输出使能,控制输出的高阻态

Verilog使用.连接端口,VHDL使用=>连接端口。

GPIO里面有很多的原语,直接使用。

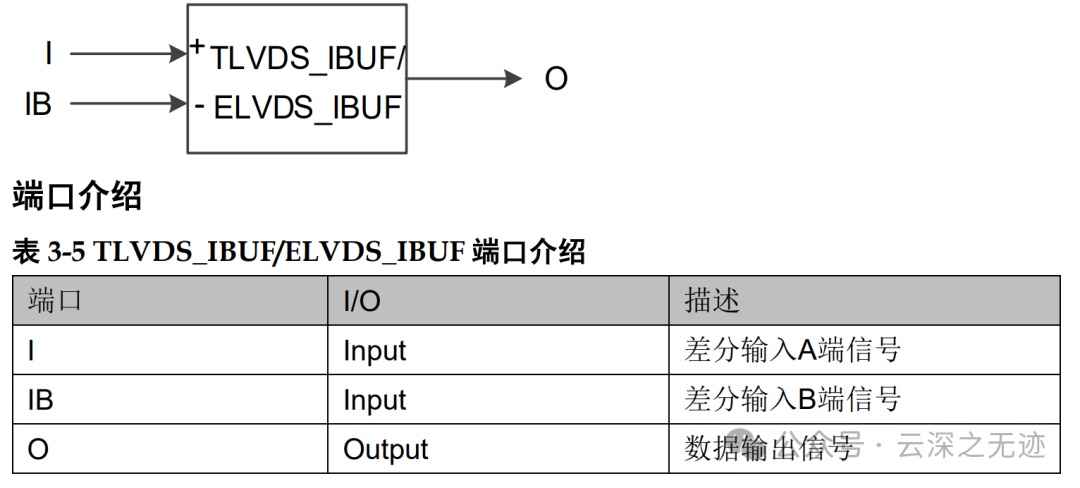

看这个,真差分缓冲器

I, IB: 这两个引脚是差分输入对,分别代表差分信号的正极和负极。

O: 输出端口,输出经过缓冲处理后的信号。

TLVDS_IBUF/ELVDS_IBUF: 表示这是一个LVDS或ELVDS输入缓冲器。LVDS和ELVDS都是低压差分信号传输标准,具有抗噪能力强、高速等特点。

LVDS

1变2

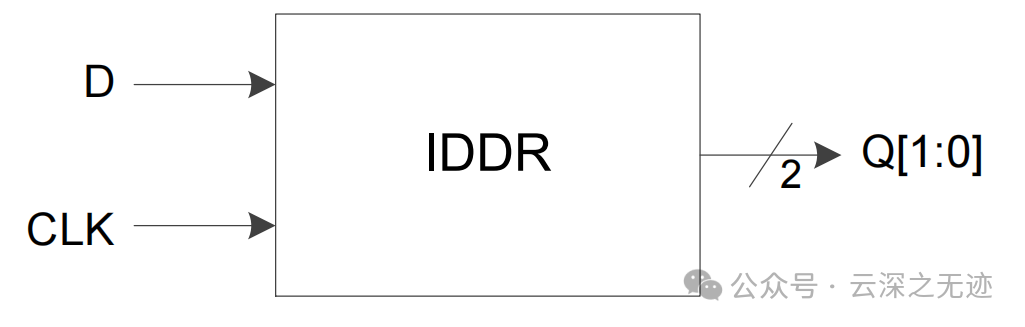

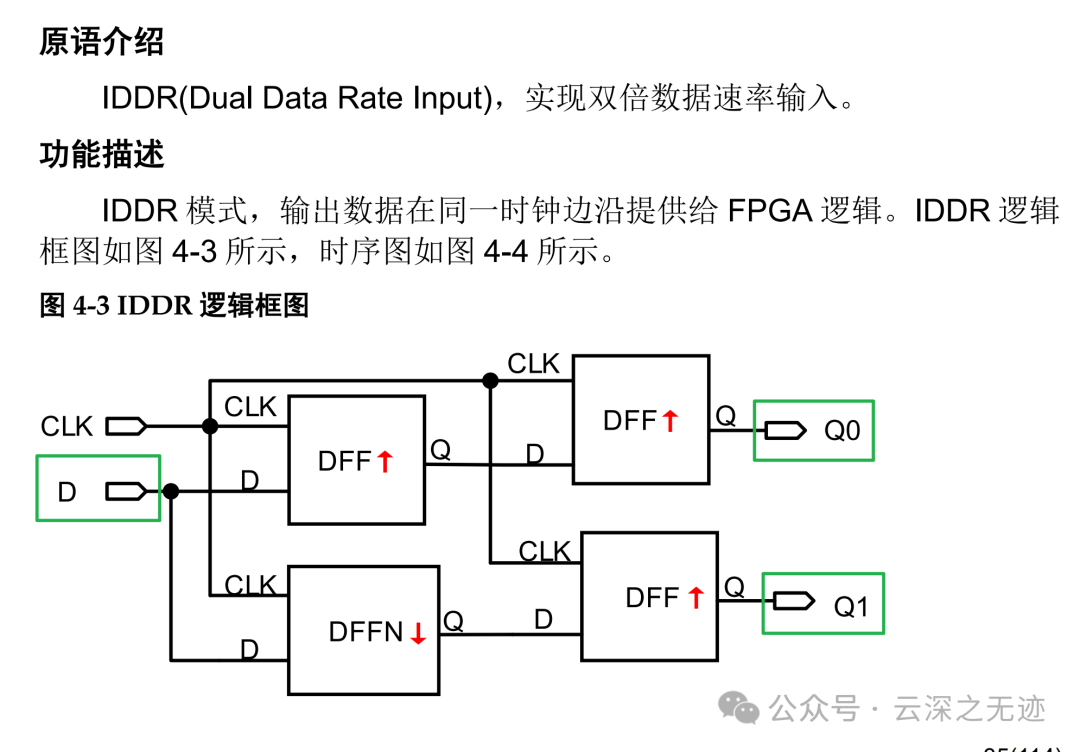

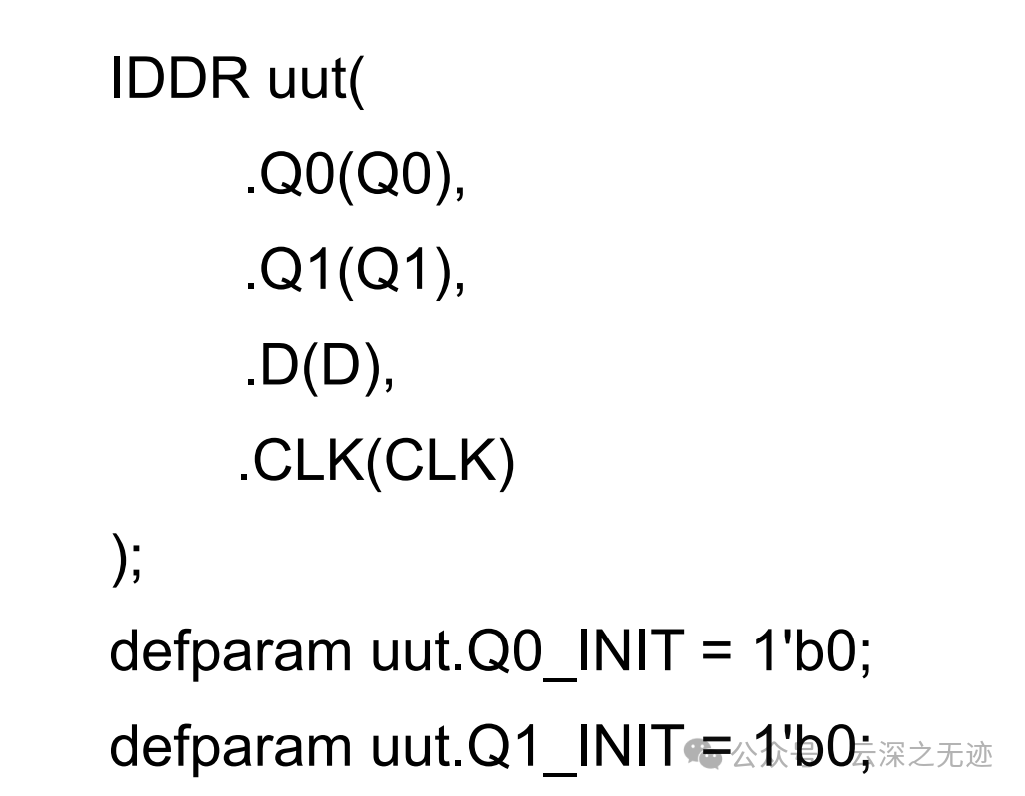

IDDR是一种特殊的输入接口,它能够在同一个时钟周期内,通过在时钟的上升沿和下降沿分别采样数据,实现双倍的数据传输速率。简单来说,就是用一个时钟周期完成了传统模式下需要两个时钟周期才能完成的数据传输。

双时钟采样: IDDR内部通常包含两个触发器,分别在时钟的上升沿和下降沿采样数据。

数据传输: 在一个时钟周期内,可以将两个数据位分别写入这两个触发器。

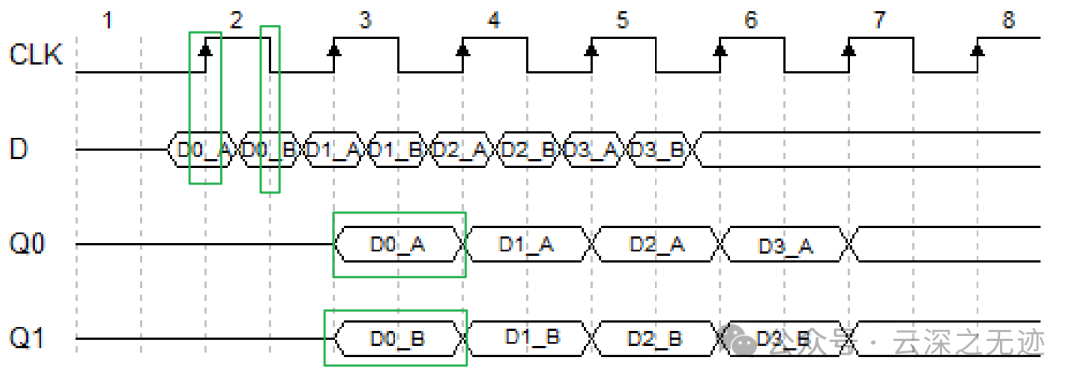

和上面单边采样的比较

可以看到D在CLK的上升和下降取样

时钟周期: 图中显示了8个时钟周期。

数据输入D: 在每个时钟周期内,D输入的数据是变化的,代表连续输入的数据。

输出Q0和Q1: 在每个时钟周期内,Q0和Q1分别在时钟的上升沿和下降沿采样D输入的数据。也就是说,在一个时钟周期内,IDDR可以输出两个数据。

defparam uut.Q0_INIT = 1'b0;

defparam uut.Q1_INIT = 1'b0;:设置Q0和Q1的初始值为0。

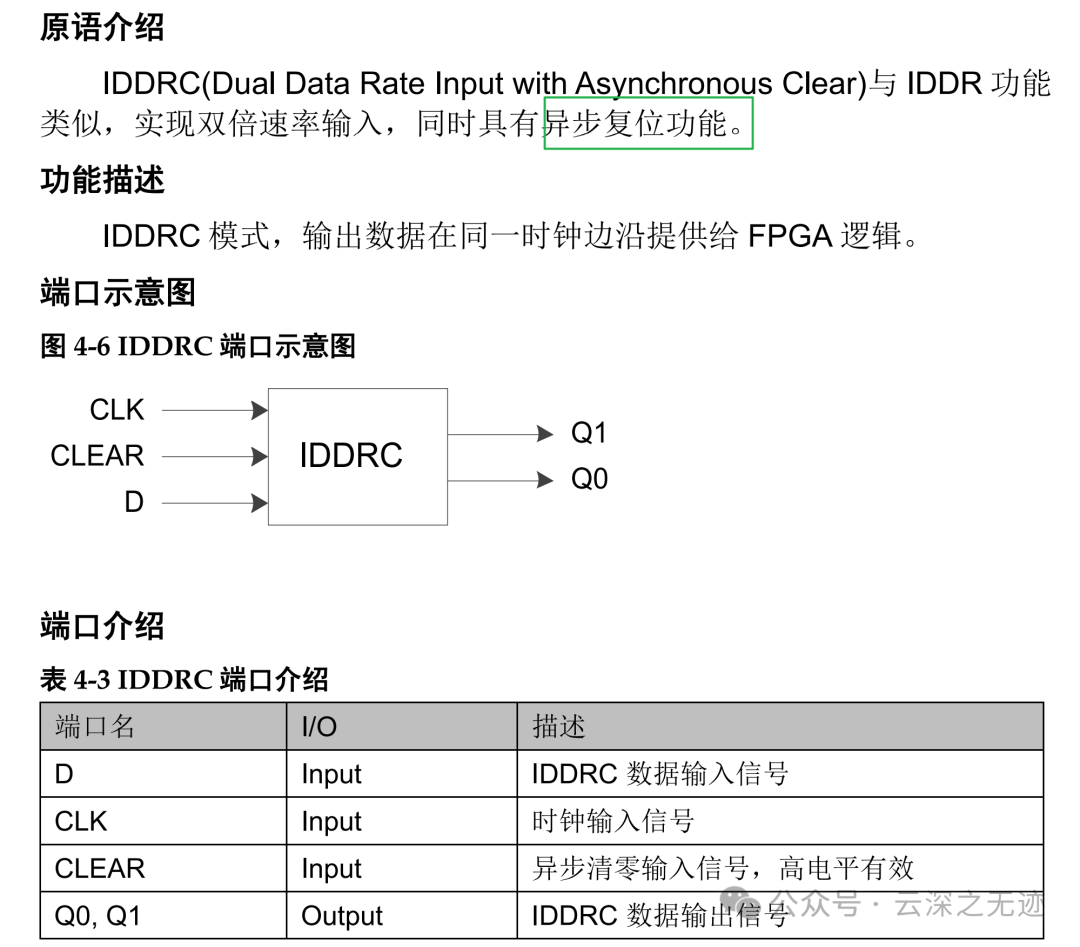

还有一个一样的,但是加了一个异步清0的

异步清零: 除了时钟信号,IDDRC还引入了异步清零信号。当异步清零信号有效时,不论时钟信号的状态如何,IDDRC的输出都会被清零。比如需要快速复位的场合。

和上面的比较

异步清零是指在不依赖系统时钟的情况下,通过一个独立的异步信号直接对寄存器或计数器等电路进行复位或清零的操作。与同步清零相比,异步清零不受系统时钟的限制,可以随时进行。

独立性: 异步清零信号与系统时钟是独立的,不受时钟边缘的影响。

灵活性: 可以随时对电路进行复位或清零,提高了系统的灵活性。

速度快: 异步清零的响应速度通常比同步清零更快。

FPGA真的是需要对计算机原理,数字电路,协议,编程的一些原则很熟悉才行。

但是FPGA也是很可爱,需要掌握系统的方方面面。