作者:Grace Sun,AMD工程师;来源:AMD开发者社区

在最新发布的Vivado Design Suite 2024.2中,引入的新特性之一是启用了仅适用于Versal器件的Advanced Flow布局布线。关于此特性,文档UG904以及AR#000036830 均有说明,本文基于此做些扩展汇总,以帮助读者对Advanced Flow有更全面的了解。

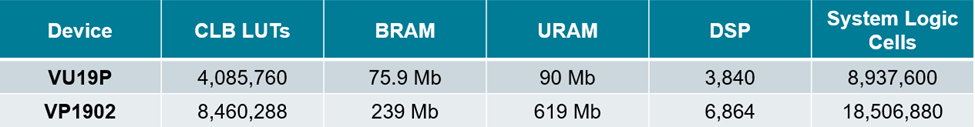

AMD Versal 自适应 SoC 将强大的可编程逻辑与加速引擎以及先进的内存和接口技术相结合,为各种应用提供定制且高效的异构加速。Versal 器件的逻辑密度显著提高,从而提高了性能和容量。下表比较了 UltraScale+ 系列的 VU19P 与 Versal Premium 系列的 VP1902,后者是一款大型器件。

从 UltraScale+ 过渡到 Versal 器件已导致关键资源显著增加:CLB LUT、BRAM、URAM、DSP 和逻辑单元的数量增加了一倍。这一增强功能能实现更复杂的设计。然而,随着逻辑密度的增加,编译时间也呈非线性增长。

随着设计变得越来越复杂,需要Vivado工具进行创新,以有效管理和应对以下方面的挑战:

编译时间

设计收敛

拥塞问题

Advanced Flow相较于Vivado传统的Standard Flow而言,旨在提高设计效率并缩短编译时间,适用于更大、更复杂、功能丰富的 AMD Versal自适应 SoC。

为了应对 Versal 架构编译时间更长的挑战,优化和加速布局布线过程至关重要。增强这一步骤将有助于管理 Versal 自适应 SoC 的复杂性。

从 2024.2 版本开始,Vivado Design Suite 为所有 Versal 器件引入了Advanced Flow。这种新流程具有新的布局布线算法,可提高设计性能、改善可布线性并更好地解决复杂的时钟布局要求。额外的架构改进增强了将大型复杂问题分解为可以并行解决的小问题的能力。

Advanced Flow 的引入显著加快了编译时间,改善了Versal设计的QoR,从而有助于提高整体生产力和加速设计迭代。

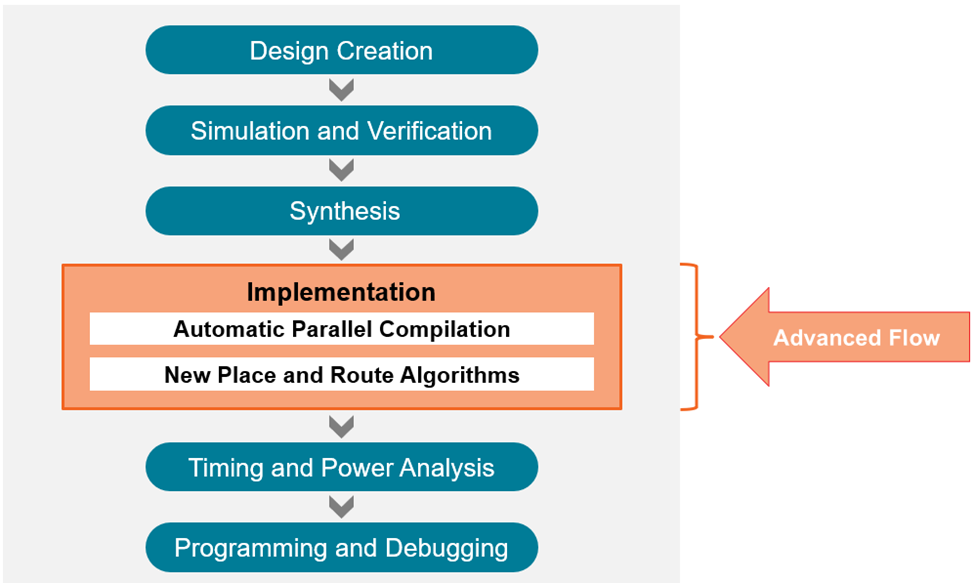

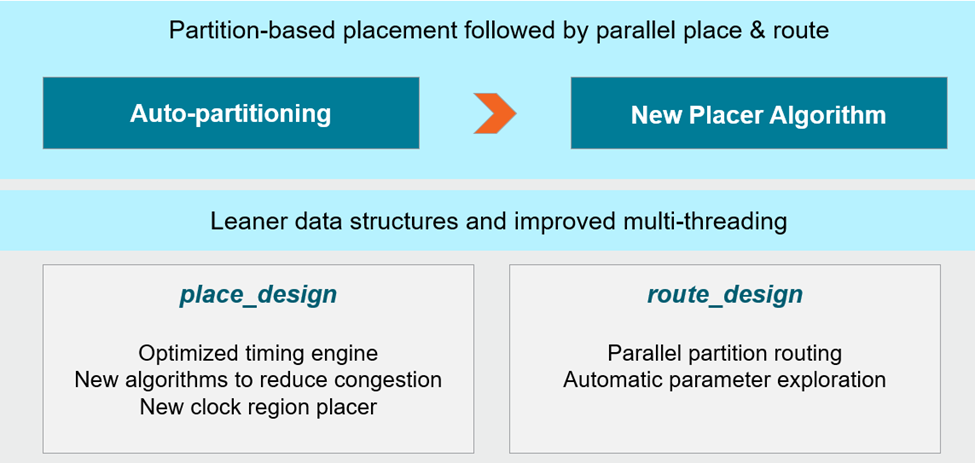

典型的设计流程从设计创建开始,然后是所有设计功能的模拟和验证,然后进入综合阶段。Advanced Flow的主要重点是Implementation阶段,其中包括自动并行编译和新的布局和布线算法,如下图所示:

Advanced Flow引入了改进的分区和布局规划方法,可优化并行编译。新算法有助于放置复杂的时钟网络、减少拥塞并提高整体性能。这种架构和算法的组合大大加快了编译过程。placement后,分区信息将传递到router,以便可以并行布线分区。

后续流程(例如时序和功率分析、编程和调试)与 Vivado 的先前版本相同。

Advanced Flow 之所以成为 Versal 器件更强大的解决方案,主要得益于其自动分区以实现并行处理的功能。

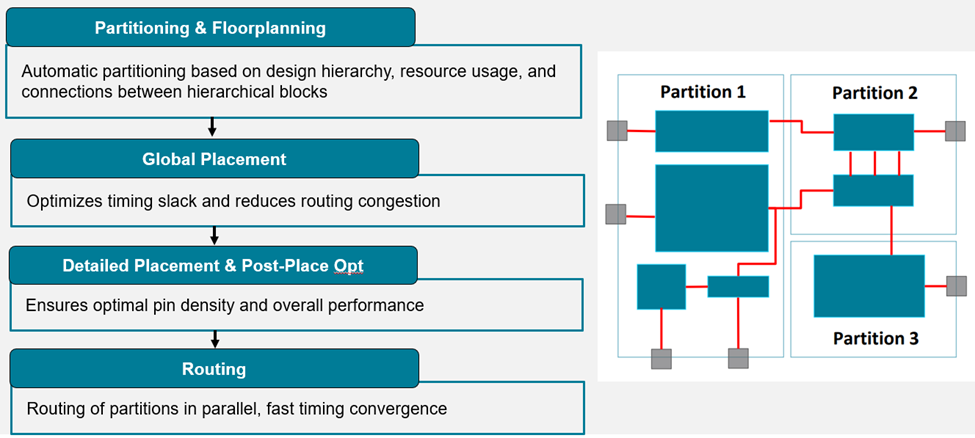

自动分区将大型复杂设计划分为可以并行解决的较小布局和布线问题,以更有效地处理分区的并行编译。对于 SSI 设备,这涉及将逻辑划分为SLR,对于单片设备,将逻辑划分为设备内的不同区域。

分区器会分析设计层次结构、资源使用情况以及模块之间的连接,自动完成设计分区。分区后,设计将以并行方式进行布局,从全局布局阶段开始,通过粗略级别的时序和拥塞优化进行整个设备的设计布局。下一阶段的详细布局和布局后优化器将优化全局布局,以确保最佳引脚密度和最佳整体性能。

然后,分区信息将传递到布线器,布线器将使用相同的分区进行并行布线,从而实现非常快速的时序收敛。

与之前的版本一样,物理优化(Phys Opt Design 步骤)可在布局后的任何时间使用,以改善时序。

在 Vivado 内部,Advanced Flow 使用更精简的数据结构来存储和检索物理设计信息,这不仅提高了布局和布线速度,而且还提高了使用checkpoint读写大型设计的能力,减小了内存占用。多线程的改进进一步提高了布局和布线效率。

新的时序引擎经过优化,可与布局器及其数据结构配合使用,有助于快速评估布局更改的时序影响。此外,布局器还增加了减少每个方向的布线拥塞的功能,从而显著提高了整体设计的可布线性。新的时钟区域布局器的容量大大增加,从而可以更好地处理具有大量全局时钟的复杂设计。

布线器可以从布局器获取分区信息来并行布线这些分区,也可以提前预测要使用多少个分区。初始布线后,会自动探索布线算法的不同参数和阈值组合。布线器会选择最佳组合,引导算法快速收敛到时序要求。

总体而言,这种新的工具架构具有将大型复杂设计自动分解为独立分区的功能,无需用户干预即可缩短编译时间。

点击“阅读原文”或扫码阅读全文