公众号 | 高速先生

作者 | 黄刚

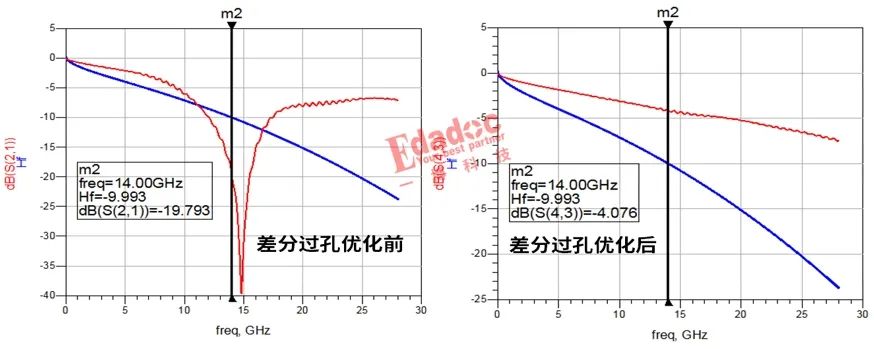

又是崭新的一年哈,高速先生在总结去年一年的粉丝互动问题时,惊人的发现排在前列的问题就包括了差分过孔的优化方法能不能大概给出来。当然,大家都知道,像传输线的阻抗板厂可以来保证,但是它们没法保证过孔的阻抗。随着速率越来越高,过孔就变成了比传输线损耗更危险的东西了。在大家以前的观念中,一个过孔哪怕是随便设计一下,损耗顶多去到1-2db就已经顶天了吧。在一条具体项目的芯片到芯片高速25Gbps链路中,只有收发两个差分过孔和中间的传输线,你能想象过孔优化好和没优化好的损耗差距有多大吗?仿真结果绝对颠覆你们想象。

对,差分过孔不做优化的话,整体链路的损耗去到接近20dB,如果认真去优化之后,损耗只有4个db,也就是两个过孔优化前后差了16个db!对比蓝色的损耗协议来说,就是pass和fail的巨大区别。走线那么长才几个db的损耗,没想到一个小小的过孔能比走线损耗都大哦!

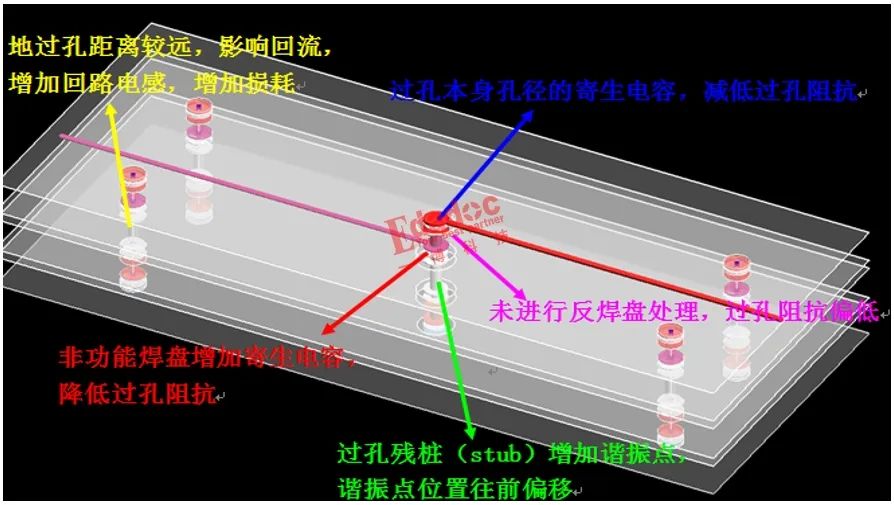

所以嘛,高速先生粉丝才每年都问我们能不能给一些通用的过孔优化方式。当然这个要求本身情有可原,一点也不过分。毕竟过孔的影响就摆在那嘛。通过下面这个单端过孔的影响示意图也能看到过孔的很多参数都会影响过孔性能。更何况的参数更多的差分过孔了。

但是高速先生也是有苦衷的啊,平时严谨的方式都推荐大家去做个仿真,真的不是故意体现我们的存在感哈!而是每个项目的过孔参数都不同,实在是没法一概而论。下面高速先生用回答一个和我们合作多年的重要客户同样问题的例子来和大家解释解释下哈。

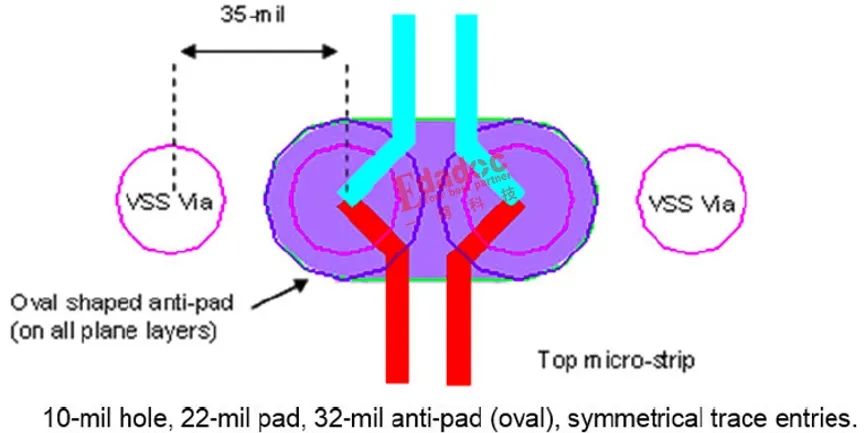

客户拿出了他们找到的不知道哪一家的设计指导书,然后对高速先生说,你们能不能也出一个像他们一样的过孔设计给行业用呢?高速先生拿到他们的关于过孔的指导图看看,的确是有不错的约束。它们对差分过孔做了很多的约束,例如信号孔到地过孔的间距为35mil,过孔的孔径为10mil,焊盘大小为22mil,甚至还规定了反焊盘为32mil的椭圆形反焊盘。

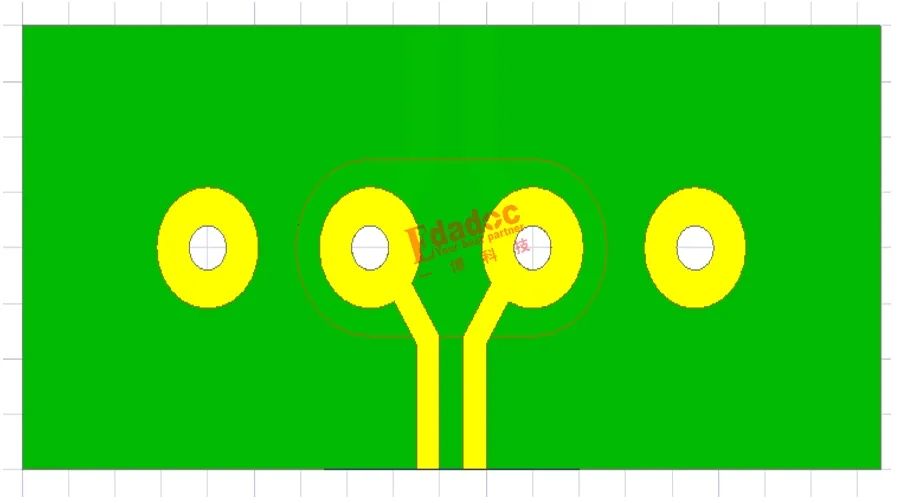

这个客户就拿着这个他们认为可以直接照抄的过孔设计指导来找我们,问高速先生也能不能在行业内去做这样的普及。上面这个过孔设计指导乍眼一看好像所有参数的约束到了,但是真的是这样吗?高速先生就用这个模型来进行建模仿真看看。按照它上面的约束参数,建模就是这个样子了。

真的是什么参数都覆盖了吗?那你就太小看这对差分过孔了。高速先生在上面已经约束很多基础上再给大家挑几个没约束的参数来对比仿真下哈。

1.板材的介电常数不同

如果这个设计用到不同级别的板材上时,阻抗的差异有多大呢?假设用到了介电常数为4和3.5的两种case上时,通过仿真会发现阻抗的差异有5个欧姆之多,如下所示:

2.出线层不同

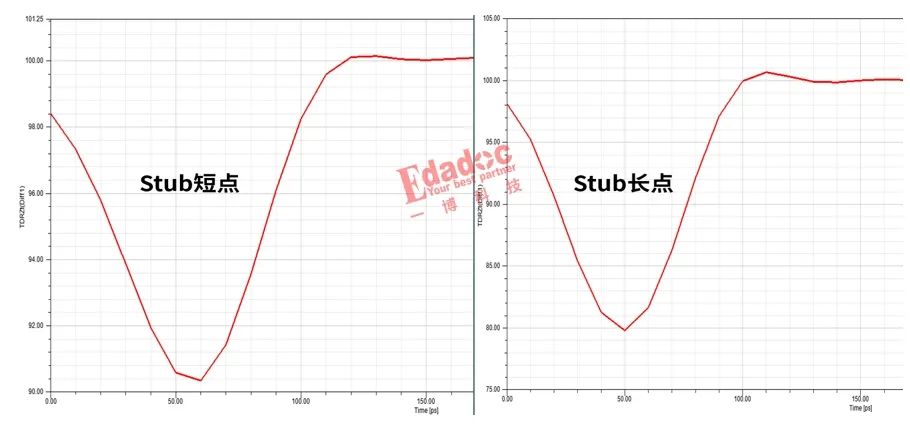

如果同样的过孔在内层的出线层不一样时,例如一个是靠很下层出线,stub比较短,另外一个是没那么下层出线,stub稍长一点,如下所示:

那么从对比的仿真结果看,阻抗差异会达到10个欧姆之多。哪怕长点的stub有背钻,我们之前的文章也有分享过,不同长度的层出线,过孔阻抗也会有不小的差异哈。

3.差分过孔间距不同

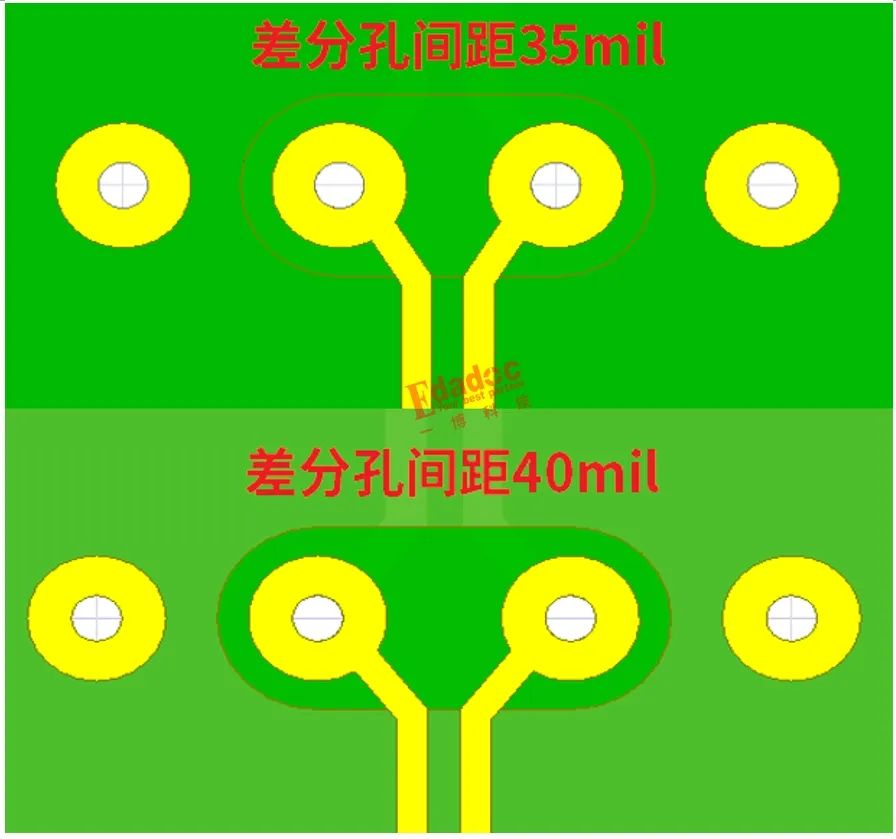

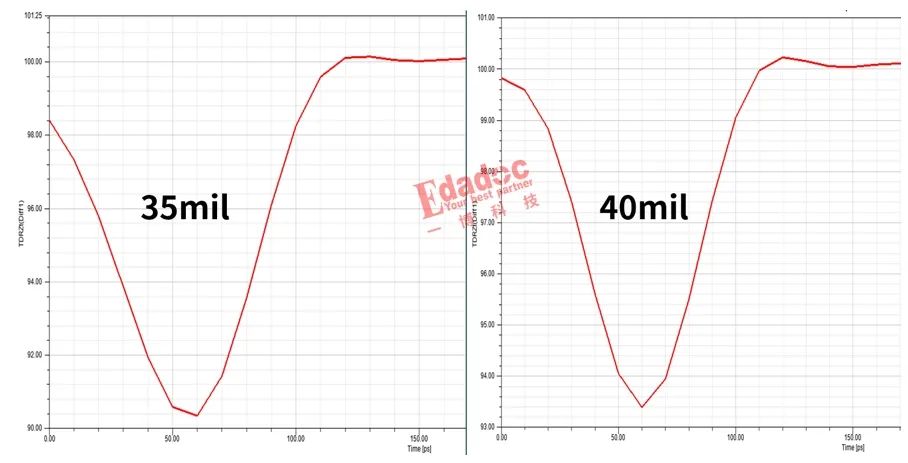

仔细看给过来的过孔指导,其实只约束了信号孔到地过孔的距离,但是没对信号孔之间的距离做约束,那我们分别建一个信号孔距离35mil和40mil,其他参数均满足指导图的case做对比,如下所示:

真没想到吧,居然这样也会有差异哦,从仿真结果看,也有超过3个欧姆的差异。

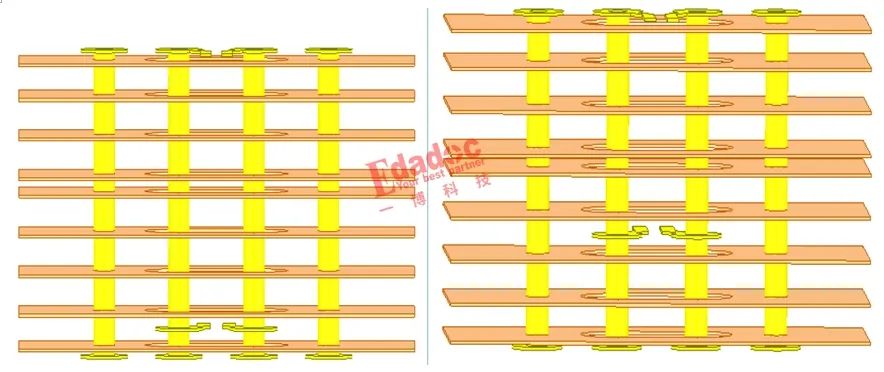

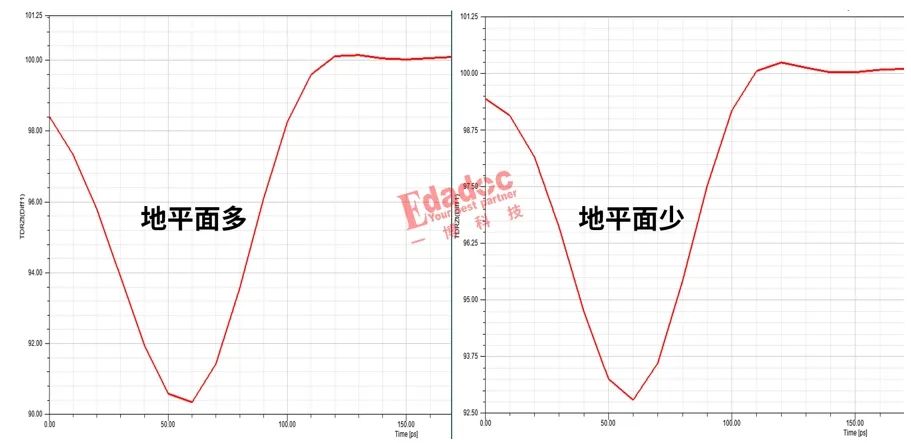

4.地平面多和少的区别

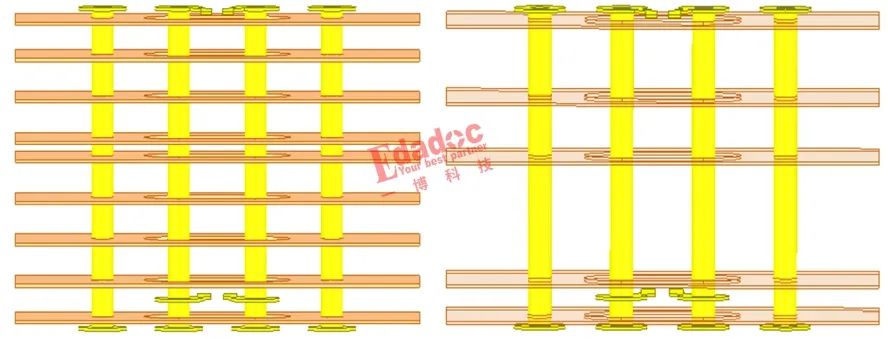

没想到还有差异点吧,如果过孔长度一样的情况下,中间层的地平面多一点和少一点也会有差异,如下所示:

从仿真结果看,差异也有接近3个欧姆。

还有其他点吗?高速先生其实觉得还有,时间关系就不再一一去抠了。这下客户也服气了,哪怕已经约束了很多参数了,其实还有另外更加隐蔽的参数没在里面,然后这个没考虑到的参数在不同的设计项目中就有可能不同,那么导致过孔阻抗的差异从3到10欧姆不等,甚至更多。这个时候再回头去看看所谓的过孔约束指导,是不是感觉意义就不那么大了吧。

当然粉丝们也不用灰心,需要知道速率越高过孔参数不同的影响就越大。如果你们的产品速率没有很高的时候,例如10GHz以前,按照我司的大部分有高速经验的设计工程师的设计方法都问题不大,这个时候其实有不少裕量足以支撑你不用去仿真的。当然速率上去了,如果大家深切的体会到了过孔的影响程度之后,我相信都不用高速先生推荐了,你们都会主动向我们提仿真需求了哈。

Q

本期提问

那大家又是怎么对高速过孔进行设计的呢,有什么自己的方法和秘诀都可以分享下哈。

声明:未经高速先生授权许可,任何机构、媒体、个人不得转载、修改、摘编或以其他方式复制、传播高速先生平台的原创作品。

— end —

如果不想错过“高速先生”的精彩内容,请记得点击上方蓝字“高速先生”,右上角“...”点选“设为星标”。可第一时间看到高速先生的推文,感谢大家的关注和支持!