今天给大侠带来基于FPGA的任意分频器设计,附源码,获取源码,请在“FPGA技术江湖”公众号内回复“任意分频器设计源码”,可获取源码文件。话不多说,上货。

在FPGA设计中,分频器一直都担任着很重要的角色,我相信很多人都已经想到了利用计算器来计算想要使用的时钟频率,但问题是仅仅利用计数器来分频,只可以实现偶数分频,而如果我需要三分频,五分频,七分频等等奇数类分频,那究竟怎么办呢?在这里,让我介绍一个可以实现任意整数分频的方法,这个办法也是同样利用了计数器来计算,跟偶数分频不一样的地方是任意整数分频利用了两个计数器来实现。

本次设计主要是设计一个可调的分频器,设置其参数,可以调节其输出的占空比,占空比的意思就是高电平所占周期的多少。我们通知计算高电平的时间和低电平的时间来实现,其实就是我们用两个计数器来控制的。

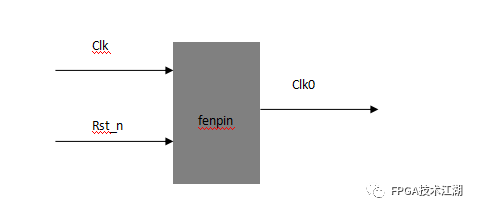

设计框架图:

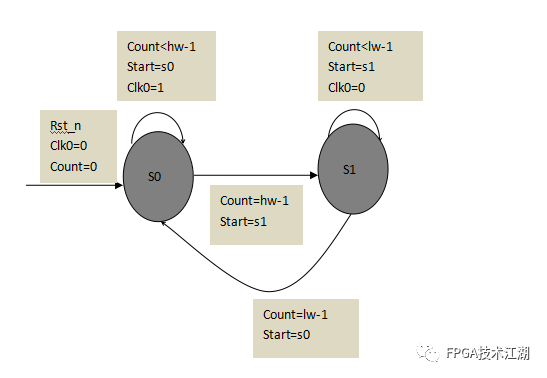

状态转移图:

通过对两个计数器的计数,一个计算到了跳转下一个状态,等下一计数器计数到了又调回第一个状态,从而完成任意分频器的设计。

module fenpinqi(clk,rst_n,clk0);input clk;input rst_n;output reg clk0;parameter HW = 7 ;parameter LW = 3 ;localparam s0 = 1'b0;localparam s1 = 1'b1;reg state;reg [2:0] count;always @(posedge clk or negedge rst_n)if(!rst_n)beginstate <= 1'b0;count <= 3'b0;clk0 <= 1'b0;endelsebegincase (state)s0:begin== HW)state <= s1;*/+ 1 > 1)< HW -1 )beginclk0 <= 1'b1;count <= count + 1'b1;endelsebegincount <= 1'b0;state <= 1;endends1:begin+ 1 > 1)< LW -1)beginclk0 <= 1'b0;count <= count + 1'b1;endelsebegincount <= 1'b0;state <= 0;endenddefault:state <= 0;endcaseendendmodule

1ns/1psmodule fenpinqi_tb();reg clk;reg rst_n;wire clk0;parameter HW = 7;parameter LW = 3;initial beginclk = 1'b1;rst_n = 1'b0;#200.1 rst_n = 1'b1;#2000 $stop;endalways #10 clk = ~clk;fenpinqi #(.HW(HW),.LW(LW))fenpinqi_dut(.clk(clk),.rst_n(rst_n),.clk0(clk0));endmodule

仿真图:

图中我们通过数上升沿的个数可以看到输出clk0的输出为高7,低3,符合我们的设计。

END

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+学校/公司+专业/岗位进群

FPGA技术江湖QQ交流群

备注姓名+学校/公司+专业/岗位进群