上文中说完了电源系统,下面就把眼光转到这个测量系统。

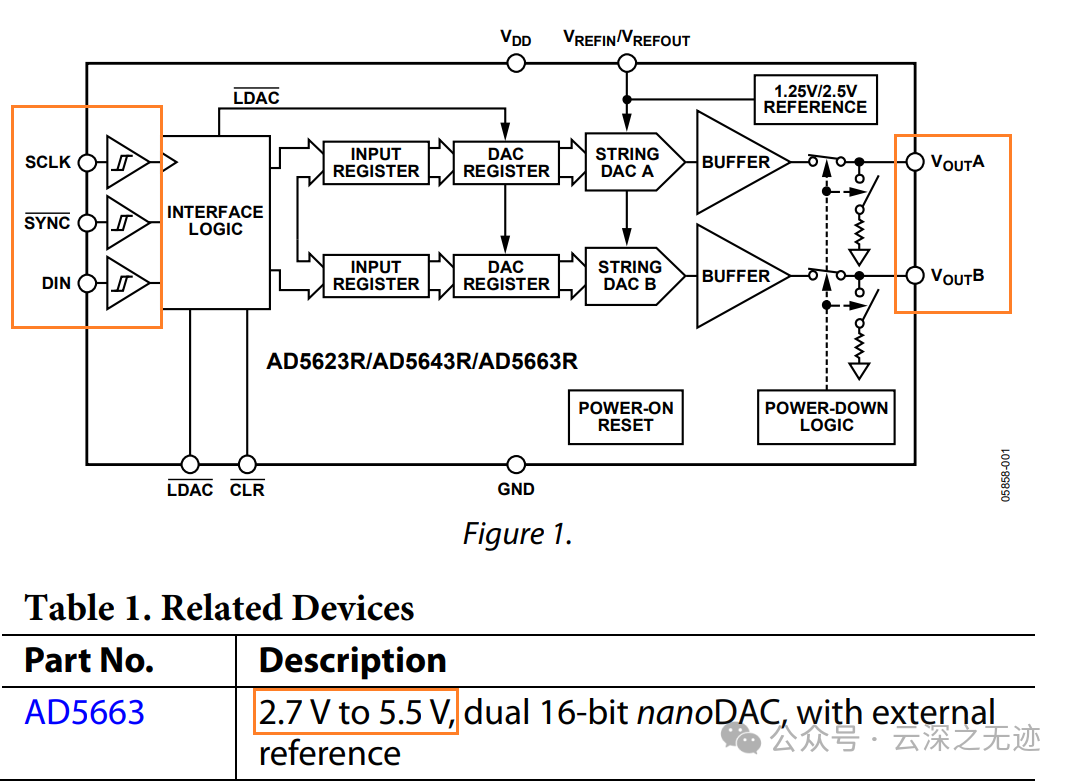

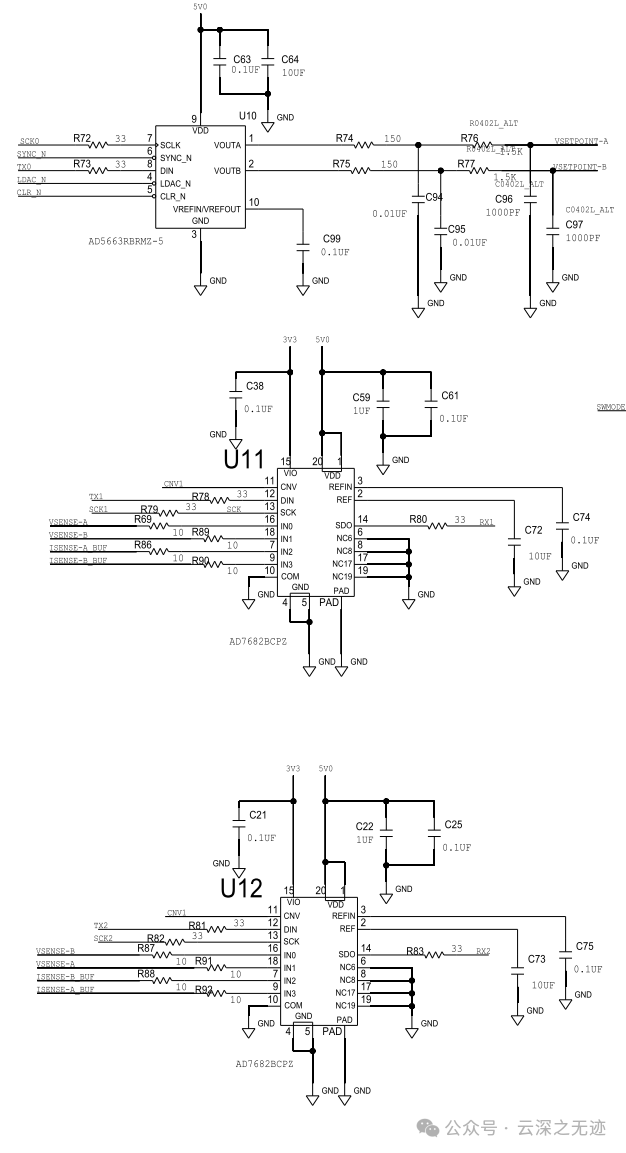

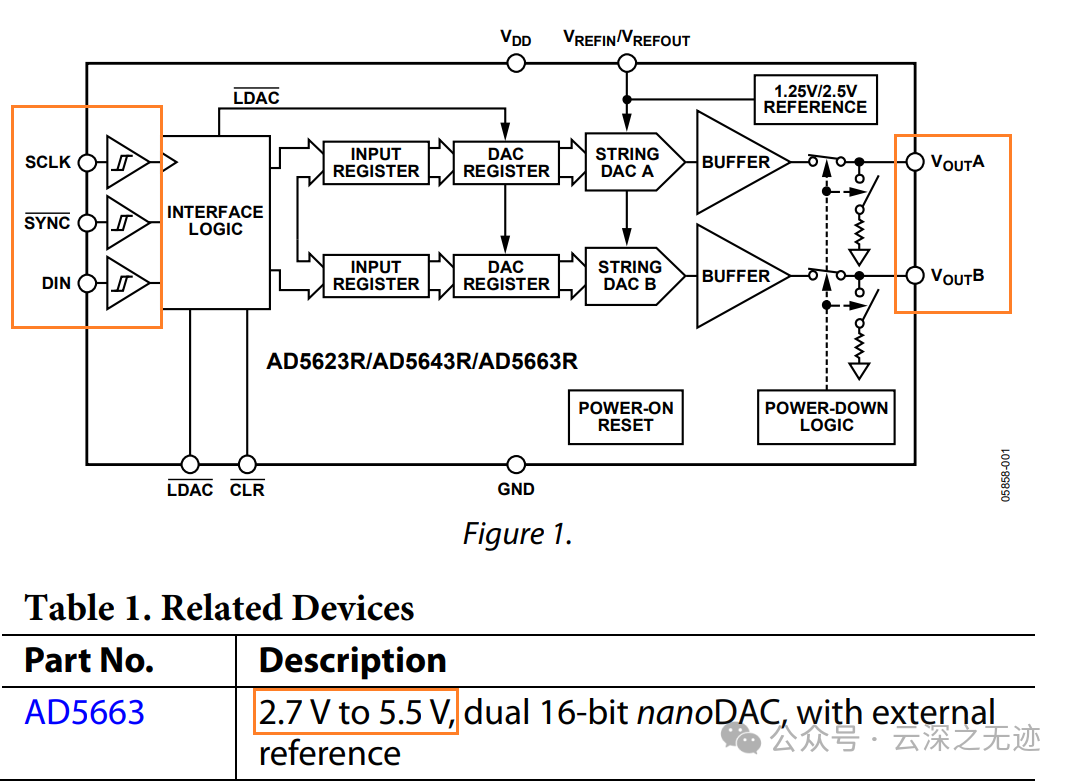

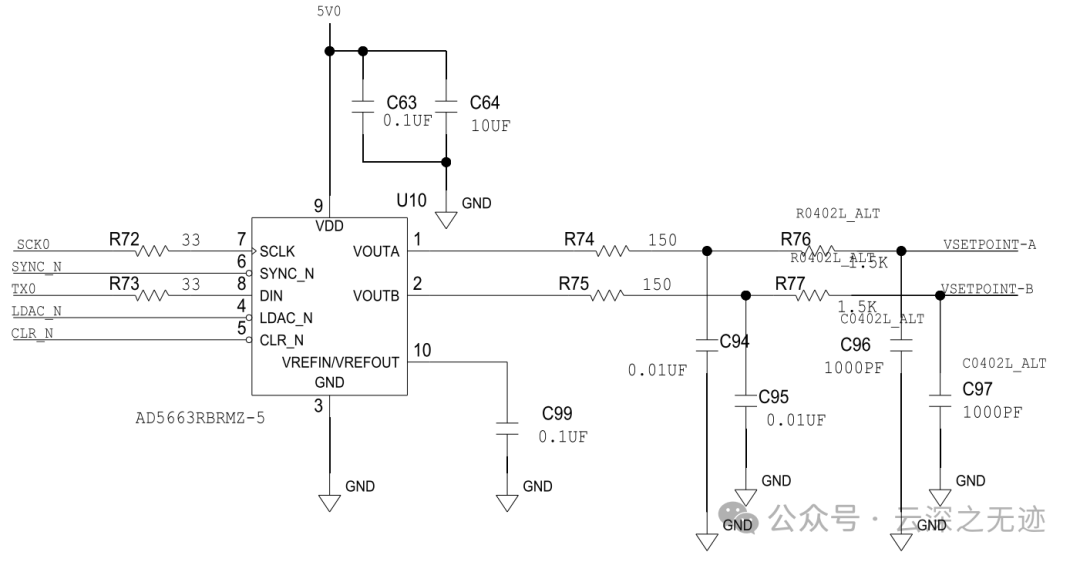

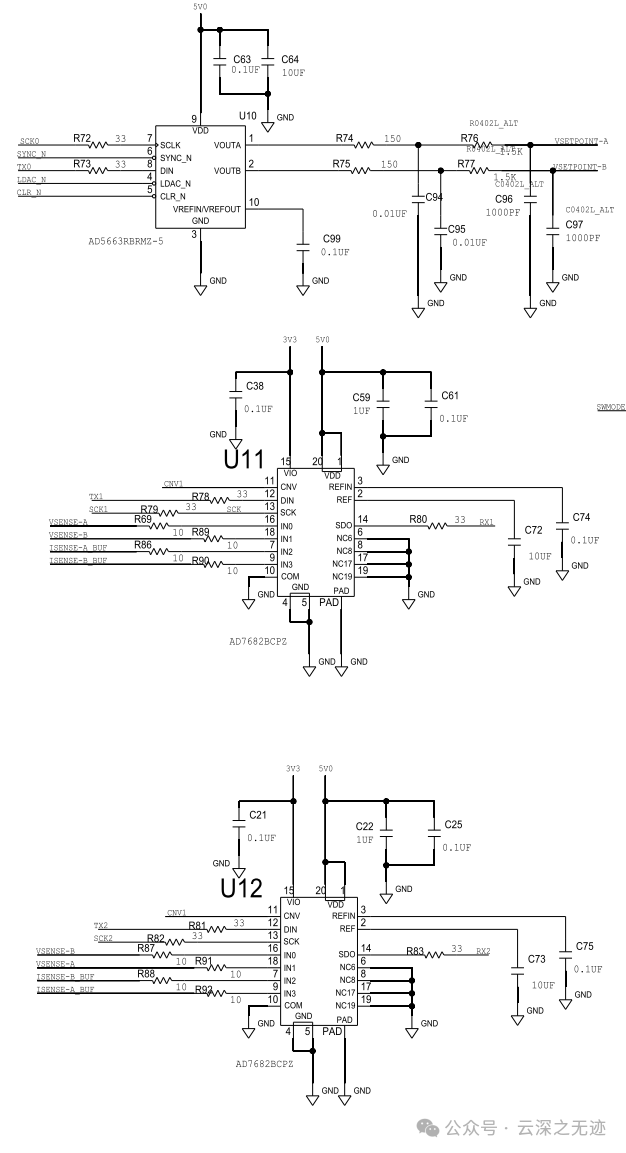

为了从数字连接的设备中获得模拟输出,需要将波形的二进制表示转换为模拟近似值。这一过程通过使用 AD5663R 双通道数模转换器(DAC)实现,具有 16位转换、快速稳定时间(高带宽) 和简单的数字接口。

就是这个啦

就是这个了

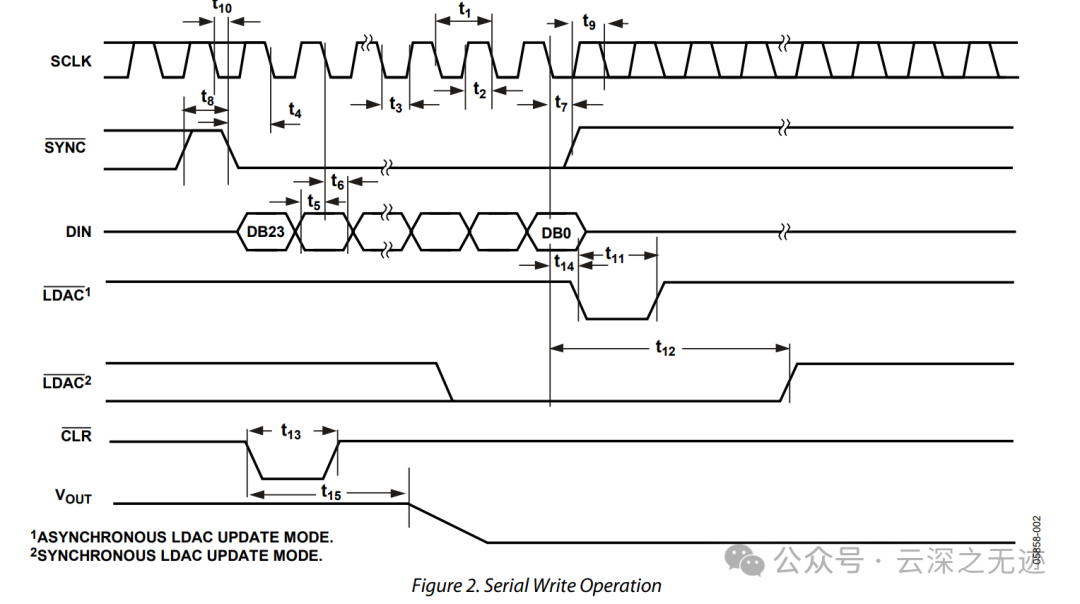

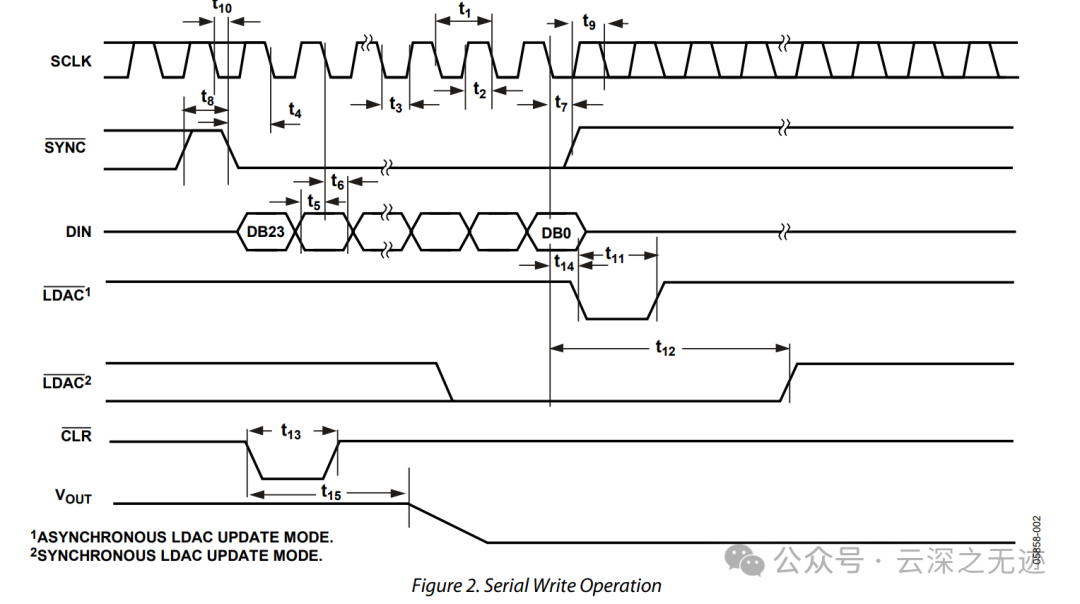

这个时序怪怪的

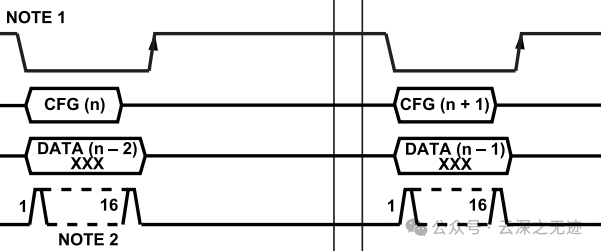

24位数据字被写入数字线,其中包含16位数据和8位配置位,数据从高位开始,依次写入到最后一位。

确实

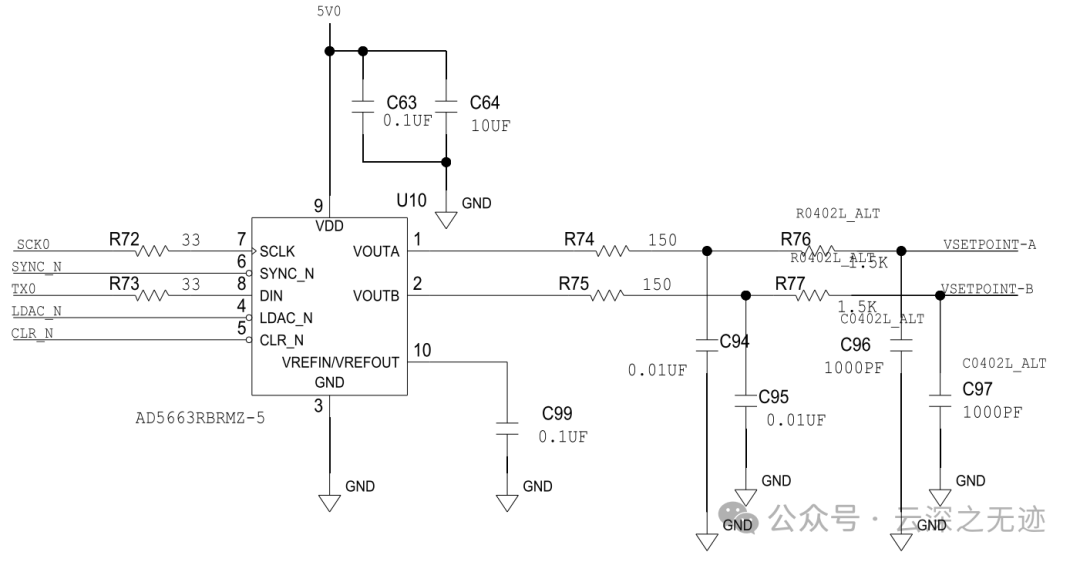

使用一个单独的时钟线来指定数据有效的时刻。通过同步线触发,交替传输随后的24位数据字。通过锁存线触发将存储在设备内存中的数据字转换为模拟电压输出。每个样本都写入两个24位的数据字,在它们之间触发同步线,之后通过切换锁存线同步开始模拟值的变化。为了减少模拟值变化中的高频成分,在设备的模拟输出端放置了两个一阶低通滤波器,每十倍频率衰减 6dB,有效地将高次谐波的幅度降低到可忽略的程度。

确实有这个滤波器

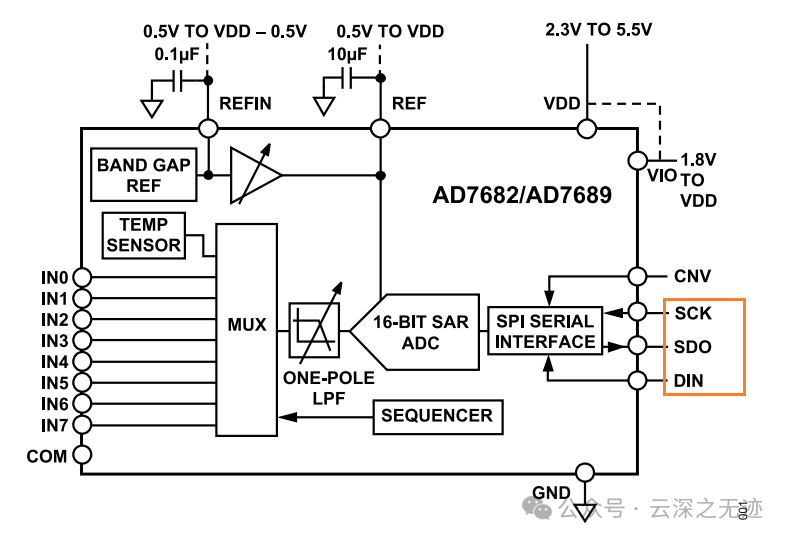

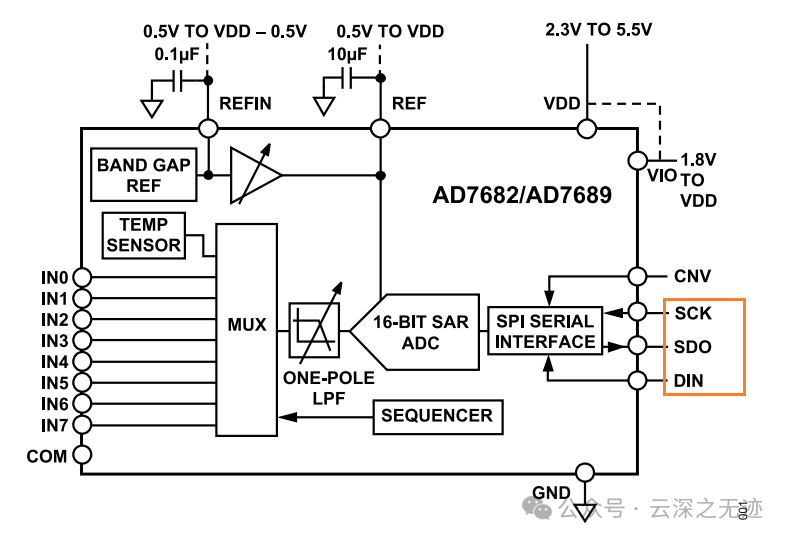

模数转换(Analog-Digital Conversion)-ADC为了对两个模拟通道(分别测量电压和电流信号)进行采样,使用了两个四通道 AD7682 十六位模数转换器(ADC)。每个转换器接收两个通道的模拟信号,实现电压和电流在任意组合下的同步转换。

哟~

眼熟

精密小体积ADC-AD7682 16位4通道 哥们呢写过!

太香了这个小ADC

其实怎么说呢?还真不如有专门的输出引脚的ADC好,这个SPI的时序不是很简单。

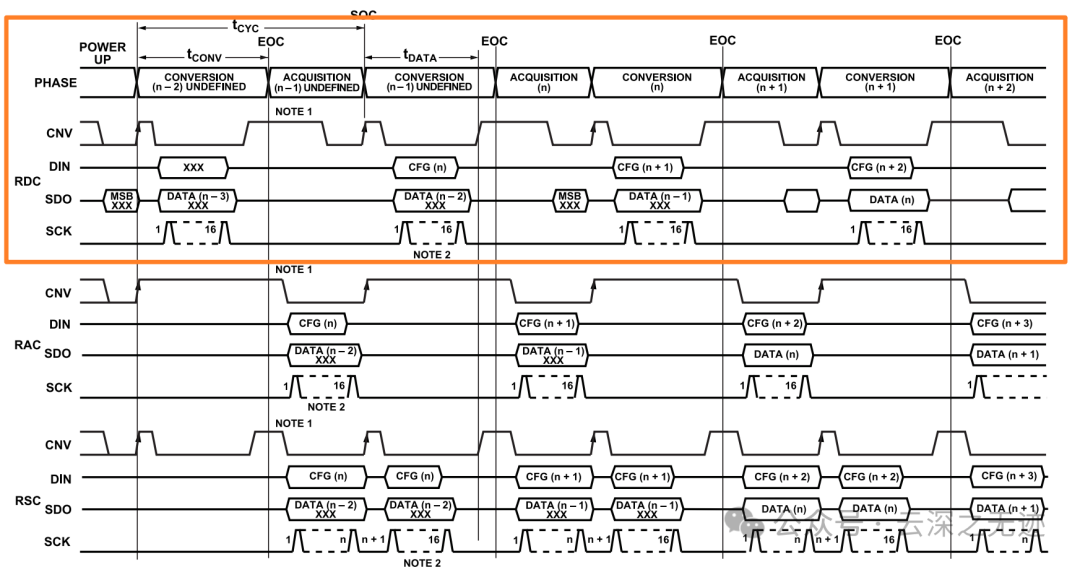

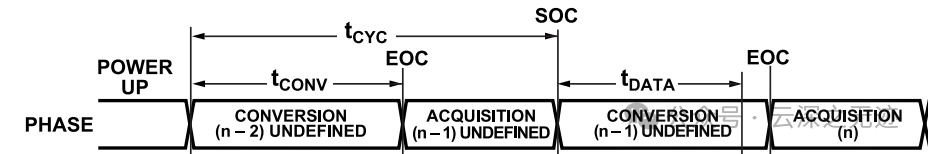

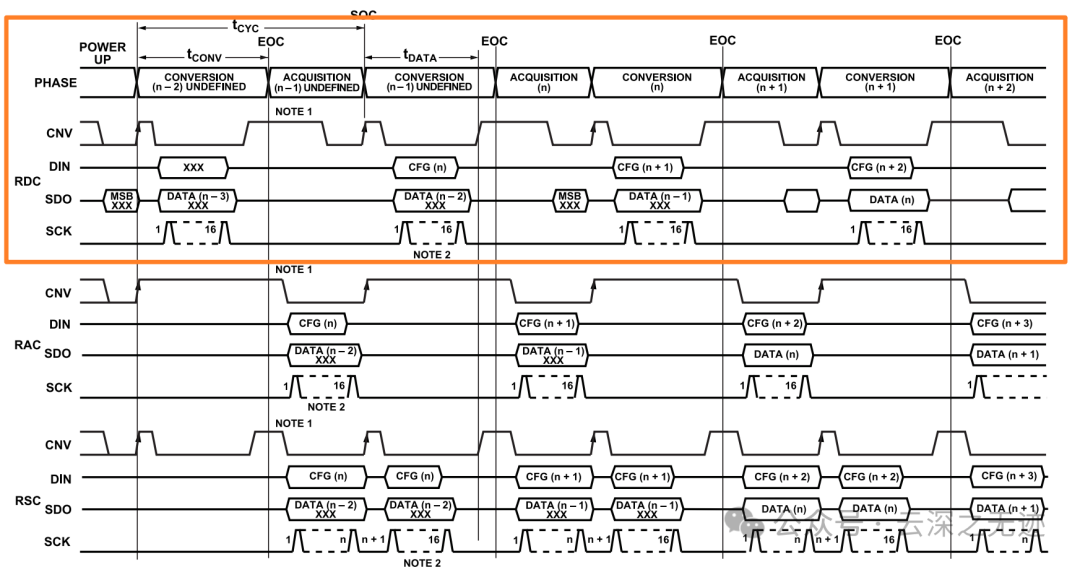

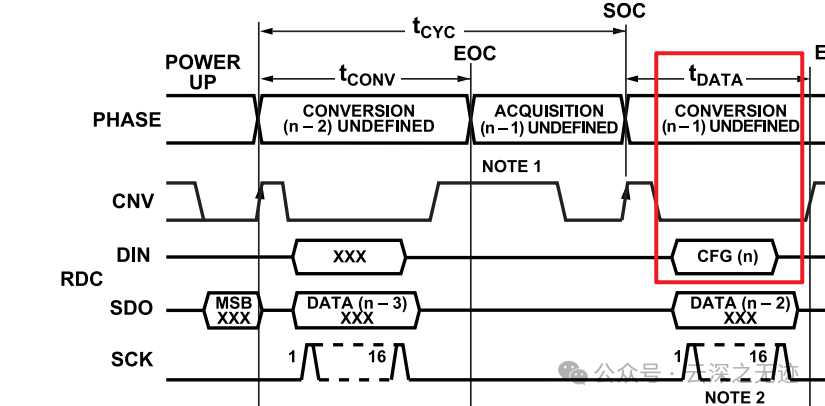

有三个状态

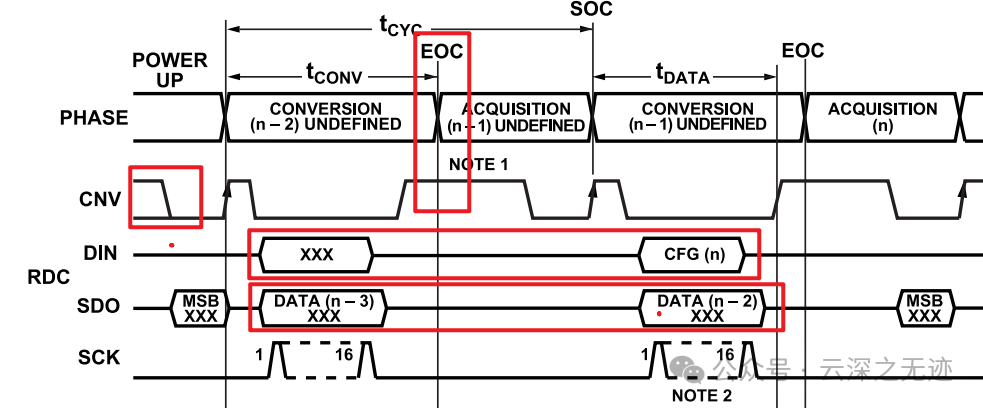

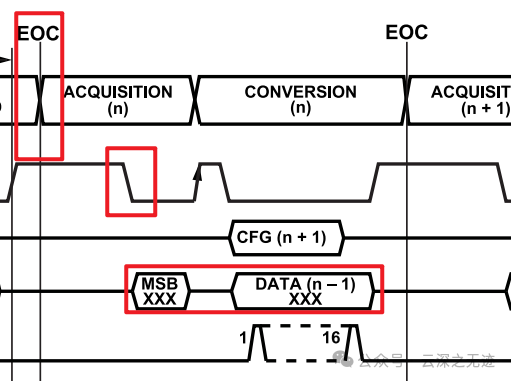

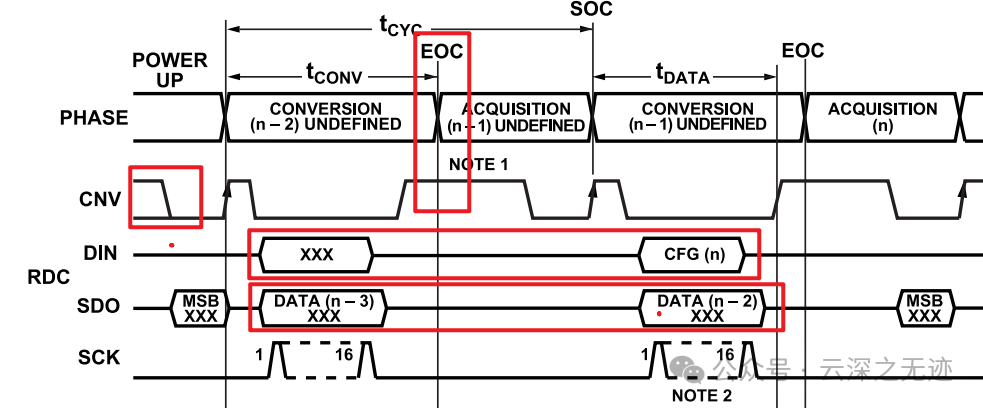

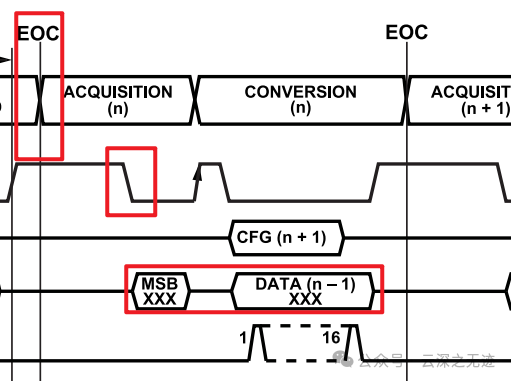

我们再分析一下这个时序。

RDC(Read During Conversion):在转换期间读取数据。

RAC(Read After Conversion):在转换完成后读取数据。

RSC(Read/Write Spanning Conversion):跨越转换周期进行读取/写入。

读取的状态有三种。

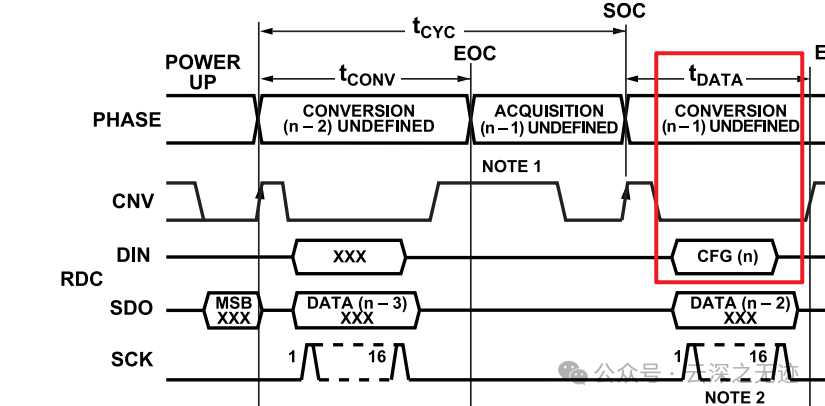

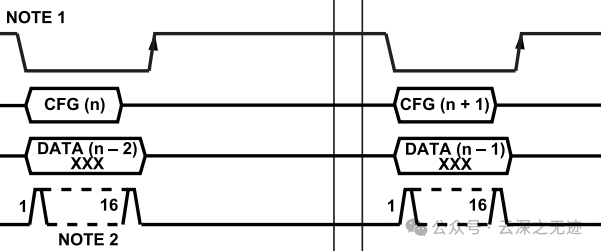

SDO输出,MSB先输出

CNV:转换启动信号,当其由低拉高时,启动一个新的采样/转换周期。

EOC:转换结束信号(End Of Conversion),表示当前采样/转换已完成。

SDO:串行数据输出,用于输出 ADC 转换结果。

DIN:串行数据输入,用于写入配置寄存器(CFG)。

SCK:串行时钟信号,用于数据的同步传输。

在上电后的最初几次读写周期(图中第一个“Phase n”),ADC 的转换结果是不确定的(undefined)。需要两次虚拟转换(dummy conversions),以确保 CFG(配置寄存器)被正确加载,且 ADC 进入正常工作状态。

就是一开始的周期是读入配置

这里就CFG配置进去

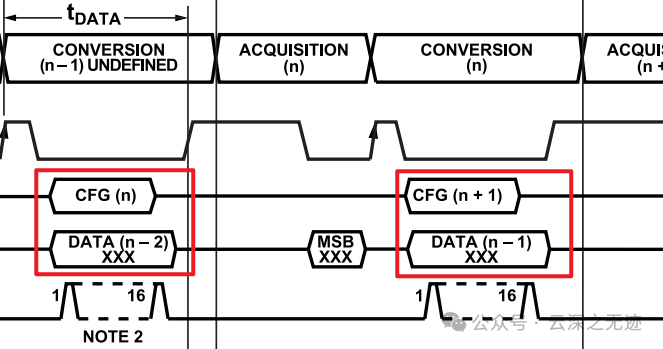

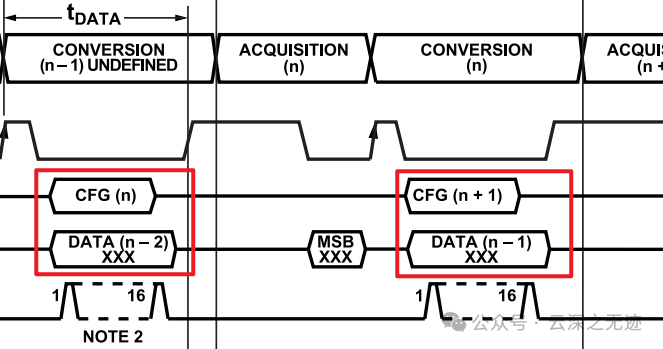

CFG 寄存器是 ADC 的配置寄存器,控制采样速率、输入范围、通道选择等功能。CFG 数据通过 DIN 端输入,在时钟 SCK 的上升沿或下降沿同步写入。配置必须在当前转换周期结束之前完成(即在 EOC 之前),否则会被丢弃。

可以看到符合

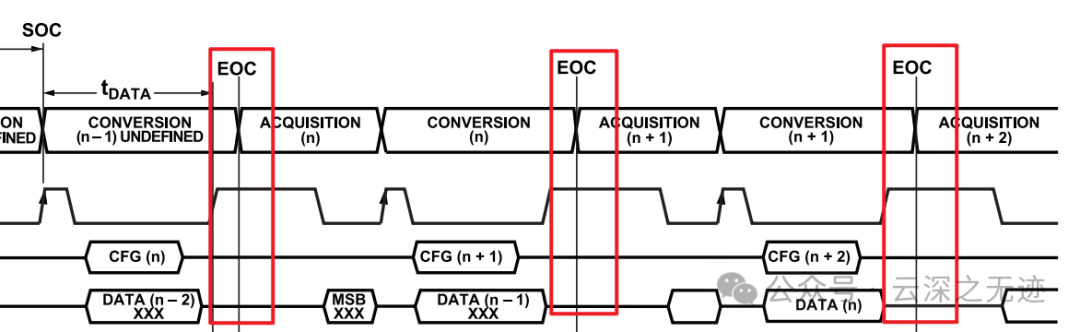

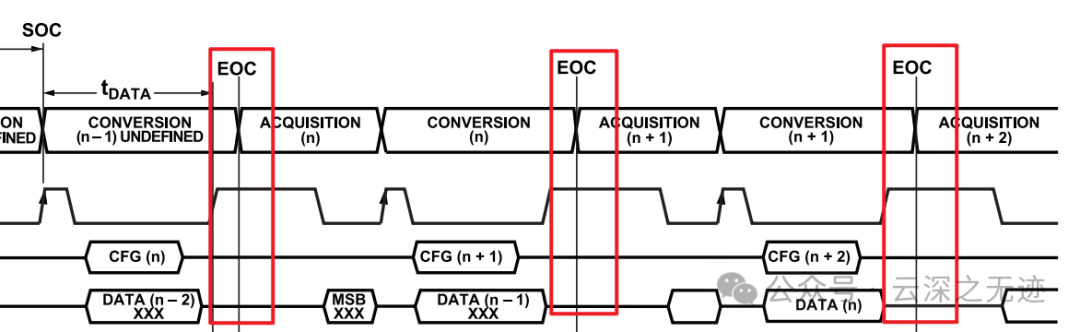

转换完成(EOC)后,转换结果以 MSB(最高有效位) 开始,通过 SDO 串行输出。RDC 模式:数据在当前转换周期(CNV=高)期间读取,读写操作和转换操作并行。

读取的都是前两个周期的转换结果,这也好理解,因为SPI的性质不是实时的改变的,而是读入然后转换,所以有滞后。

RAC 模式:数据在转换完成(EOC)后读取,避免了并行操作。

可以看到时序上面是同步的

RSC 模式:跨越转换周期进行读写操作,同时写入新的配置并读取旧的转换数据。在 EOC 之后,CNV 被拉低,SDO 从高阻状态变为输出转换数据。

看顺序,EOC出现,CNV拉低,然后数据就可以读取了

- CNV 必须在 EOC 前拉高,否则会启用忙指示器(Busy Indicator),可能导致不希望的时序冲突。

- 如果启用了配置寄存器回读功能(CFG Readback),则需要额外的 30 个 SCK 时钟下降沿 来完成数据传输。

- 对于写入配置的情况,数据必须在 n-1 周期 写入,且在 n 周期生效。

https://www.analog.com/media/en/technical-documentation/data-sheets/ad7682_7689.pdf