今天给大侠带来基于FPGA实时时钟的设计,附源码,获取源码,请在“FPGA技术江湖”公众号内回复“基于FPGA实时时钟的设计源码”,可获取源码文件。话不多说,上货。

本次设计采用了美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟电路 DS1302,它可以对年、月、日、周、时、分、秒进行计时,具有闰年补偿功能,工作电压为2.5V~5.5V。采用三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号或RAM数据。DS1302内部有一个31×8的用于临时性存放数据的RAM寄存器。

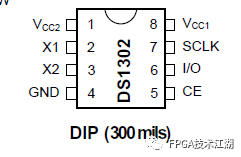

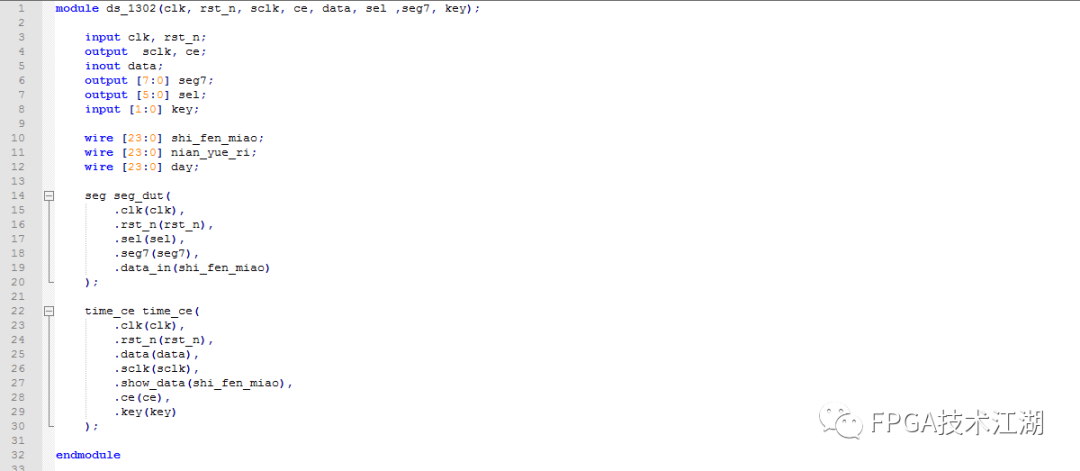

DS1302芯片的封装如下:

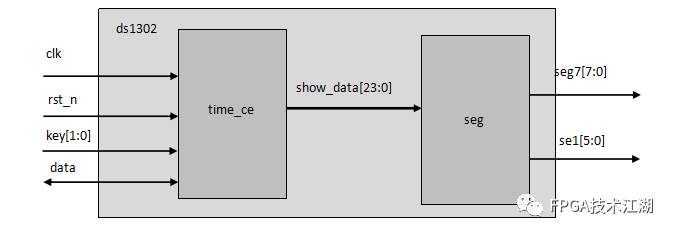

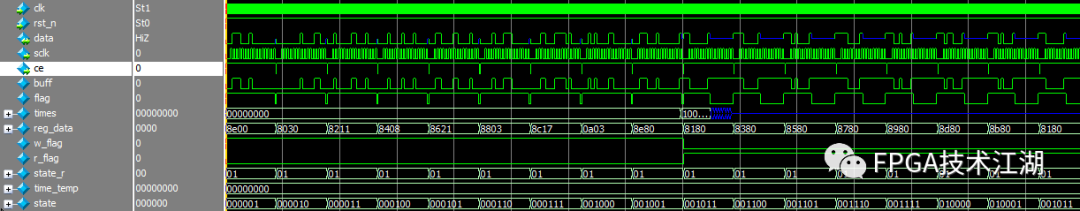

DS1302芯片有8个引脚,在本次的设计中只要驱动3个引脚就可以了,其他的引脚都是和硬件相连接的,和FPGA连接的有时钟sclk,串行数据数据接口IO,以及CE。

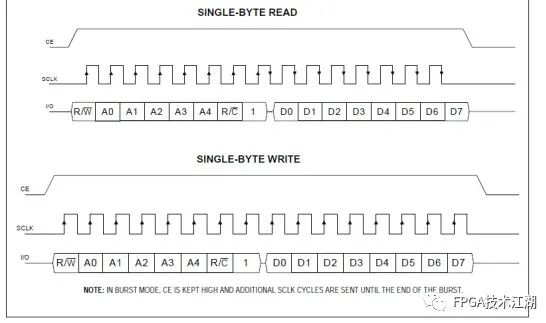

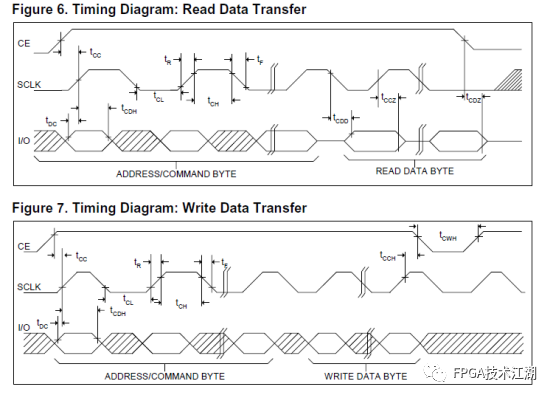

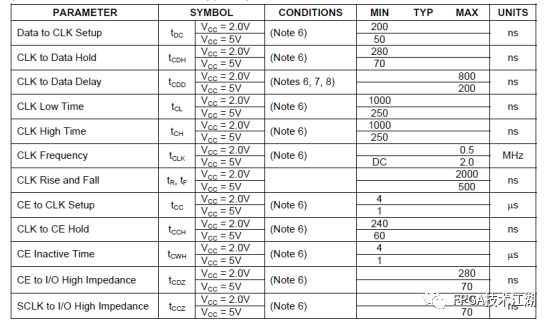

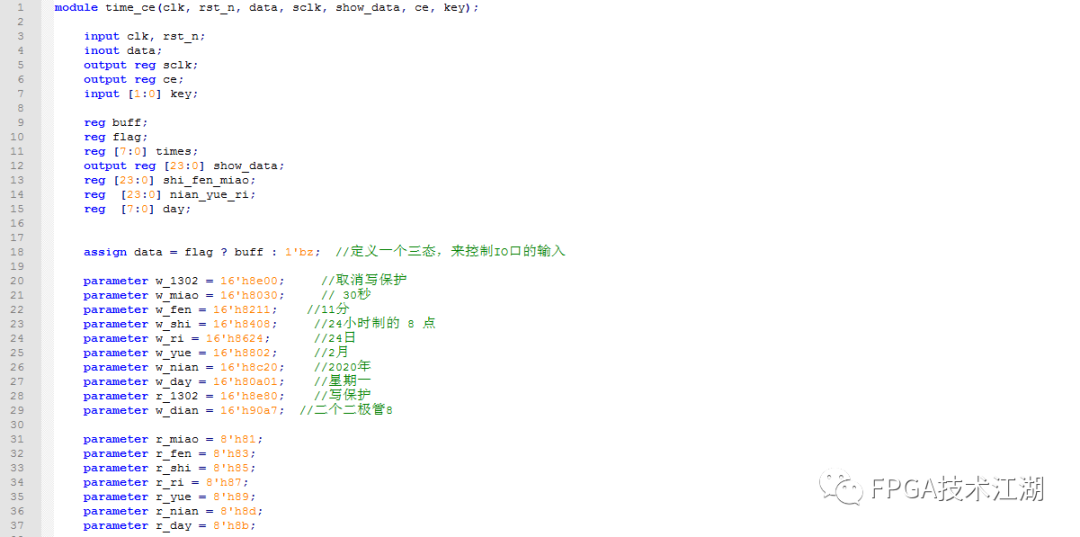

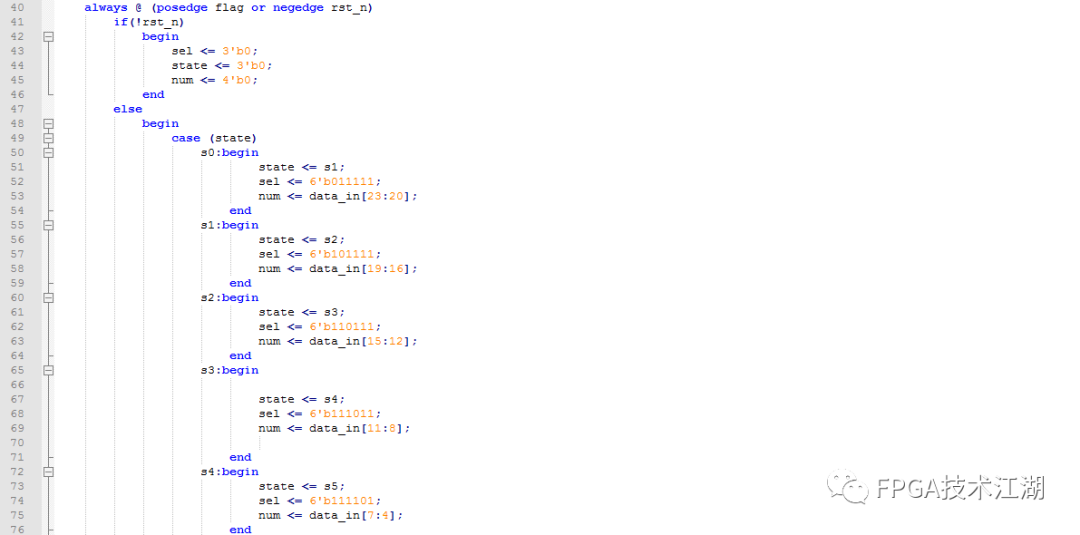

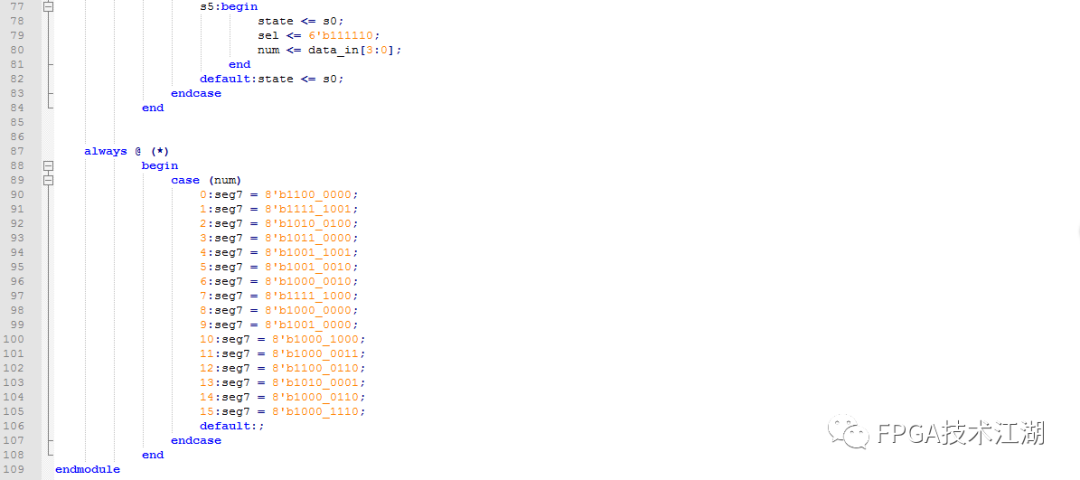

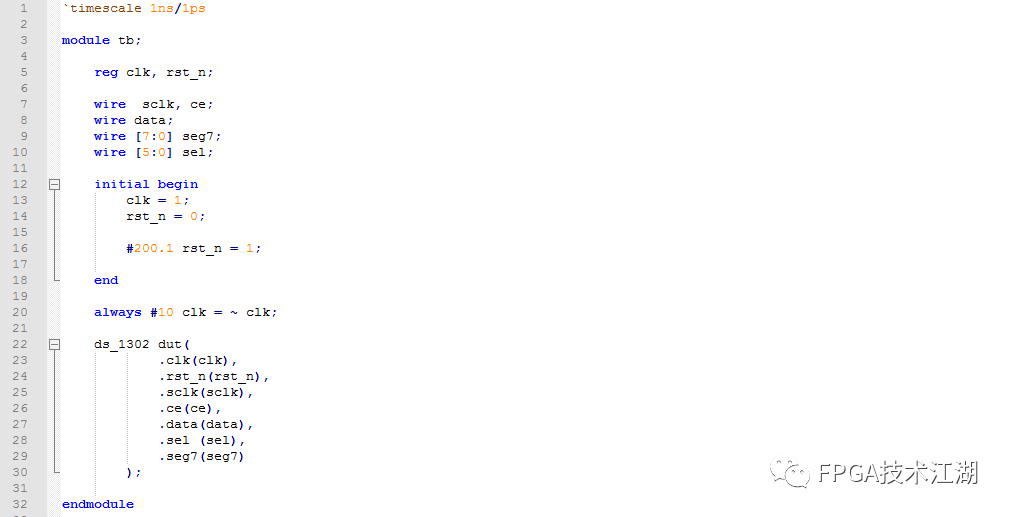

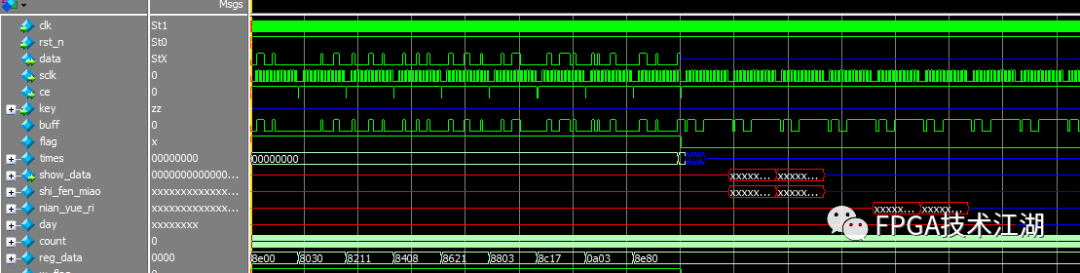

其工作原理就是在数据的传送过程中先把CE拉高,在每个数据的上升沿写入数据,在下降沿输入数据,一次只能读写一位数据。最初我们通过一个8位的控制指令来选择读写,如果控制指令是单字节模式,连续的8个脉冲上升沿写入,下降沿读出数据,一次只能读取一个字节,如果是突发模式通过连续的脉冲一次性的写完7个字节的时间寄存器也可以一次性的读完8--328位的ram数据

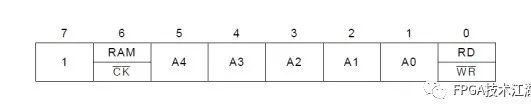

控制指令有8位,第七位必须为高,如果是0写入被禁止,第六位0是对时钟寄存器的读写操作,为1对是控制对RAM区的读写操作。

bit1 -- 5 是对相关寄存器的操作,bit0是读写操作。

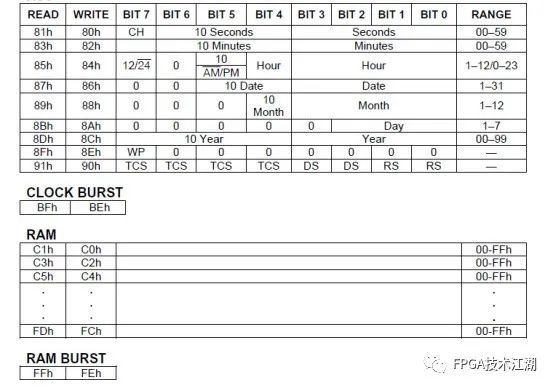

各个寄存器的的设置,和每位的表示如下图,从图中我们了解到读写时控制字是多少以及写入寄存器的地址,和写入的8位的时间表示。我们可以通过下表来设置一个初始的时间。

END

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+学校/公司+专业/岗位进群

FPGA技术江湖QQ交流群

备注姓名+学校/公司+专业/岗位进群