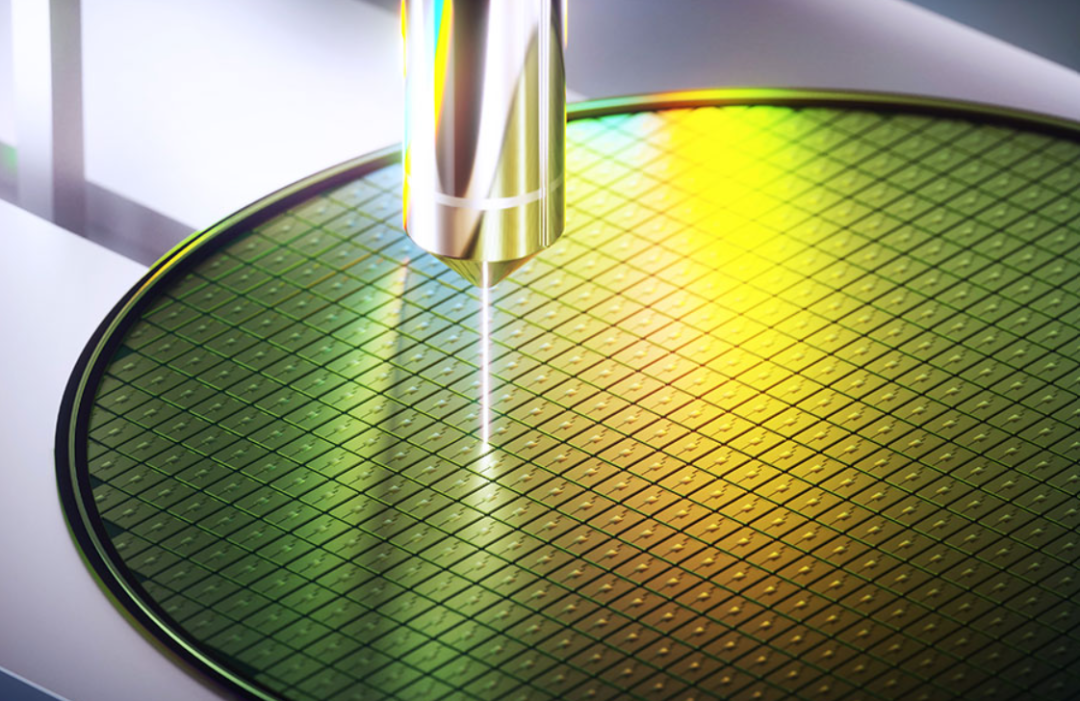

随着半导体制造向先进的工艺节点和更复杂的设计发展,光掩模(光掩膜、光罩)——用于将图案转移到晶圆上的关键工具——在这一进程中扮演着越来越重要的角色。Tekscend Photomask (TOPPAN Holdings凸版印刷)、大日本印刷(DNP)等国际光掩膜生产的领先企业,正在引领行业技术与产业化不断进步。 2024年12月,大日本印刷公司(DNP)宣布成功开发了一种新型光掩膜,这种光掩膜用于制造线宽仅为1纳米的下一代半导体电路。该公司已经开始向半导体制造设备厂商提供样品,预计1纳米半导体技术将在2030年后普及,为人工智能(AI)和自动驾驶技术的进步提供支持。 大日本印刷与比利时的半导体研发机构“imec”合作,开发了用于逻辑半导体的光掩膜,这种光掩膜在硅晶圆上的电路曝光过程中使用。为了实现1纳米级别的精确度,大日本印刷采用了先进的电子束绘图设备,并通过调节感光材料的厚度等参数,确定了最佳的加工条件。 公司计划在2023至2025年间,向光掩膜业务投资200亿日元,目标是到2030年使EUV用光掩膜的销售额达到100亿日元。

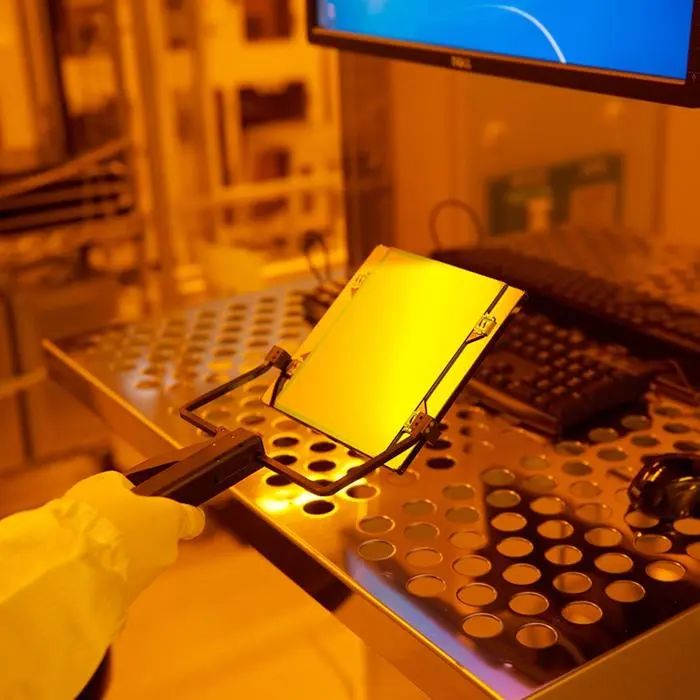

来源:DNP

此外,TOPPAN Holdings旗下的Tekscend Photomask与美国 IBM 签订了共同开发2纳米及以下光掩膜的合同,目标是实现1纳米级别产品的实用化。日本政府也在加快对1纳米级别半导体相关部件的支持,文部科学省在2025年度预算中列入了约40亿日元用于研发新一代半导体。 1纳米半导体被认为在电力效率和运算性能上比2纳米半导体提高10%至20%。例如,在AI领域,1纳米半导体能够更快地提供答案并提高准确率。在自动驾驶领域,1纳米半导体的快速数据处理能力可以提升安全性。 来源:Toppan 光掩膜市场分为代工厂自制和专业厂商外销两种,全球市场中,外销产品占40%,而日本企业在外销产品方面表现强劲。大日本印刷预计,到2027年,外销光掩膜市场规模将比2023年增长40%,达到26.65亿美元。 ——Tekscend Photomask与DNP最新动态 Toppan Photomask,作为全球领先的半导体光掩模供应商,宣布于2024年11月1日正式更名为Tekscend Photomask Corp。此次品牌重塑旨在提升公司在全球先进微加工技术领域的知名度,并增强其在半导体市场的竞争力。 新名称“Tekscend”融合了“技术”和“上升”的含义,象征着公司对技术进步和行业成长的承诺。随着名称的更改,Tekscend Photomask的所有地区子公司也将采用Tekscend品牌。这一统一身份预计将促进各地之间的合作,并推动半导体技术的创新。Tekscend Photomask在2024年11月12日宣布在欧洲安装了首台多束光掩模写入机(Multibeam Mask Writer),这一设备显著减少了复杂设计的掩模写入时间,从几天缩短至仅需7-12小时。这一进展对于保持在全球半导体市场中的竞争力及提升欧洲本地生产能力至关重要。 大日本印刷株式会社(DNP)正在加速开发与EUV(极紫外光)光刻技术兼容的2纳米代逻辑半导体光掩模制造工艺,计划在2025年完成开发,并在2027年开始量产。DNP成功实现了超2纳米一代逻辑半导体光掩模所需的精细图案分辨率,并完成了兼容高数值孔径(NA)2光掩模的标准评估。 DNP计划在2024年底前运行第二个和第三个多电子束掩模写入系统,以全面开发用于2纳米一代EUV光刻的光掩模制造工艺。 大日本印刷与比利时的半导体研发机构“imec”合作,开发了用于逻辑半导体的光掩膜,这种光掩膜在硅晶圆上的电路曝光过程中使用。2024年12月,大日本印刷公司(DNP)宣布成功开发了一种新型光掩膜,用于制造线宽仅为1纳米的下一代半导体电路。 亚化咨询认为,中国企业在成熟制程的崛起,必将驱动国内光罩(光掩模版)的需求。中国市场将为全球光罩产业注入新活力,助推半导体制造迈向更大的规模与更高的水平。亚化咨询研究认为,DNP和Tekscend的成功不仅标志着其在半导体光掩模领域的领导地位,也为日本在下一代半导体关键材料技术的竞争中奠定了基础,值得中国国内的半导体材料企业借鉴 二、日本芯片业弯道超车竞逐1nm

日本领先的半导体材料制造商正在采取战略举措,开发1纳米芯片生产的关键部件,将自己定位于下一代半导体技术的前沿。 大日本印刷公司 (DNP) 在开发 1 纳米级半导体光掩模方面取得了重要里程碑,并已开始向设备制造商分发样品,目标是在 2030 年后实现量产。该公司的突破来自与比利时微电子研究机构 Imec 的战略合作,专注于高数值孔径极紫外 (EUV) 曝光设备的光掩模开发。

通过实施先进的电子束光刻技术和材料优化,DNP成功建立了最佳制造工艺。

该公司的路线图包括到 2027 财年启动 2 纳米光掩模的量产,与国内芯片制造商 Rapidus 的 2 纳米芯片生产时间表保持一致。DNP 预测,到 2027 年,全球外部光掩模市场将扩大 40%,达到 26.7 亿美元。

另一家日本主要材料制造商凸版印刷(Toppan)已于 2023 年开始向 IBM 供应 2 纳米光掩模,并计划在 2026 财年开始量产。该公司已与 Imec 和 IBM 建立了战略合作伙伴关系,共同探索光掩模技术的高级应用。

富士胶片通过推进 1 纳米芯片生产所必需的光刻胶材料,为生态系统做出了贡献,并已承诺投资 130 亿日元建设新的研发中心。为支持这些私营部门的举措,日本教育部已拨款 40 亿日元用于 2025 年的下一代半导体研发。

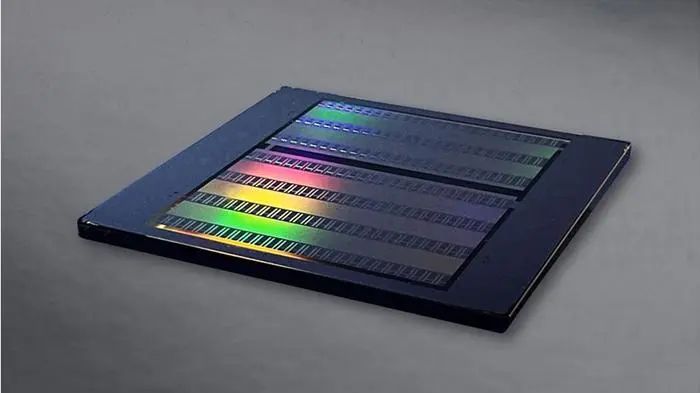

大日本印刷 (DNP) 于 2024 年 12 月 12 日宣布,已成功解决了 2nm 及以后代工艺中逻辑半导体光掩模所需的精细图案,并与 EUV(极紫外)光刻兼容。

此外,DNP还完成了与高数值孔径(NA)兼容的光掩模的基本评估,这些光掩模正在考虑应用于从2nm一代开始的下一代半导体,并将其提供给半导体开发联盟、制造设备制造商、材料制造商。该公司还宣布已开始提供光掩模进行评估。

近年来,针对尖端逻辑半导体,使用EUV光源的EUV光刻的量产不断取得进展。DNP于2023年完成了3nm一代EUV光刻的光掩模制造工艺的开发,并于2024年3月宣布开始全面开发2nm一代逻辑半导体的光掩模制造工艺。作为Rapidus参与的新能源产业技术综合开发机构(NEDO)的分包商,我们将生产用于尖端逻辑半导体开发的光掩模。与流程和保证相关的技术。

此次,DNP成功将2nm及以后代逻辑半导体光掩模所需的精细图案解析为EUV光刻用光掩模,旨在实现先进半导体制造。为了实现2nm及以后代EUV光刻的光掩模,需要比3nm代小20%以上的图案,并且形状不限于典型的线性或矩形图案,也正在变得越来越小。这需要能够在同一掩模上解析所有精细图案(包括弯曲图案)的技术。针对这些挑战,DNP通过在既定的3nm代制造工艺的基础上进行反复改进,已经达到了2nm代及以后代所需的图案分辨率。

此外,我们还完成了与High NA兼容的EUV光掩模的基本评估,这些光掩模正在考虑用于从2nm一代开始的下一代半导体,并已开始提供样品掩模。用于高NA-EUV光刻的光掩模比常规EUV光刻需要更高的精度和更精细的加工,但DNP创建了与常规EUV光刻的光掩模不同的制造工艺流程,并在此基础上进行了优化。

DNP 将继续建立可提高制造良率的生产技术,并计划于 2027 财年开始为 2nm 代逻辑半导体提供量产光掩模。此外,我们将与imec合作,继续开发光掩模制造技术,着眼于1nm一代。“我们将与国际半导体行业的各个合作伙伴合作促进发展,为日本半导体行业的发展做出贡献。”