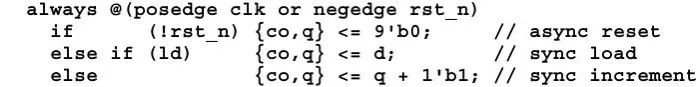

使用异步复位的最大优势是,数据路径就可以保证是干净的。对于同步复位,数据路径要插入逻辑,会增加门和额外的延迟。

使用异步复位,设计人员可以保证复位不会被添加到数据路径中。

一个有利于异步复位的优点是,电路可以在有时钟或没有时钟的情况下复位。

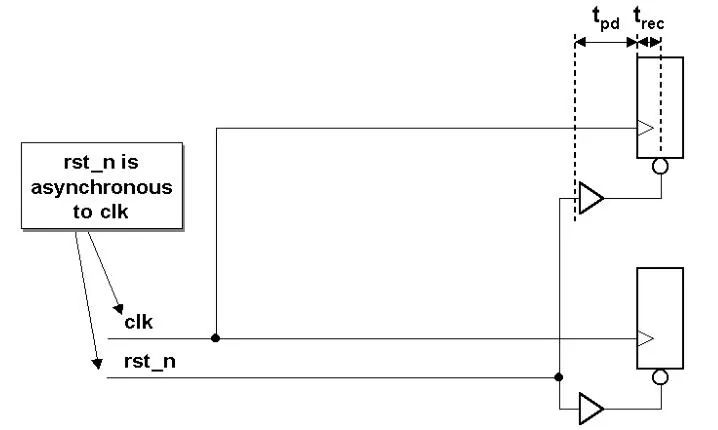

异步复位最大的问题在于复位时序是异步的,复位不是问题,解复位才是问题。如果异步复位是在触发器的有效时钟沿附近释放的,则触发器的输出可能会进入亚稳态,从而丢失复位状态。

对于上图这个设计,异步复位信号相对时钟是异步的。存在两个潜在问题:(1)违反复位恢复时间,(2)不同时序元件的复位移除发生在不同的时钟周期。

1-重置恢复时间

重置恢复时间是指重置被释放和时钟信号再次变高之间的时间。sdf有3个概念来建模恢复时间和信号移除时间检查:$recovery, $removal和$recrem(后者是恢复和移除时间检查的组合)。这些时序违例会导致设计进入亚稳态。

2-重置释放跨越不同的时钟周期

复位移除与时钟上升沿不同步时,复位信号和时钟信号中任一者的传播延迟的微小差异可能会导致某些触发器先于其他触发器的退出复位状态。

「数字芯片设计【不定期更新文件】」链接:https://pan.quark.cn/s/27331927a18e

*免责声明:本文由作者原创。文章内容系作者个人观点,路科验证转载不代表路科验证对该观点赞同或支持,如果有任何异议,欢迎联系路科验证。