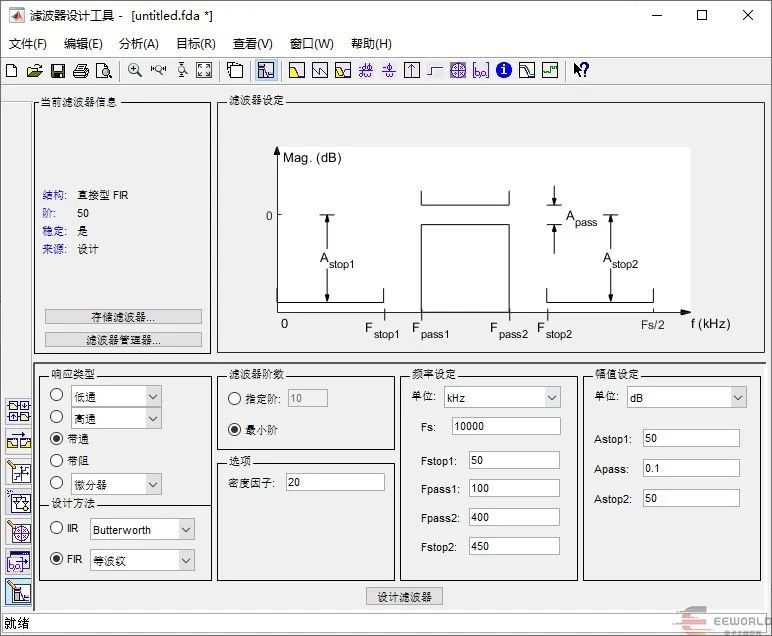

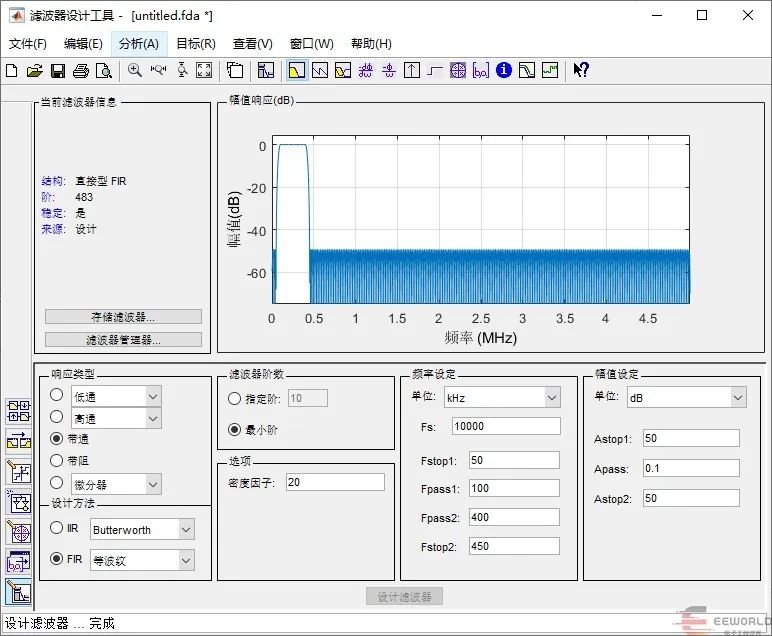

设计一个带通滤波器,并验证其功能。

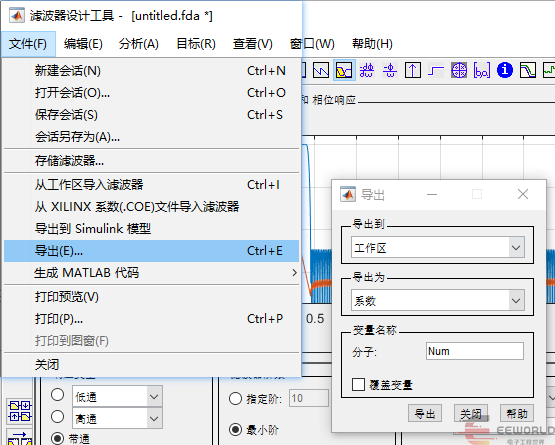

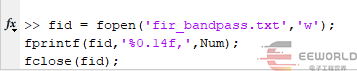

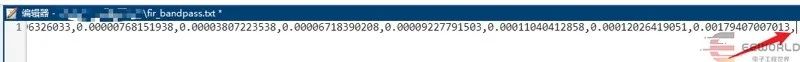

1、使用MATLAB设计滤波器系数

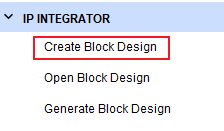

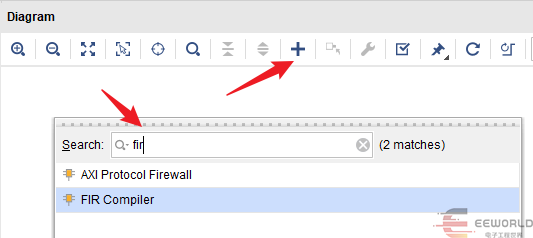

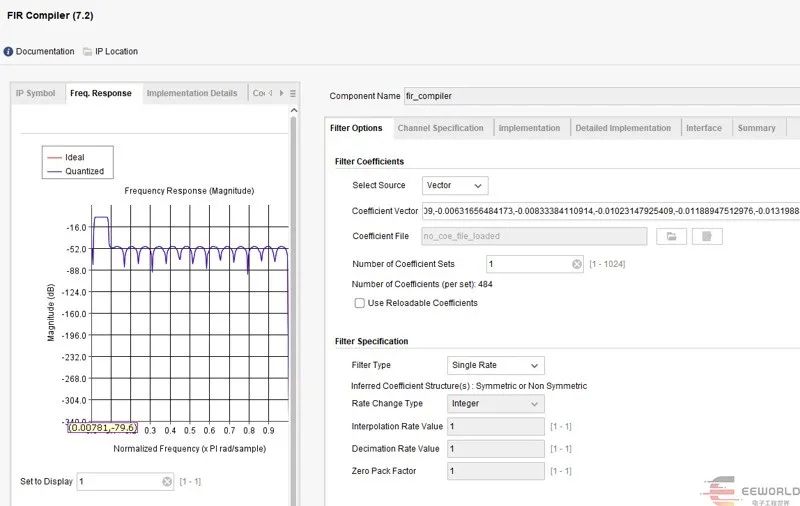

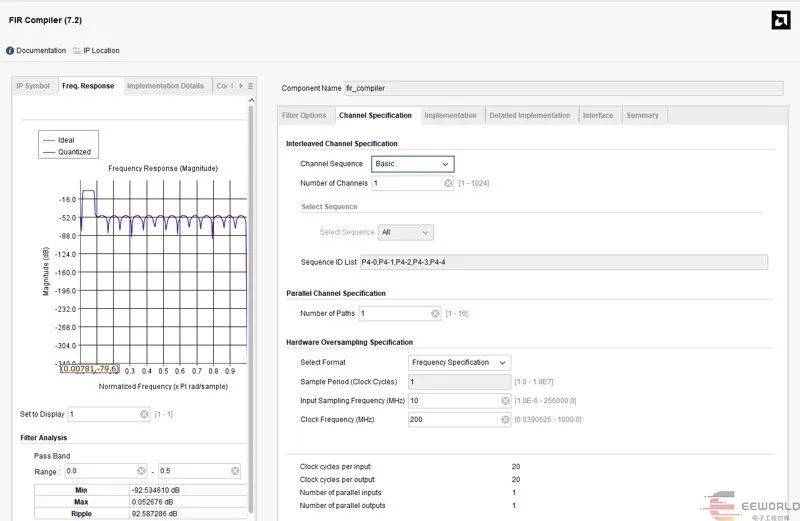

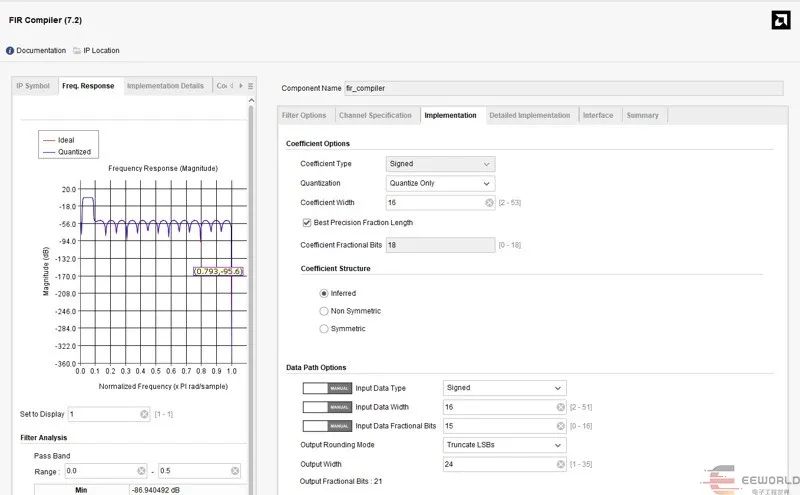

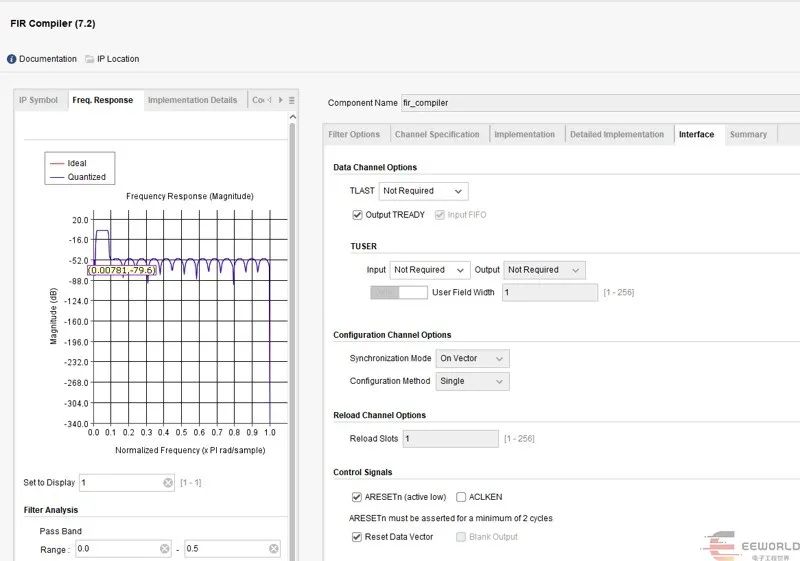

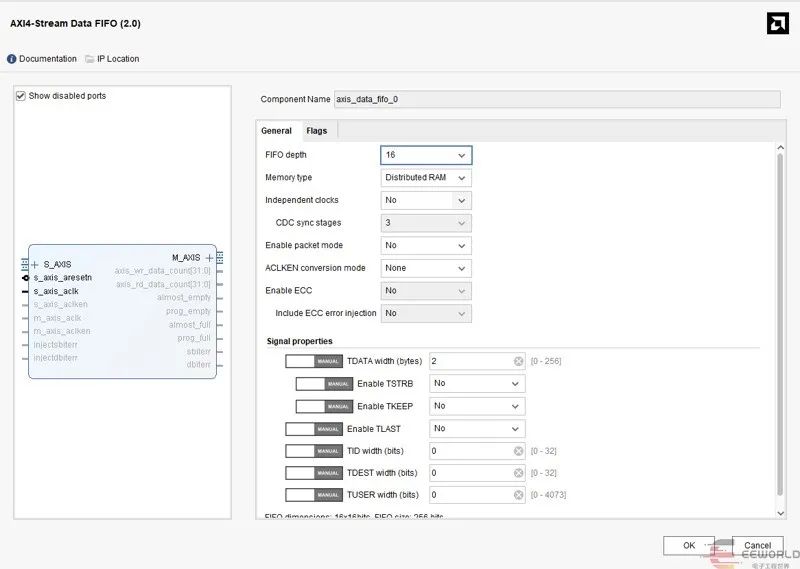

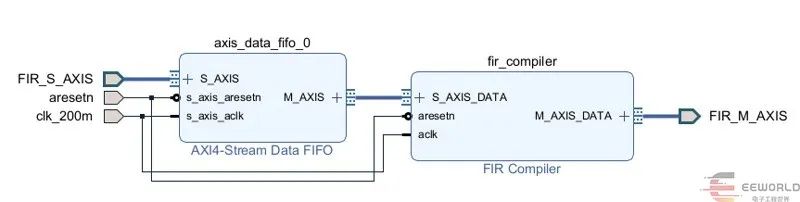

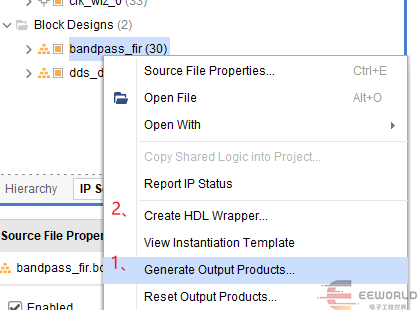

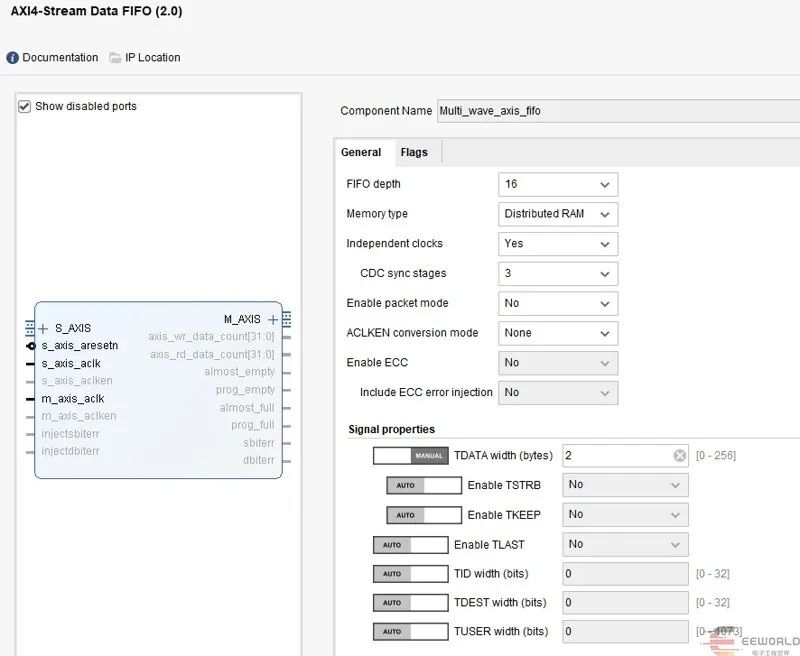

2、FPGA中FIR的实现

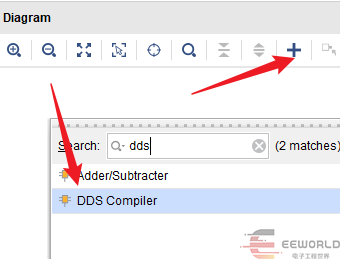

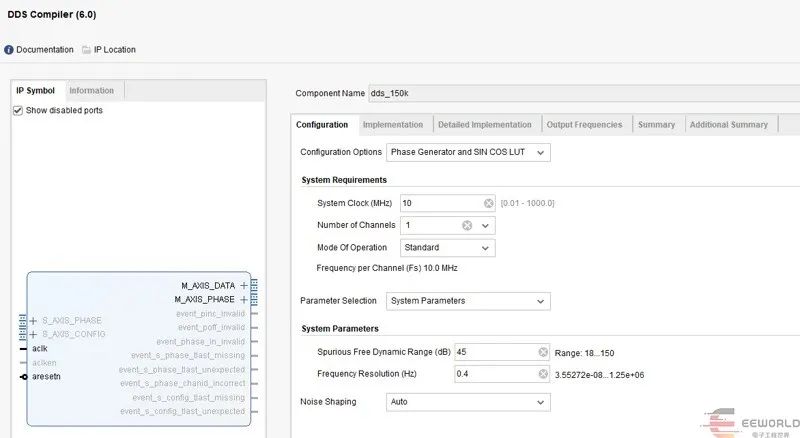

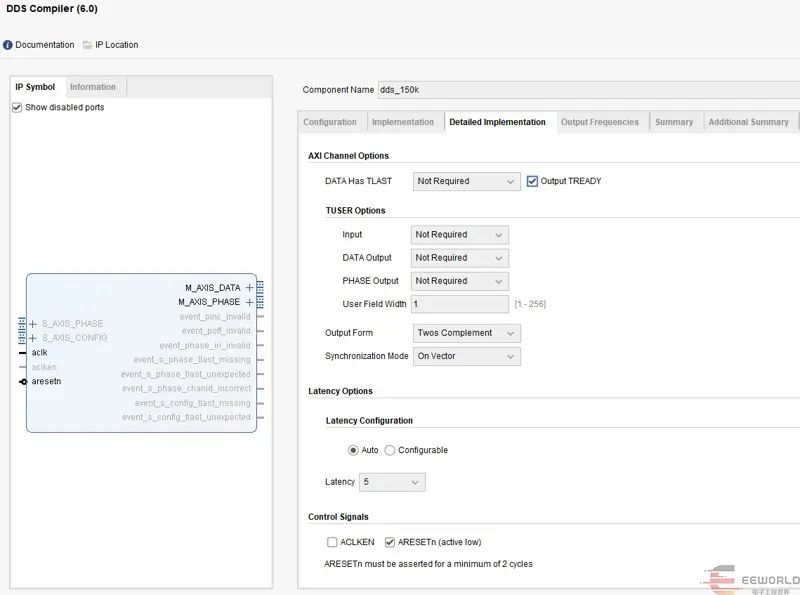

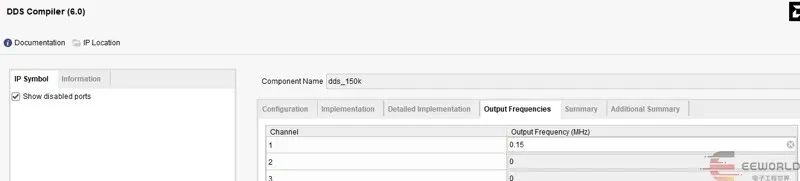

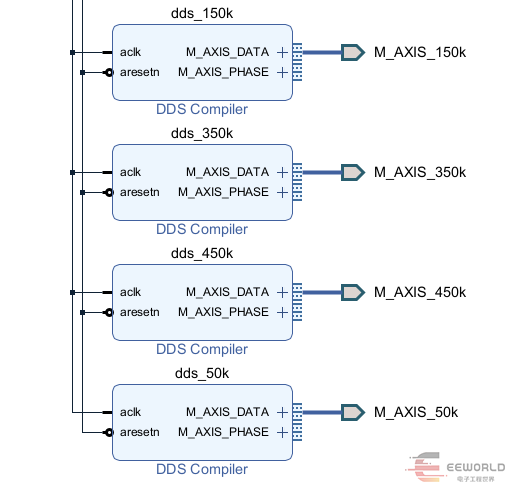

3、FPGA中DDS的实现

这里DDS用于产生FIR的输入信号。同样点击Create Block Design,添加DDS IP核。

4、top模块编写

module fir_top(

input pl_ref_clk_100m_p,

input pl_ref_clk_100m_n

);

reg [4:0] cnt;

wire clk_10m,clk_200m;

wire signed [7:0] M_AXIS_50k_tdata;

wire M_AXIS_50k_tvalid,M_AXIS_50k_tready;

wire signed [7:0] M_AXIS_150k_tdata;

wire M_AXIS_150k_tvalid,M_AXIS_150k_tready;

wire signed [7:0] M_AXIS_350k_tdata;

wire M_AXIS_350k_tvalid,M_AXIS_350k_tready;

wire signed [7:0] M_AXIS_450k_tdata;

wire M_AXIS_450k_tvalid,M_AXIS_450k_tready;

wire signed [15:0] Multi_wave_S_AXIS_tdata;

wire Multi_wave_S_AXIS_tvalid,Multi_wave_S_AXIS_tready;

wire signed [15:0] Multi_wave_M_AXIS_tdata;

wire Multi_wave_M_AXIS_tvalid,Multi_wave_M_AXIS_tready;

wire signed [15:0] FIR_S_AXIS_tdata;

wire FIR_S_AXIS_tvalid,FIR_S_AXIS_tready;

wire signed [23:0] FIR_M_AXIS_tdata;

wire FIR_M_AXIS_tvalid,FIR_M_AXIS_tready;

assign rst_n = locked;

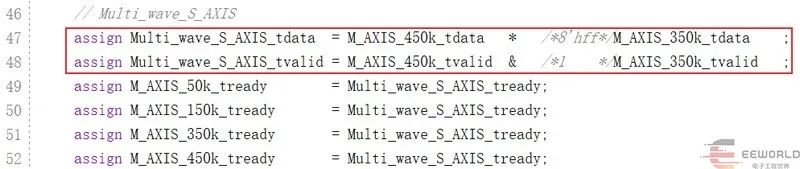

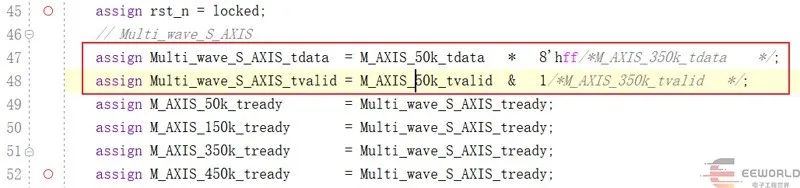

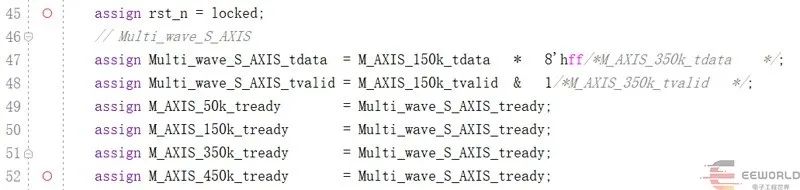

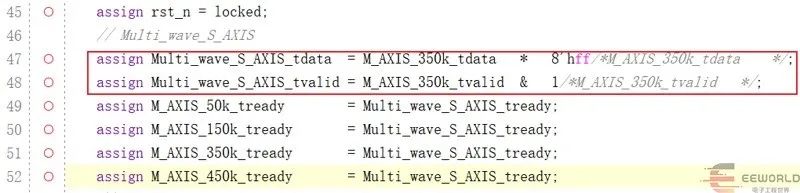

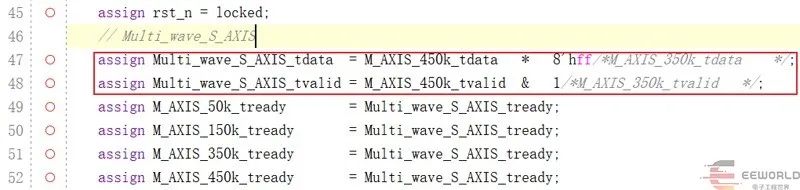

// Multi_wave_S_AXIS

assign Multi_wave_S_AXIS_tdata = M_AXIS_450k_tdata * 8'hff/*M_AXIS_350k_tdata */;

assign Multi_wave_S_AXIS_tvalid = M_AXIS_450k_tvalid & 1/*M_AXIS_350k_tvalid */;

assign M_AXIS_50k_tready = Multi_wave_S_AXIS_tready;

assign M_AXIS_150k_tready = Multi_wave_S_AXIS_tready;

assign M_AXIS_350k_tready = Multi_wave_S_AXIS_tready;

assign M_AXIS_450k_tready = Multi_wave_S_AXIS_tready;

// Multi_wave_M_AXIS

assign FIR_S_AXIS_tvalid = Multi_wave_M_AXIS_tvalid;

assign FIR_S_AXIS_tdata = Multi_wave_M_AXIS_tdata;

assign Multi_wave_M_AXIS_tready = FIR_S_AXIS_tready;

assign FIR_M_AXIS_tready = (cnt == 'd19) && Multi_wave_M_AXIS_tvalid;

dds_design_wrapper dds_design(

.M_AXIS_150k_tdata (M_AXIS_150k_tdata ),

.M_AXIS_150k_tready (M_AXIS_150k_tready ),

.M_AXIS_150k_tvalid (M_AXIS_150k_tvalid ),

.M_AXIS_350k_tdata (M_AXIS_350k_tdata ),

.M_AXIS_350k_tready (M_AXIS_350k_tready ),

.M_AXIS_350k_tvalid (M_AXIS_350k_tvalid ),

.M_AXIS_450k_tdata (M_AXIS_450k_tdata ),

.M_AXIS_450k_tready (M_AXIS_450k_tready ),

.M_AXIS_450k_tvalid (M_AXIS_450k_tvalid ),

.M_AXIS_50k_tdata (M_AXIS_50k_tdata ),

.M_AXIS_50k_tready (M_AXIS_50k_tready ),

.M_AXIS_50k_tvalid (M_AXIS_50k_tvalid ),

.Multi_wave_M_AXIS_tdata (Multi_wave_M_AXIS_tdata ),

.Multi_wave_M_AXIS_tready(Multi_wave_M_AXIS_tready),

.Multi_wave_M_AXIS_tvalid(Multi_wave_M_AXIS_tvalid),

.Multi_wave_S_AXIS_tdata (Multi_wave_S_AXIS_tdata ),

.Multi_wave_S_AXIS_tready(Multi_wave_S_AXIS_tready),

.Multi_wave_S_AXIS_tvalid(Multi_wave_S_AXIS_tvalid),

.aresetn (rst_n ),

.clk_10m (clk_10m ),

.clk_200m (clk_200m )

);

always@(posedge clk_200m or negedge rst_n)begin

if(!rst_n)begin

cnt <= 'd0;

end

else begin

cnt <= (cnt == 'd19)? 'd0 : (cnt + 1'b1);

end

end

bandpass_fir_wrapper bandpass_fir(

.FIR_M_AXIS_tdata (FIR_M_AXIS_tdata ),

.FIR_M_AXIS_tready (FIR_M_AXIS_tready ),

.FIR_M_AXIS_tvalid (FIR_M_AXIS_tvalid ),

.FIR_S_AXIS_tdata (FIR_S_AXIS_tdata ),

.FIR_S_AXIS_tready (FIR_S_AXIS_tready ),

.FIR_S_AXIS_tvalid (FIR_S_AXIS_tvalid ),

.aresetn (rst_n ),

.clk_200m (clk_200m )

);

clk_wiz_0 pll(

.clk_10m(clk_10m),

.clk_200m(clk_200m), // output clk_200m

.reset(1'b0), // input reset

.locked(locked), // output locked

.clk_100m_in(clk_100m) // input clk_100m_in

);

IBUFDS clk_100m_ibufds(

.O (clk_100m),

.I (pl_ref_clk_100m_p),

.IB (pl_ref_clk_100m_n)

);

endmodule

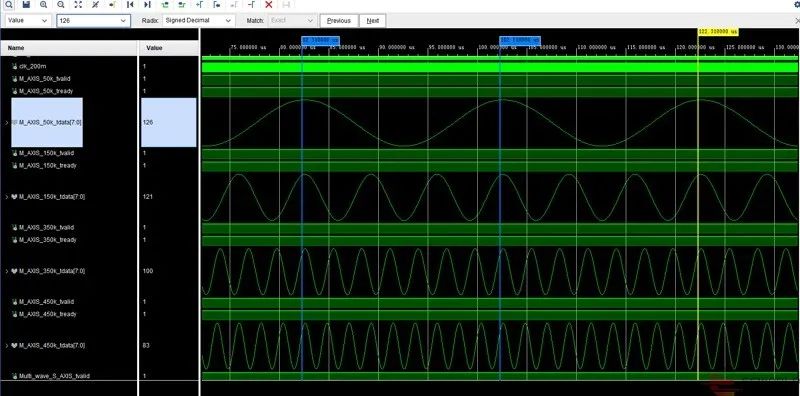

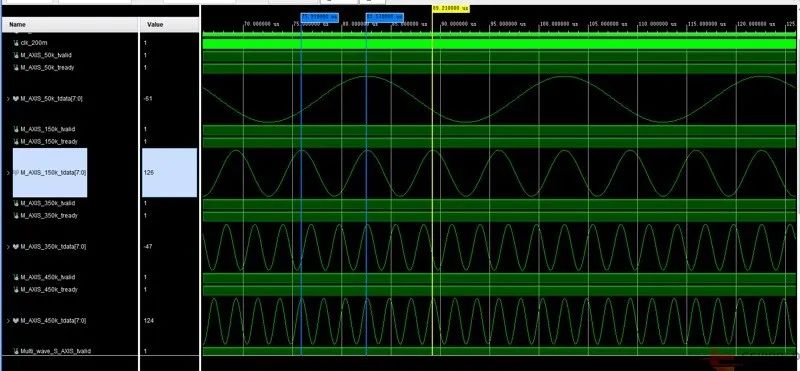

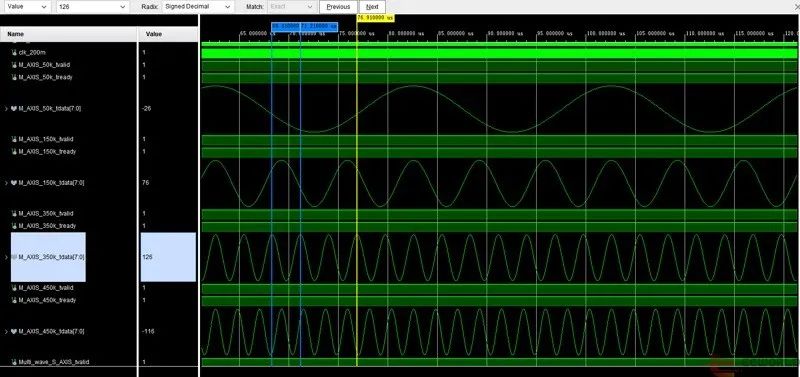

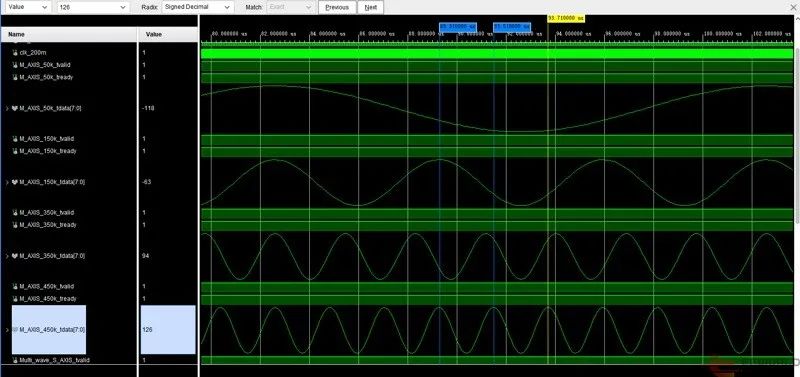

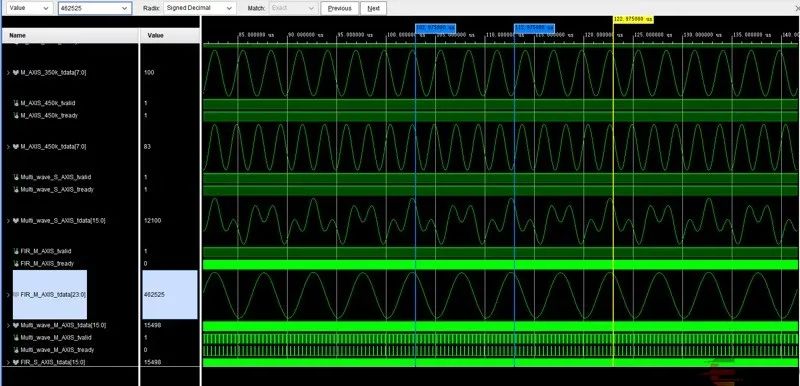

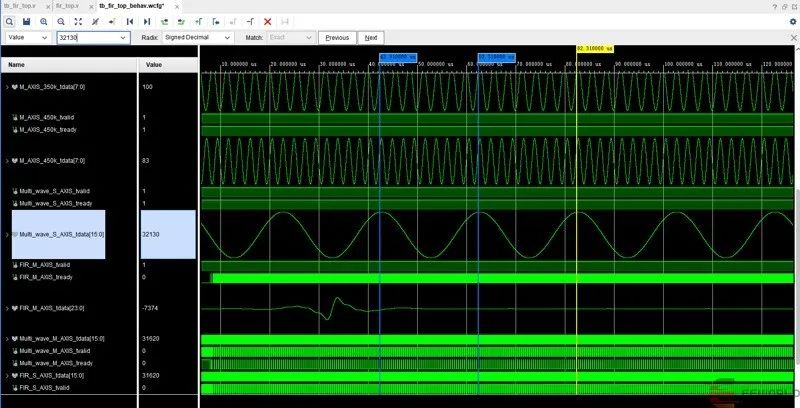

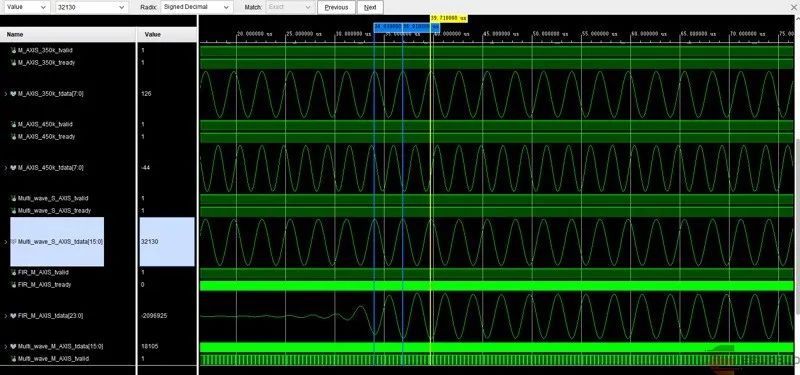

5、功能仿真

6、结论

· END ·

扫码添加小助手回复“进群”

和电子工程师们面对面交流经验