动动手指,关注公众号并加星标哦

(1)

以前有很多人问,运放系列视频的链接,我已经把那个下载下来,可以文末扫码自取。不过,那个原视频,有几集没有字幕,再加上up主是印式英语,所以英语欠佳如我的,就凑合着板书看吧。

还好,对着板书,能猜出个七七八八。

在那个视频中,up主简单的提了一下,MOS管的两个效应,即分别是Body Effect和Channel-Length Modulation。

对于Body Effect,在选择Vth的时候,稍稍选的大了一点。

对于Channel-length Modulation,则把管子的沟道长度选大了,虽然用的工艺是180nm的,但是在进行设计的时候,把L选成了1um(单级运放)和500nm(双级运放)。

(2)

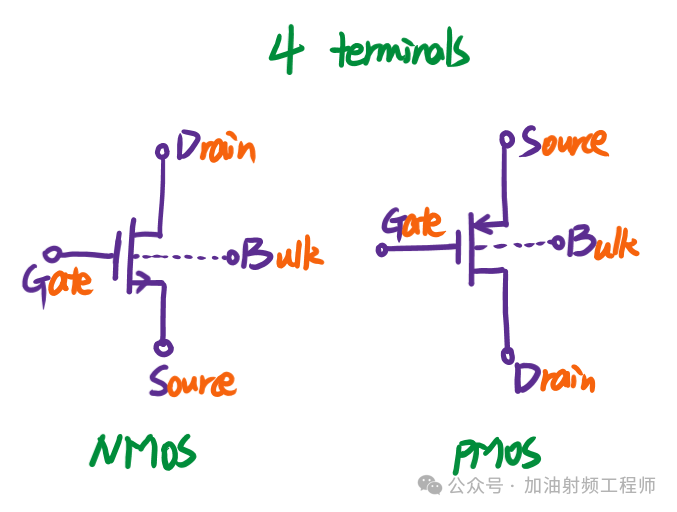

MOS管,有四个端子,分别为gate、source、drain和sub(bulk),如下图所示。

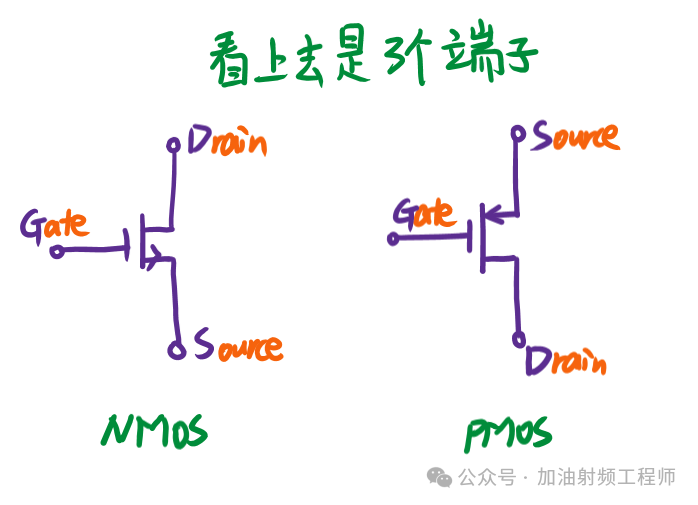

很多时候,看到的NMOS的符号表示只有三个端子,如下图所示。这是因为,这个时候,默认source和substrate处于同一电位。比如对于NMOS来说,同时接地;而对于PMOS来说,同时接VDD。

Body Effect,大概是这样一个现象,就是MOS管的souce和sub不在同一电位,source要比sub(bulk)的电压高一点,从而导致这个器件的Vth的值也跟着变化。

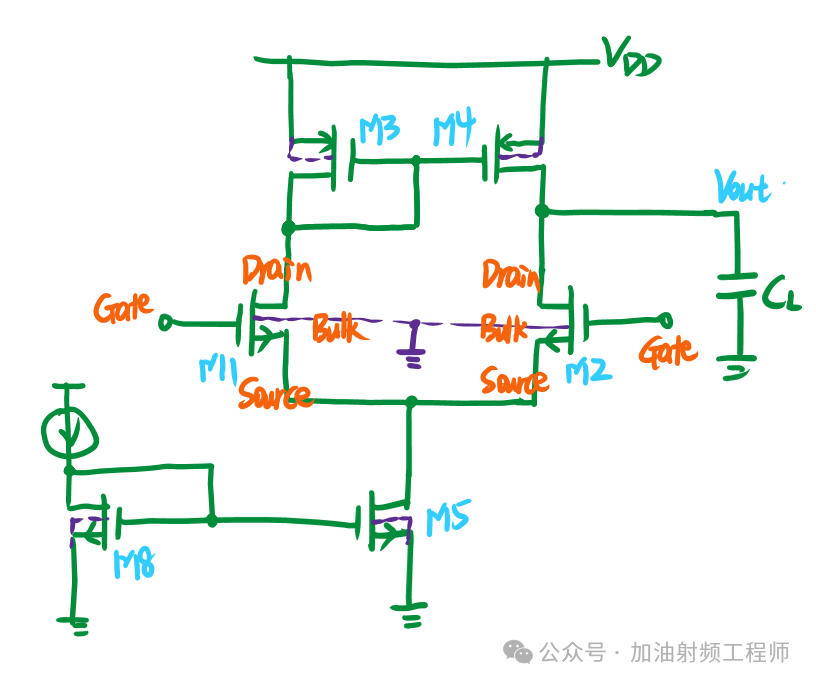

而在运放的架构中,由于M5的存在,M1、M2的source和bulk不是在同一个电位。bulk端子,也就是NMOS管的衬底,接地;而source端子,则是正电压。

在文献[1]中,是这样描述Body Effect,本人翻译水平有限,介意可看原文。

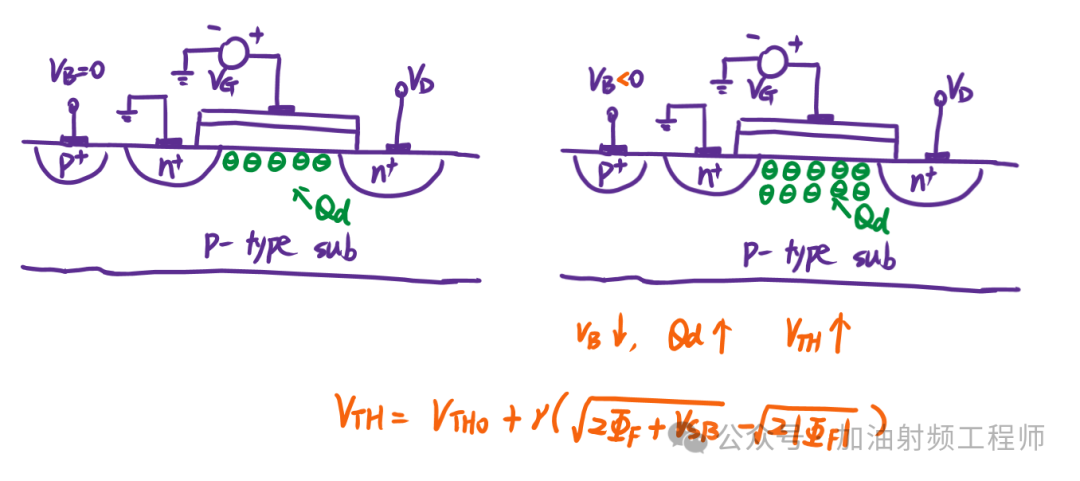

如果NFET的bulk电压比source电压低,会怎么样呢?因为S和D结仍然处于反偏状态,所以我们推测,器件仍然会正常工作,但是它的一些特性会发生改变。为了理解这个效应,假定VS=VB=0(原文中是VD=0,但是和文中图示不符),VG

当VB变的更负时,跟过空穴会被吸引到衬底连接处,留下更多负电荷,从而形成更大的耗尽区。在反型层形成之前,栅极电荷必须镜像Qd,所以Vth是耗尽层中总电荷的函数。因此,当Vb下降时,Qd上升,从而Vth也上升。这种现象,被称为“body effect”或者"back-gate effect"。

整个过程如下图所示。至于下图中的公式是怎么来的,试着了解了一下,发现以目前的认知,还看不懂,暂且放放。

(3)

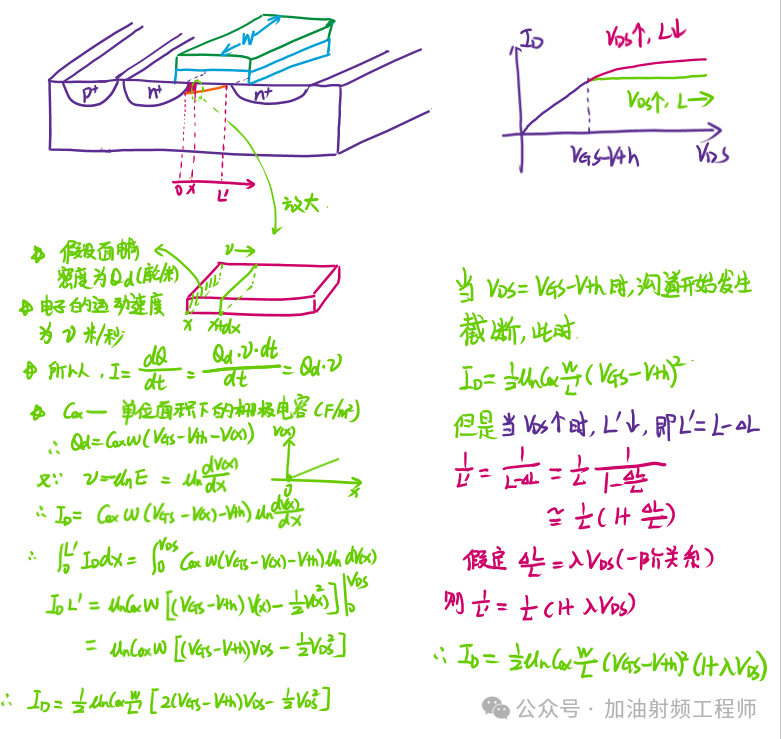

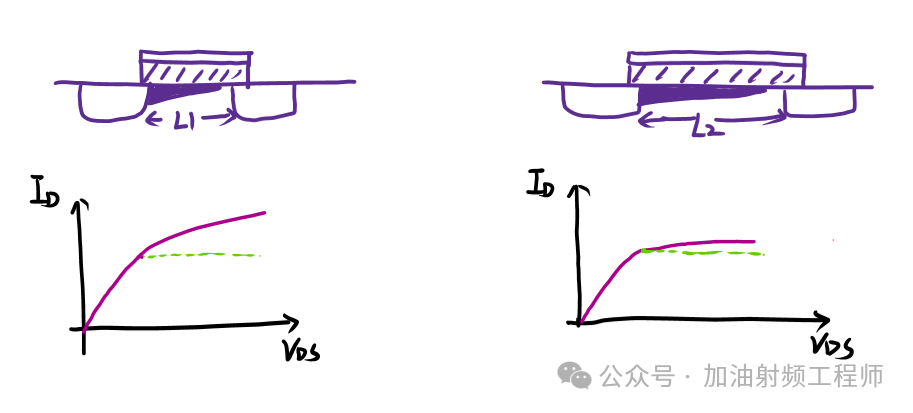

在分析沟道长度随VDS的变化的时候,为了简化起见,刚开始,是假定沟道长度不随VDS变化而发生变化的。但是实际上,实际的沟道长度是随着VDS的增加,而缓慢减小的,这种现象称为沟道调制效应,即"channel-length modulaiton"。

在运放视频中,之所以把沟道长度选大,就是因为沟道长度越长,而变化的长度绝对值本身就不大,所以沟道长度的相对变化△L/L就相对要小,从而减少沟道长度效应对理论计算的影响。

参考文献:

[1] Behzad Razavi, Design of Analog CMOS Integrated Circuits

[2] Behzad Razavi, Fundamentals of Microelectronics

运放系列视频,扫码自取:

完结接收机课程吆喝处哈(已在平台上购买的同学,加我微信,领课件资料哈!)

想报名的同学,可以海报底部扫码哈!

想了解射频系统的同学,可以添加我的微信RF606yuer,备注:射频系统书籍,可以领取37本关于射频系统的书籍。

☜左右滑动查看更多

Slide for more photos