与几十年前乃至十几年前相比,我们今天所使用的电子设备无疑更轻便、更好用。这在很大程度上得益于它们所搭载的芯片,这些芯片不仅晶体管数量更多,性能更强大,而且能效比也显著提高。

芯片上晶体管数量的变化有何规律?摩尔定律(Moore’s Law),一个来自1965年的预言,在今天仍然适用。

来历

通过仔细观察新兴技术趋势,英特尔公司联合创始人戈登·摩尔(Gordon Moore)相信,芯片上的晶体管数量将会以指数速度大幅提升,同时相对成本则会显著下降。

在1965年,他首次提出这一预测,并发表了一篇短文进一步阐述了这个观点,预测集成电路上的晶体管数量将每年翻一番。1975年,他将他的预测调整为:集成电路上的数量将每两年翻一番,而成本只会略有增加。这就是我们今天所说的摩尔定律。

尽管并非物理定律和自然规律,但作为半导体行业“自我实现的预言”,摩尔定律一直成立。它推动着包括英特尔在内的整个半导体行业不断探索技术创新,造出速度更快、体积更小、价格更实惠的晶体管。

现在

持续创新是摩尔定律的基石。

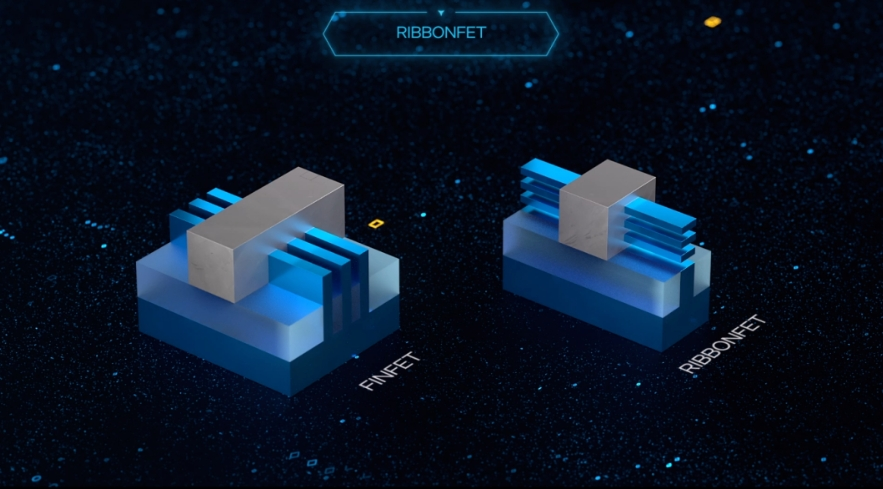

五十多年来,工程师们不断按照摩尔定律的节奏,将越来越多的晶体管装进越来越小的芯片里。英特尔在相关的基础工艺创新方面硕果累累,如应变硅(strained silicon)、Hi-K金属栅极(Hi-K metal gate)和FinFET晶体管,都带来了功耗和成本的持续降低和性能的不断增长。现在,通过制程、封装和架构等方面的持续创新,英特尔在持续推进摩尔定律。

RibbonFET全环绕栅极(GAA)晶体管,使得栅极能够全面环绕带状的晶体管沟道,这带来了三大优势:晶体管沟道的垂直堆叠相较于水平堆叠,大幅节约了空间;栅极的全面环绕增强了对电流的控制,让晶体管开关的速度更快,实现了性能提升;晶体管沟道可以调整宽度,为芯片设计带来了更高的灵活性。

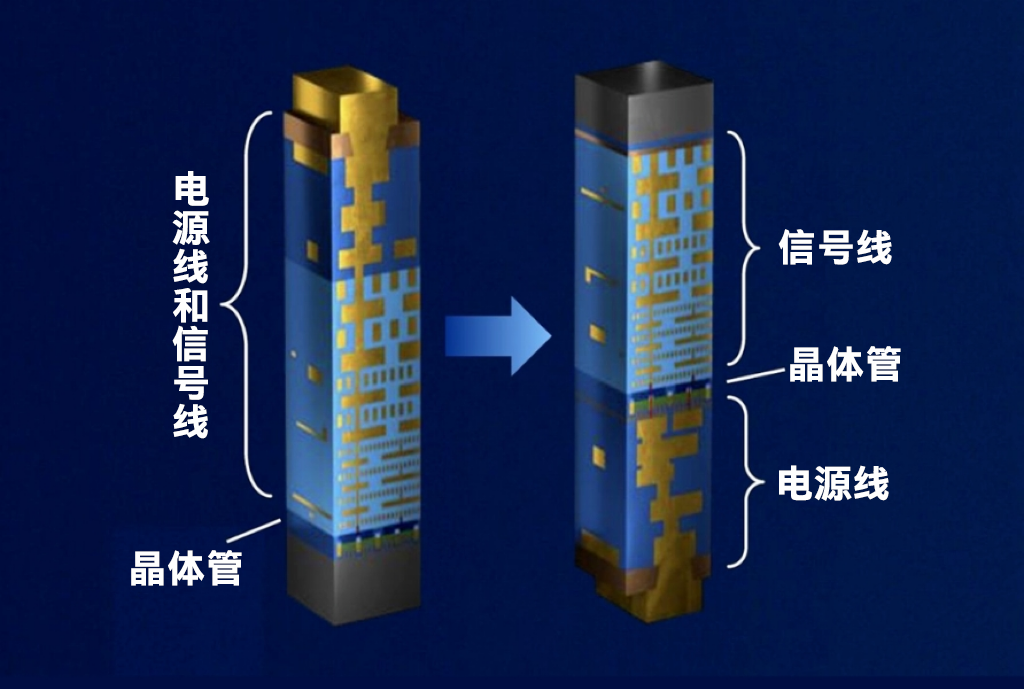

PowerVia背面供电技术实现了电源线与互连线的分离,将电源线迁移至晶体管底层,让晶体管的供电路径变得更加直接,有效改善了供电,减少了信号串扰,降低了功耗。同时,这种新的供电方式还让芯片内部的空间利用更高效,有助于晶体管的进一步微缩。

此外,先进封装技术也提供了推进摩尔定律的新工具,通过让设备内的芯片以更紧密的方式相互连接,同样能够增加集成的晶体管数量。通过EMIB(嵌入式多芯片互连桥接)2.5D技术,英特尔实现了芯片的侧向互连,通过一个嵌入基板内部的芯片把不同的芯片放在同一块平面上相互连接。Foveros 3D先进封装技术则支持以垂直方式堆叠芯片。

未来

作为在未来继续推进摩尔定律的技术储备,英特尔还在以下前沿领域进行了探索:

关键技术

既包括让晶体管更小、更快的技术,也包括改善多芯片封装的技术,以提高每瓦特性能:

● 新型晶体管设计

● 光刻技术突破

● 先进封装

新概念

基于物理学的创新和突破推进芯片的设计和制造,探索未来计算的新可能:

● 新型开关

● 性能提升

● 能效比提升

新功能

进一步拓展硅技术,满足未来的供电和存储需求:

● 更高效的供电

● 更大的内存资源

● 材料领域的突破

讲完了晶体管和摩尔定律,下一期的“5分钟小科普”将带大家走近半导体制造,敬请期待!

©英特尔公司,英特尔、英特尔logo及其它英特尔标识,是英特尔公司或其分支机构的商标。文中涉及的其它名称及品牌属于各自所有者资产。

相关资讯

/转载请注明出处/