Adcom Computers 利用 Xpedition 实现协作、提高可靠性并缩短产品上市时间

2017 年和 2015 年 PCB 设计技术领导奖 (TLA) 获得者

关于 ADCOM

20 世纪 80 年代早期,以色列的Adcom是电话交换中心、自动拨号器和电话编目领域的先驱。到20 世纪 80 年代晚期,他们开始为电子设计公司和大型国防客户(如Elbit 和 Rafael)开发测试设备。几年后,Adcom 开始定制产品设计,于 2000 年迁移到 Mentor Xpedition®平台,以满足客户对新产品和独特产品的需求。

如今,Adcom 的业务在军事/国防和民用公司之间平分秋色,他们使用 Xpedition 设计了数百个项目。

Adcom 计算机和通信公司不惧怕挑战。为了满足尝试新事物的愿望,Adcom采用最新 PCB 设计技术,确保客户获得高质量、可靠的产品并按时交付。

缩短产品上市时间是一项巨大的挑战。为了避免时间安排上依赖外部承包商,Adcom 尽可能使用内部专家,沟通交流和协同设计对他们的成功至关重要。Mentor 的 Xpedition® 平台支持这种设计流程,允许 Adcom 团队高效协作。

“Xpedition让我们能够将周期时间缩短15-20%”Adcom 计算机和通信公司团队领导Moshe Frid 表示。

“能够让几个人同时为同一产品开展工作,有助于缩短产品上市时间,没有什么比 Xpedition 做得更好。”

— MOSHE FRID,ADCOM 团队领导

在电路图设计阶段使用基于流程的并行方法,团队成员可以实时使用同一个数据库,而无需分割和重新组装。这使他们能够并行工作,而不会出现一致性问题。

Adcom 团队领导 Moshe Frid 表示:“我们在整个设计流程中相互协作。例如,在电路图设计阶段,我们通常有四到五名团队成员同时并行工作。我们还确保在电气设计阶段增加说明,以便在布局开始时一切井然有序。通过使用 Xpedition,任何人都能获得他们需要的东西,这样他们就可以持续工作而不会遇到瓶颈。”

除了并行设计,Adcom 还在布局阶段使用元件布局组来节省时间。他们还发现草图布线有帮助,并预计在不久的将来会使用复用模块。

Adcom 对细节非常锱铢必较,不断检查彼此的工作以实现一次成功。例如,在元器件选型期间,团队成员会不断地咨询,来回往复,确保准确选择元器件,避免在设计过程中出现问题。

Adcom 首席运营官 Ruth Kastner 表示:“管理不断变化的行业并取得成功的关键是一流工程师与一流产品设计工具的结合——使用 Xpedition 对Adcom 来说非常合适。”

减少迭代并确保产品质量

Adcom 面临的另一个挑战是其设计的复杂性,涉及从多板和刚性-柔性到模拟和数字设计以及先进封装的各种技术,其产品使用 2 层至 20 层的电路板,尺寸从药丸胶囊大小到 120 x 60 cm都有。收发器包括对几毫伏电压敏感的千兆位和模拟信号。“当两个信号在同一块电路板上彼此相邻而电路板消耗超过 100A 的电压时,它们之间的平衡是一个挑战。”Frid 说。

Adcom 指出,Xpedition 仿真工具对Adcom 实现项目目标居功甚伟。

虽然 Adcom 没有在内部运行可制造性设计(DFM) 分析,但他们通过与专业制造商密切合作来弥补这一点。他们的制造商审查了 Adcom 选择的每个新元件,并同他们讨论了可能的问题和必要的准备工作,无论是使用特殊的脚位,设置距离和阻抗计算,选择要在板上使用的材料,还是确定这些材料之间的关系。

总结

利用 Xpedition 工具流程,Adcom 采用业界最佳的并行协作实践和“左移”式分析与验证,应对当今最复杂的 PCB 设计挑战,同时满足上市时间目标,为客户提供可靠的产品。

Adcom 凭什么脱颖而出?有一个集成的并行工具流,其包含所有需要的工具,从原理图和版图之间的交互显示,通过组布局和草图布线节省布局时间,到整个设计过程中的仿真。

获奖技术

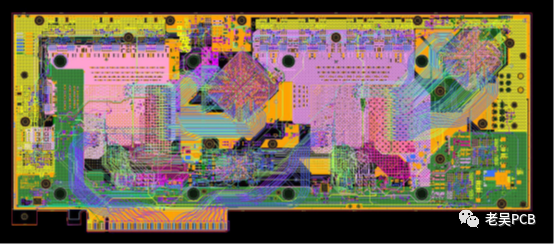

Adcom 荣获 Mentor 2017 技术领导奖,其基于 FPGA 的硬件加速卡 Neptune获得最佳计算机设计奖。

产品示例:Neptune,一种基于 FPGA 的硬件加速卡

评委会评论说,该产品提供整洁和高密度的布线、出色的 HDI 设计以及创新的散热器,其设计在同类产品中出类拔萃。

该卡是一种先进的高引脚数设计,必须在严格的设计约束下有效管理电源。整个卡有大量铜来输送电流,数据速率为每秒 480 GB,18 层设计需要全面的信号和电源完整性分析以及3D 电磁分析。

两个全新的 Xilinx®UltraScale FPGA 作为主要计算器件,两个 4Gb 混合存储器立方体通过 15Gbps 线路(总共 480Gbps)连接以提供服务,没有现成的规格或参考板可供研究。因此,该项目需要与Xilinx 设计团队紧密合作,以消除关于存储器立方体控制器的 FPGA 核心代码的难解问题。

在设计 Neptune 卡时,Adcom 面临如下重大挑战:

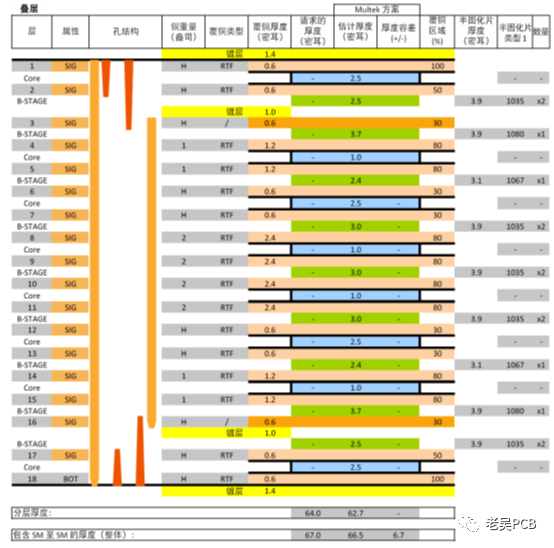

0.95V 供电轨上仅有 28mV 噪声容限,配电网的目标阻抗仅为0.28mΩ,约束非常严格。为确保产品可靠性,需要进行大量 3D 电磁 (EM)分析。团队使用 Mentor HyperLynx®工具设计了一种独特的电容布局策略。团队还利用四个嵌入式电容核心优化了堆叠。

满足 PCIe Gen3 要求:一条 16 位宽总线在两个 FPGA 上分叉。

18 层 PCIe 板的厚度约束

承载电流需要大量的铜,因此Adcom使用低介电常数的薄芯(3.00 DK,2.5mil 厚)。这使他们能够在关键线路上实现 50 和 100 欧姆的阻抗。

前三层使用 HDI 来布设大部分差分对,没有残留分支

与制造商密切合作以确保可制造性

ECAD/MCAD 协作对满足热要求至关重要

服务器机箱必须容纳 8 个相同的PCIe 卡,每个卡功耗为 300W

每天使用 MCAD 进行一次迭代,持

续两周以上,以使用热分析的反馈

来优化 3D 布局

复杂的叠层: