一根信号线上,通过电阻连接一个固定的高电平VCC,信号线初始、空闲时一直保持高电平状态,称为上拉电阻。

总线的上拉电阻各有不同作用,如I2C的上拉电阻是由I2C端口内部结构决定的,而RS485和CAN总线的上拉电阻是为了做终端匹配。那这不同总线的上拉电阻,是否接上拉,阻值的选择有何讲究吗?

是的,这些电阻阻值的选择都是有理论依据的,如果阻值选择不正确,会引起一些异常,例如曾经有一个案例,I2C上拉电阻阻值为10K,而应用却要求I2C跑400KHz的高速率,显然这样的上拉电阻不能满足400kHz的高速率要求,出现通信错误也是不可避免的了。

对于RS485和CAN总线而言,则需要根据现场情况进行灵活使用,就算节点数相同的两个应用,由于布线和所接设备的差异,需要的匹配电阻也是不同的。理论计算值可做为重要的参考依据。

I2C上拉电阻有什么作用、阻值如何确定?

I2C上拉电阻有什么作用、阻值如何确定?常说I2C需要加上拉电阻,却不知道为什么需要加上拉电阻?

第一是I2C本身的协议决定,空闲时两线均保持高电平状态,能够实现线“与”功能。

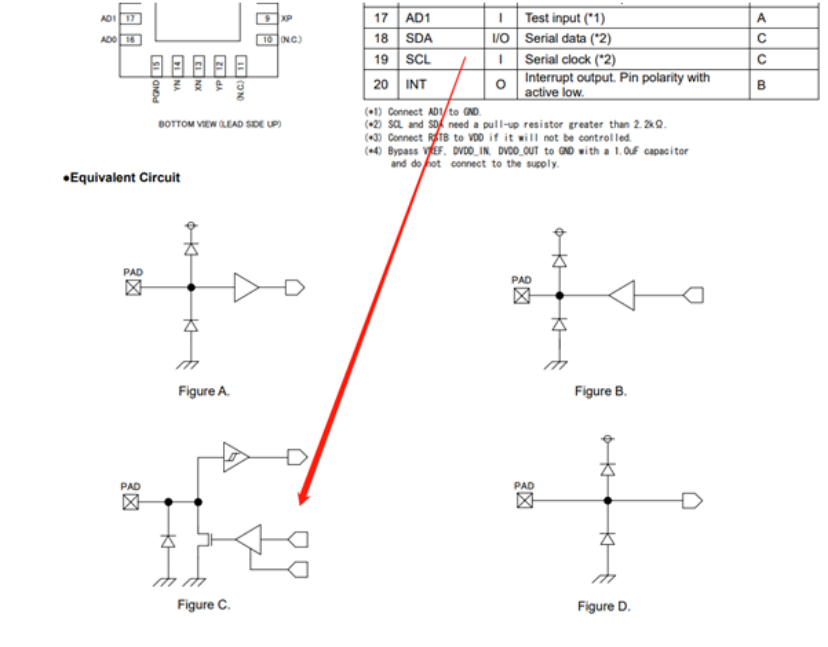

第二是器件内部结构,如图1所示,SCL和SDA引脚内部结构,内部无法提供高电平,只能依靠外部高电平。目前部分器件支持上拉功能的复用功能开漏模式,芯片内部可配置为上拉模式(建议使用外部上拉电阻)。

I2C上拉电阻的取值大小怎么确定?

考虑IO灌电流,阻值不能过小。通常在标准模式100Khz,灌电流不超过3mA,

VOL不超过0.4V,若上拉电阻至3.3V,上拉电阻阻值约大于1k。

代入Vdd = 3.3,Vol(max) = 0.4,Iol(max) = 3,得到Rmin = 966Ω。

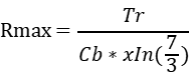

考虑上升时间,阻值不能过大。高电平是靠外部上拉电阻提供,电阻和总线电容组成RC网络,电阻过大充电时间过长,造成信号上升缓慢,未在规定时间内到达高电平,导致数据错误。针对I2C系统,在上拉电压的30%至70%时来测量上升时间和下降时间,总线电容100pF,总线最大上升时间300ns。

代入Tr = 300,Cb = 100,计算得到Rmax = 3.54kΩ。

根据以上计算,上拉电阻的取值在966~3.54k之间。工程实际设计中,并不是完全按照这个值来设计,通常可选取2.2k,3k,4.7k。

解决I2C通信问题,建议抓取I2C波形,观察总线上升/下降时间,并分析总线电容和上拉电阻等因素,并结合驱动代码全面分析。