以太网Link Down问题排查

以太网Link Down问题排查这个问题的故障现象是:设备在与电脑通信,开启自适应,速率千兆时,设备端使用iperf进行1000Mbit/s满载测试,偶发的调试串口会出现Link down打印,通信数据大量丢包,然后会马上link up,有时Link up成千兆,通信会恢复正常;有时会Link up成百兆或者十兆,通信会中断,ping包不通。手动输入 ifconfig eth0 down,ifconfig eth0 up后恢复正常ping包。

1. 电脑往设备发满载测试,并不会出现Link down的问题。

2. 设备往电脑发,当只是发100Mbit,即10%的负载时,也不会出现Link Down的问题。200Mbit时小概率复现。

3. 强制成100M全双工时,双向发送满载测试,不会出现Link Down的问题。

4. 测量25M晶振实际频率为24.99984M,尝试过飞线更换成25M有源晶振,问题还在。

5. 测量PHY芯片输出给MAC的125M时钟测量为125M,波形正常。

6. PHY芯片的0V/2.5V/3.3V供电纹波正常,均小于20mV。

7. RGMII_TXD的4根数据线,分别测试使用0Ω、22Ω电阻串联,增加7K上拉,无改善。

8. 飞线带变压器的RJ45测试,或使用长度较短的CAT6网线,均无改善。

9. 把PHY芯片配置的RGMII发送和接收时钟的Clock Skew都设置为0,通过MAC去调整,测试满载也是会down。

10. 使用示波器探头去点RGMII TX的数据线时,PING包会断。放开探针就可以恢复。

11. 飞线把RGMII的IO电平改为1.8V,可以解决这个问题。

12. 不使用底板的3V,使用数字电源来供电3.3V给底板,问题还在。

13. 把TXCLK、TXD0~3、TX_EN这6根线,从连接器出来断开,到PHY芯片也断开,直接飞线,不使用底板的走线,验证是可以解决这个问题。

14. 把串联的电阻改为焊锡直连,问题还在。

15. 只断开TXD3这根,再飞线,可以解决这个问题。

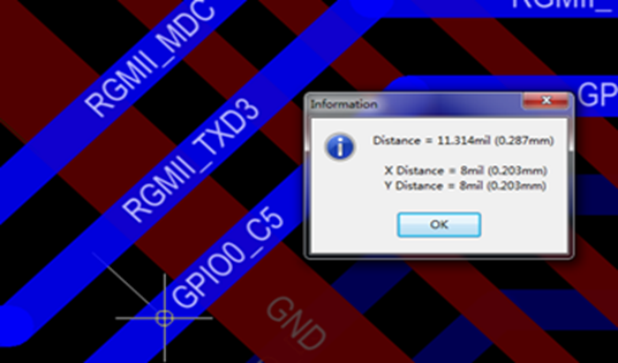

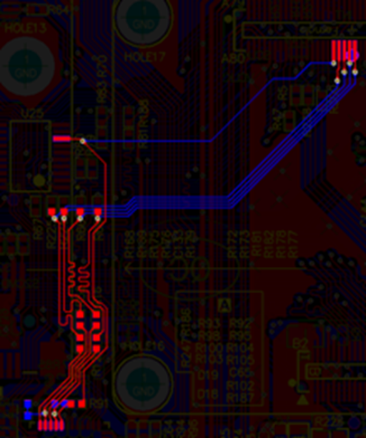

TXD3这根线的左右两边分别是MDC和PWM信号,跟TXD3的中间距离最小为12mil,线粗为5mil(参见图1),不满足3W规则。尝试割断左右这两根线并焊接飞线,也可以解决这问题。

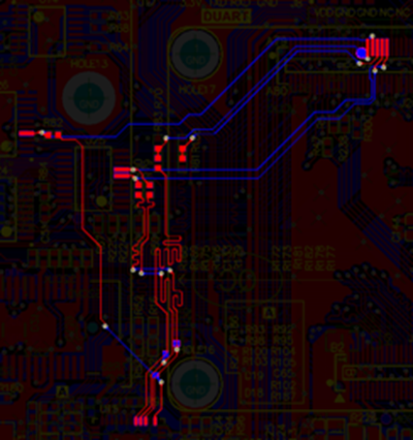

16. 检查PCB走线,RGMII和LCD是复用管脚,在PCB走线的时候,会有一点分叉存在(最长分叉为2mm左右),参见图2。

17. RGMII TX组走线长度:3010mil~3224mil,RGMII RX组走线长度:2403mil~2571mil(参见图3),单端阻抗整板为50欧。从等长来看,TXD3跟其它发送的数据线并没有严格等长,根据手册要求,TXD0~TXD3是需要按60mil以内的等长的,且总长度应在3000mil以内。

经过以上的一系列调试分析可推知,由于TXD3没有做好等长,终端电阻没有摆放在靠近源端,TXD3旁边有时钟线干扰,走线有分叉且总长度太长,多种因素叠加在一起,导致以太网测试满载时会down。

其他容易忽视的问题

其他容易忽视的问题复位时间不够导致网卡工作异常、MDIO信号反射导致网络卡死以及以太网Link Down问题都是典型的以太网常见故障,其中调试过程的经验方法值得借鉴,还有一些其他需要重视和警惕的问题,设计和调试时应当做排查重点:

以太网PHY到变压器这段的驱动分为电流型和电压型,设计时需要查看手册,确定变压器这边的中间抽头是要拉高还是接地。

PHY的设备地址PHYADDR通过上下拉电阻来实现。PHYADDR往往和LED管脚复用,设计时要注意如果PHYADDR是上拉,则该管脚为低电平有效,应该接到LED的负极;如果PHYADDR是下拉,则该管脚为高电平有效,应该接到LED的正极。

RMII不像RGMII和MII有一个TXCLK一个RXCLK,取而代之的是一个50MHz的REFCLK,这个时钟设计是要注意核对主控端和PHY端各自是作为输入还是输出,是否可配置,有些厂家的是可以通过软件配置的,有些却是固定的,需要在设计前确定REFCLK的方向。

最佳的以太网电磁兼容拓扑应为:PHY芯片共模电感/磁珠TVS管网络变压器气体放电管/放电齿RJ45。容易被忽视的是以太网POE,当连接了支持POE的交换机,以太网的信号线上会有最高57V的电压,即使产品不需要POE功能,也要注意器件的耐压值。