去年就买这本书了,我顺手就踹回来了,上面说了几个仪器,我觉得还挺综合,让我们在年末为来一次收官活动。

其次就是确实是不少高校的学术也是来陆陆续续的问相关课程里面的一些仪器设计,借此机会当作学习套件也不是不可以。资料给的很齐全,感觉用这个上课也不是不行,做毕设,做实验。

今天第一章先把里面前四章写了,基本元器件和基本电路以及一点杂项,我的理念是,书要越读越少。

这书是南方医科大学和深圳大学以及广东药科大学和深圳一个公司联合搞的。

但是电子世界庞杂无比,不是一本书就可以说完的,我想通过文章来做一些补充。

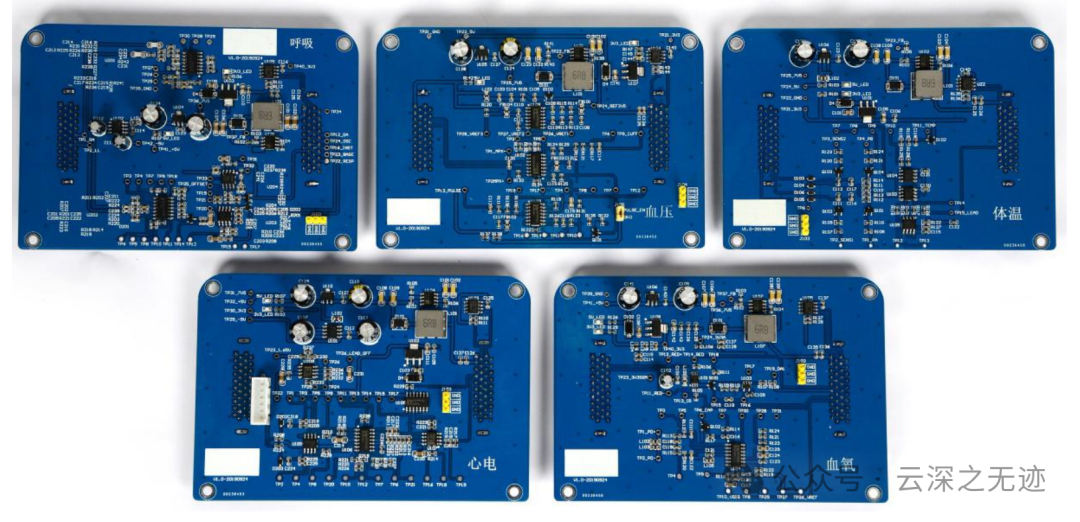

OK,就是这个了

实际上就是5个PCB

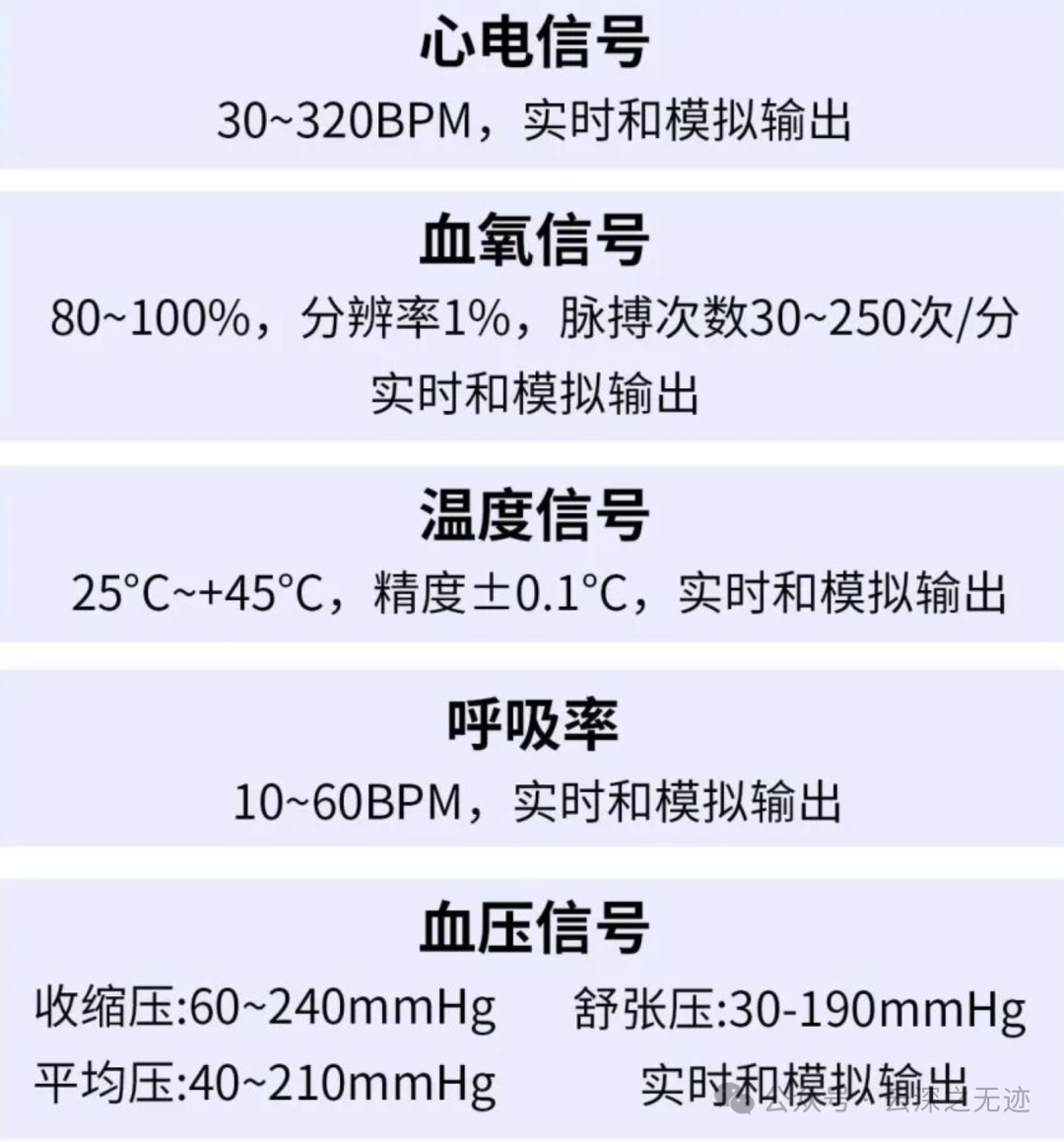

课程最后的仪器参数是这样的

这篇文章就以元器件入手,但是市面上讲元器件的也很多,所以我这里就做一些对书中内容的延拓。

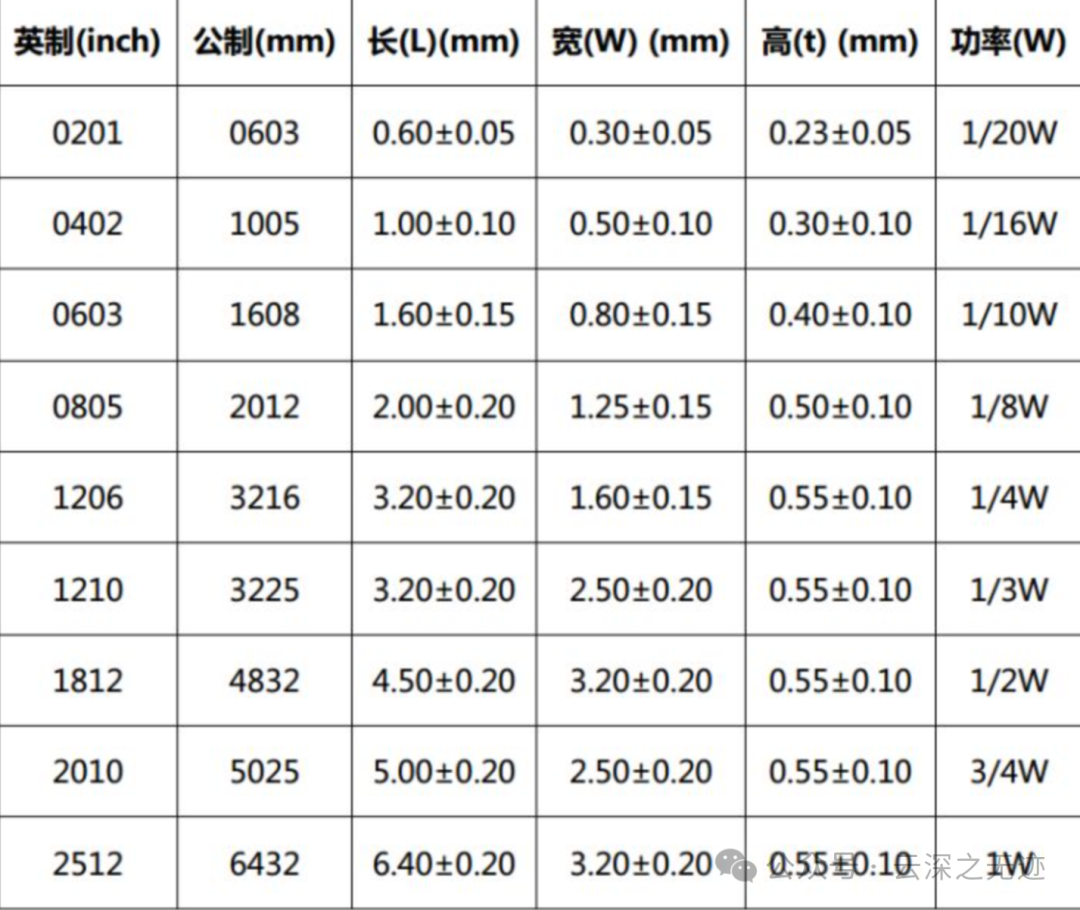

封装

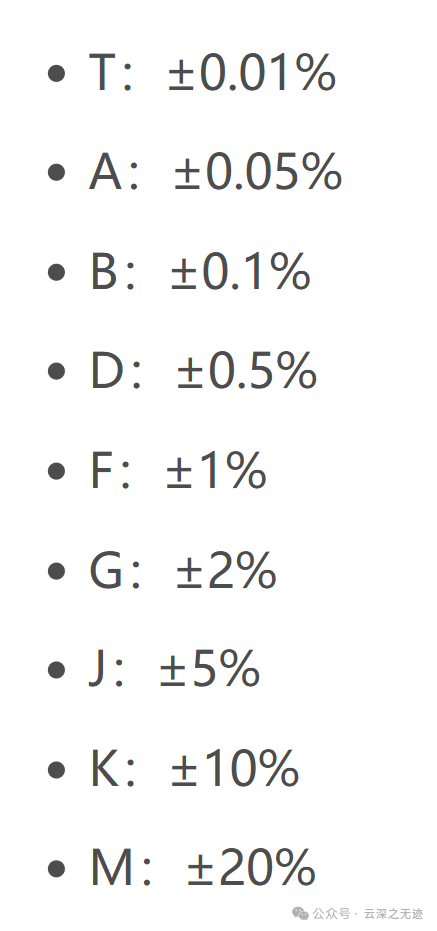

精度

一般我们使用的都是1%的电阻,太高精度的贵呢!不过做参考的电阻就要精度高:

精密=不便宜

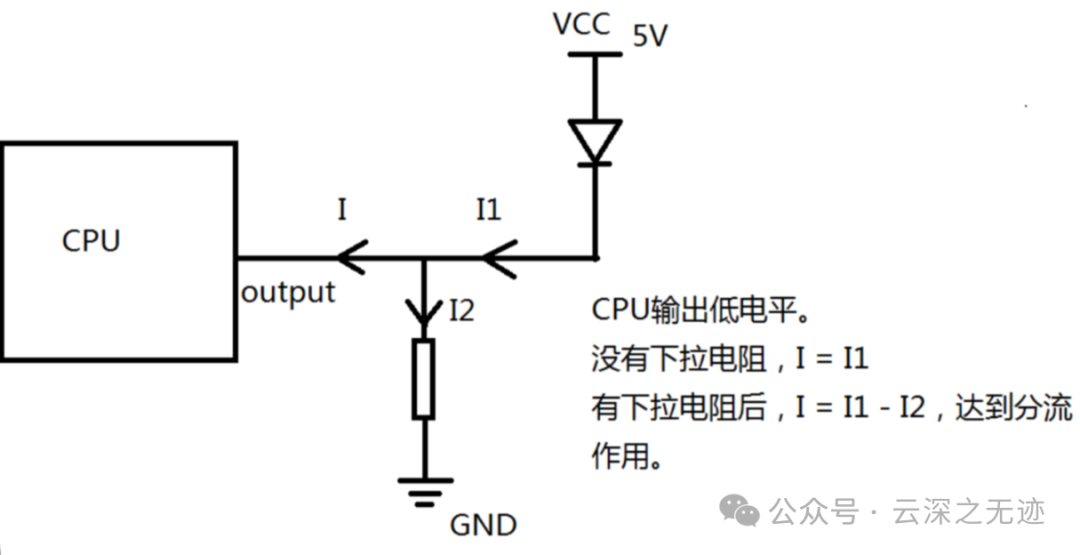

下拉

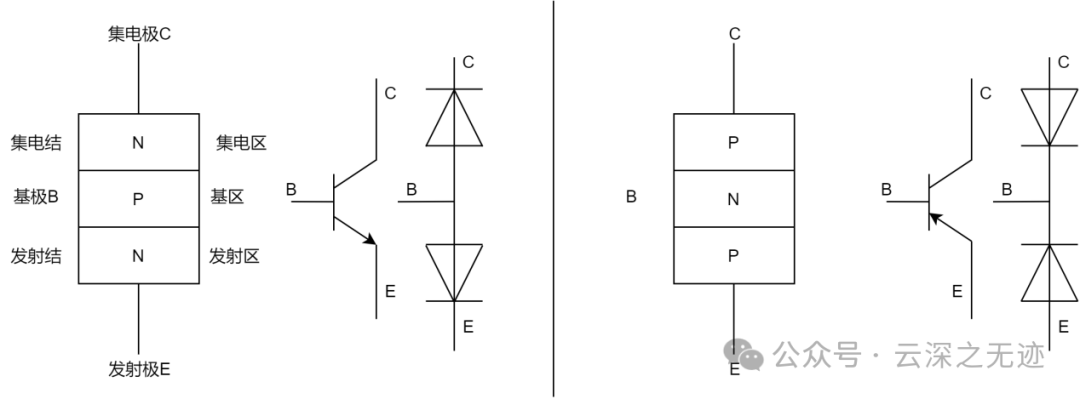

TTL(晶体管-晶体管逻辑):基于双极型晶体管的数字逻辑电路,具有较高的驱动能力,但功耗较大。

CMOS(互补金属氧化物半导体):基于MOSFET的数字逻辑电路,具有低功耗、高噪声免疫力等优点。

就是三极管和MOS管。

直接驱动: 在相同电源电压下(通常为5V),CMOS可以直接驱动TTL。这是因为CMOS的输出高电平通常高于TTL的输入高电平阈值,输出低电平通常低于TTL的输入低电平阈值。 虽然可以直接驱动,但需要注意CMOS的输出电流限制,避免损坏TTL器件。

不能直接驱动: CMOS的输出高电平通常达不到TTL的输入高电平阈值,因此不能直接驱动TTL。

需要上拉电阻: 在CMOS输出端接一个上拉电阻,当CMOS输出高电平时,上拉电阻将信号拉高到TTL能够识别的电平。

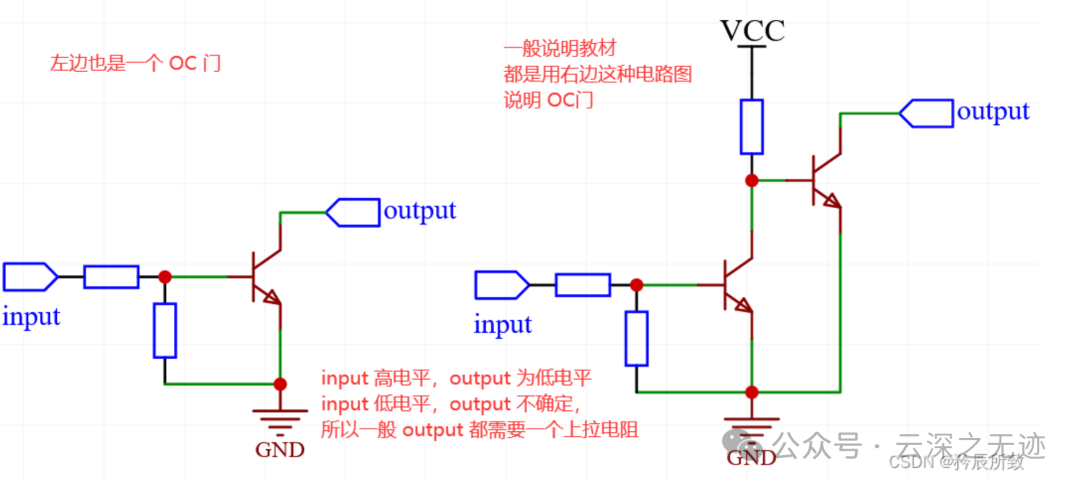

书里面还有说OC门电路,也写一下,是数字电路里面的内容,妈的,这么多内容。

因为 OC/OD 门电路不具备输出高电平的能力,所以在一般应用中,是需要外接上拉电阻的。

OC门电路,全称是开路集电极门电路(Open Collector Gate)。与传统的逻辑门电路不同,OC门电路的输出端不是直接连接到电源或地,而是通过一个外部上拉电阻连接到电源。

就是三极管里面最上面的脚:

C,没人管

我偷图

内部结构:与普通逻辑门电路相似,内部包含多个晶体管,用于实现逻辑运算。

输出端:输出端是一个开路,没有直接连接到电源或地。

外部上拉电阻:需要在输出端外接一个上拉电阻,将输出端连接到电源。

原理呢?就是实现了一个逻辑门的功能:

低电平输出:当OC门电路的输出为低电平时,内部晶体管导通,相当于将输出端短接到地,此时通过上拉电阻的电流很小,输出电压为低电平。

高电平输出:当OC门电路的输出为高电平时,内部晶体管截止,输出端相当于开路,此时通过上拉电阻的电流较大,输出电压为高电平。

我成为嘀嘀咕咕=低低高高

OD门:Open Drain,漏极开路门,和上面其实是一样的,只不过上面是针对三极管而言,OD们是针对场效应管而言,也很好理解,MOS管的 D 漏极开路的电路。

总结一下:

多个OC门电路可以并联:多个OC门电路的输出端可以并联在一起,共同驱动一个负载。当其中一个OC门电路输出为低电平时,整个输出端都为低电平。这个我还没有用过。

需要外部上拉电阻:OC门电路必须外接上拉电阻才能正常工作。上拉电阻的值会影响输出的高电平电压和驱动能力。就是C,集电极没有人管,所以要用上拉电阻确定这个不确定的状态。

输出电流有限:OC门电路的输出电流受到上拉电阻的限制。

抗干扰能力强:OC门电路的输出端开路,不容易受到外部干扰。

还有一个是阻抗匹配,这个不简单捏(我还没有研究):

高阻抗低频率传感器的工频干扰 我在去年写过这个,可以先看看

长线传输中,由于传输线的长度远大于信号波长,电磁波在传输线上传播时会产生反射,导致信号失真、衰减,甚至产生驻波,影响系统的稳定性。阻抗匹配就是为了解决这个问题而提出的。

特征阻抗: 每种传输线都有一个固定的特征阻抗,表示传输线单位长度的电感与电容的比值。

阻抗匹配: 当传输线的负载阻抗等于其特征阻抗时,传输线上的电磁波就不会产生反射,信号能够无损耗地传输到负载端。

源端匹配: 在信号源端串联一个电阻,使源端的等效阻抗等于传输线的特征阻抗。

负载端匹配: 在负载端并联一个电阻,使负载阻抗等于传输线的特征阻抗。

上面两个就是我们经常使用的方法了。

分布式匹配: 在传输线上分布地连接一些小的电阻或电容,使传输线的阻抗逐渐过渡到负载阻抗。这个我没有多见过

最后就是两个参数:

反射系数: 反射系数是衡量阻抗匹配程度的一个重要指标,反射系数越小,阻抗匹配越好。

驻波比: 驻波比是表征传输线上电压或电流波动的程度,驻波比越小,传输线上的信号质量越好。

等后面脑子里面有知识了,咱们都学学哈。

电阻还有分流和限流的作用:

先总结,后bb

将流经电路的总电流分成几路,使不同的元件分担不同的电流。通过分压作用,降低电路中某一部分的电压。

与电流表串联,通过测量分压电阻上的电压,间接测量电路中的电流。

负载保护: 将部分电流分流到分流电阻上,减轻负载的负担。

上面就分流了,限流主要是保护:

通过增加电路的总阻抗,降低电路中的电流,从而保护电路中的元件。

稳定电路: 限制电路中的突变电流,提高电路的稳定性。

这些都是小儿科,还有作用是偏置电阻:

电子电路中,特别是放大电路中,用来设定晶体管或运算放大器等有源器件工作点的一种电阻。

偏置电阻通过提供合适的偏置电流,将晶体管的工作点设置在放大区的中心,以获得最大的线性放大范围。

偏置电阻可以稳定晶体管的工作点,减小温度变化和电源电压波动对电路的影响。通过改变偏置电阻的值,可以改变晶体管的静态工作点,从而改变放大电路的放大倍数。

这里就不班门弄斧了,等我学会模拟电路就开始写杨建国老师的模拟书。

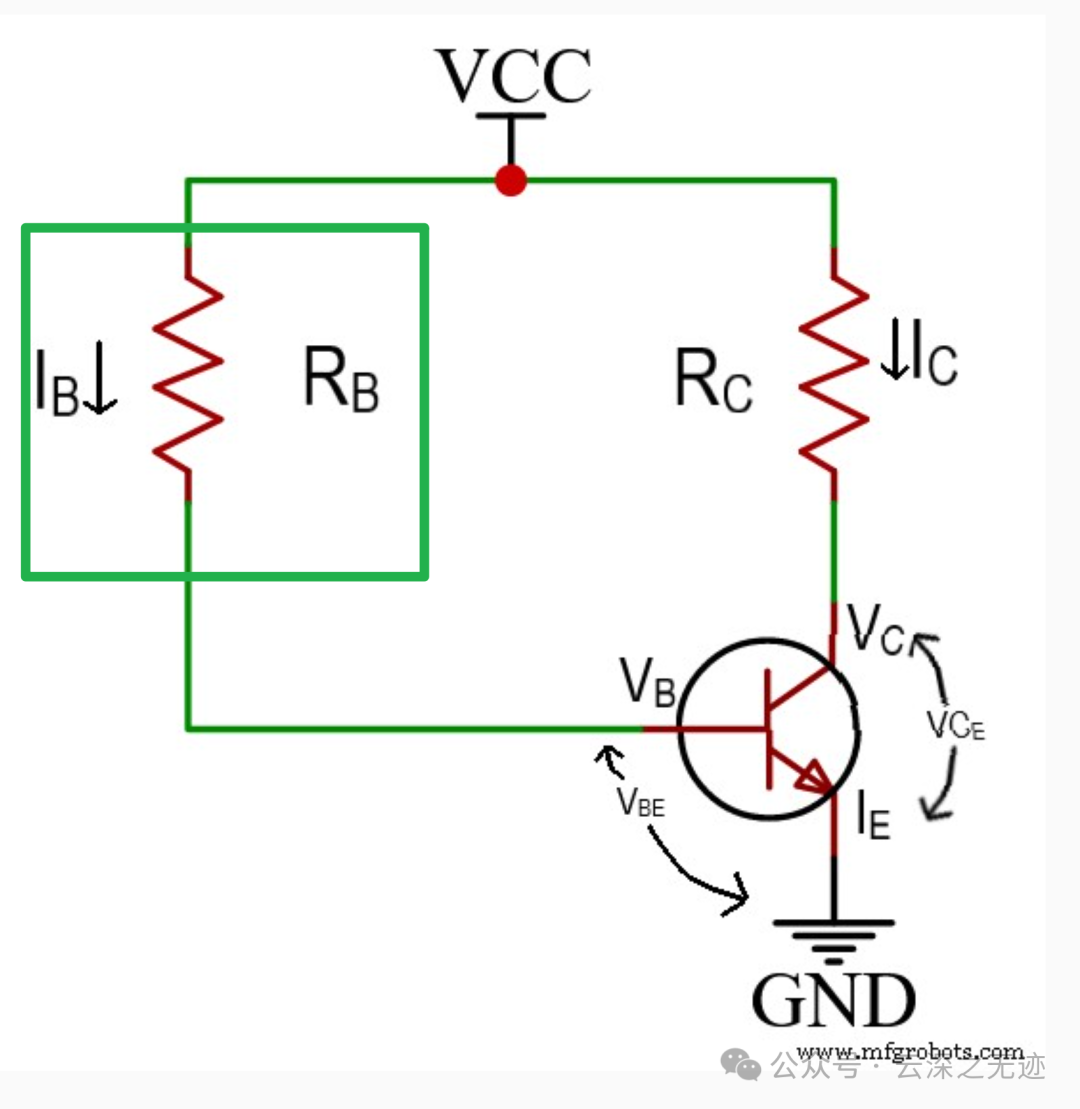

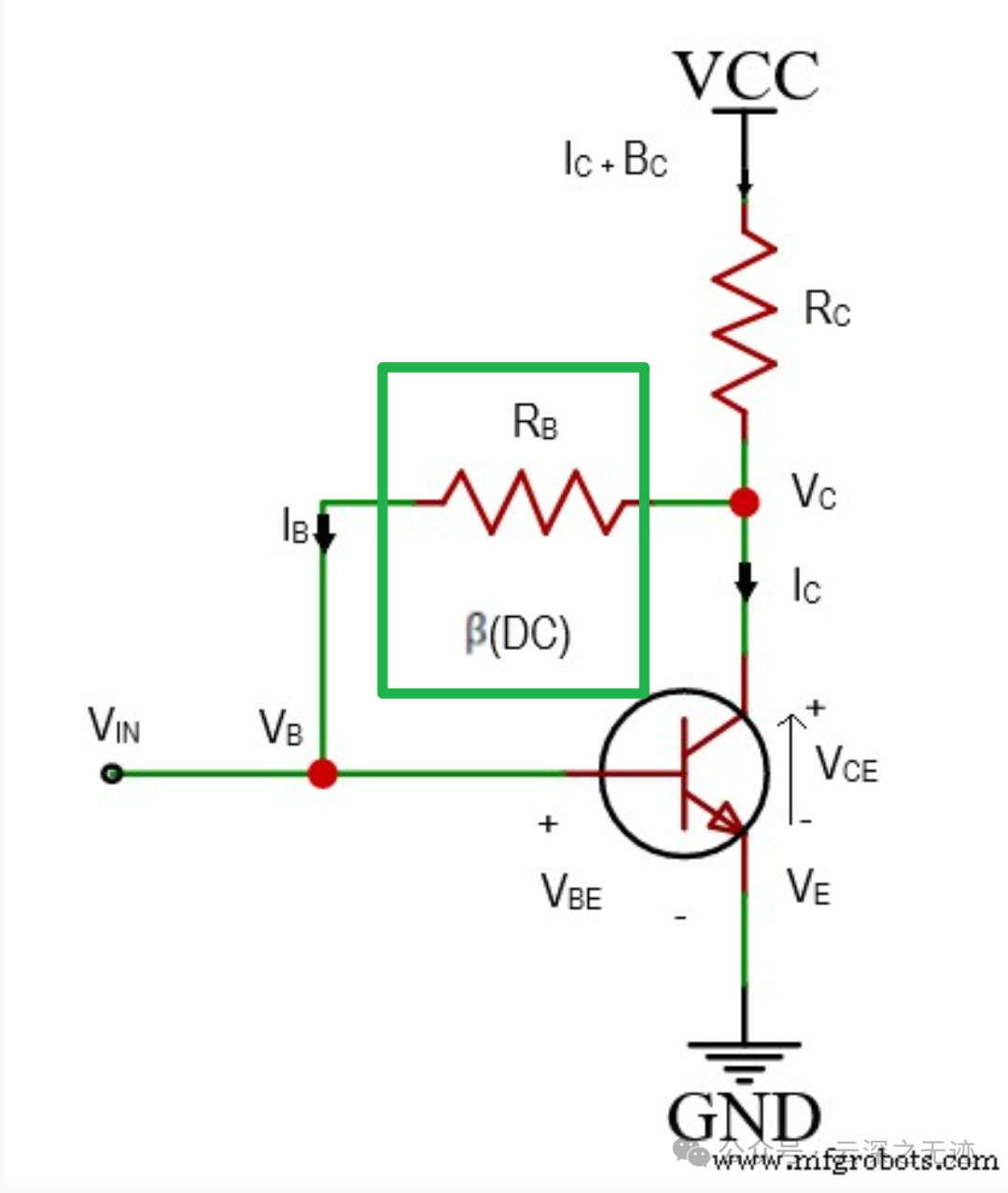

固定偏置电路是最简单的一种,但稳定性较差,容易受温度影响。

三极管的控制是BC的电压,然后E到C的电流就会线性变化,假如在线性区的话。

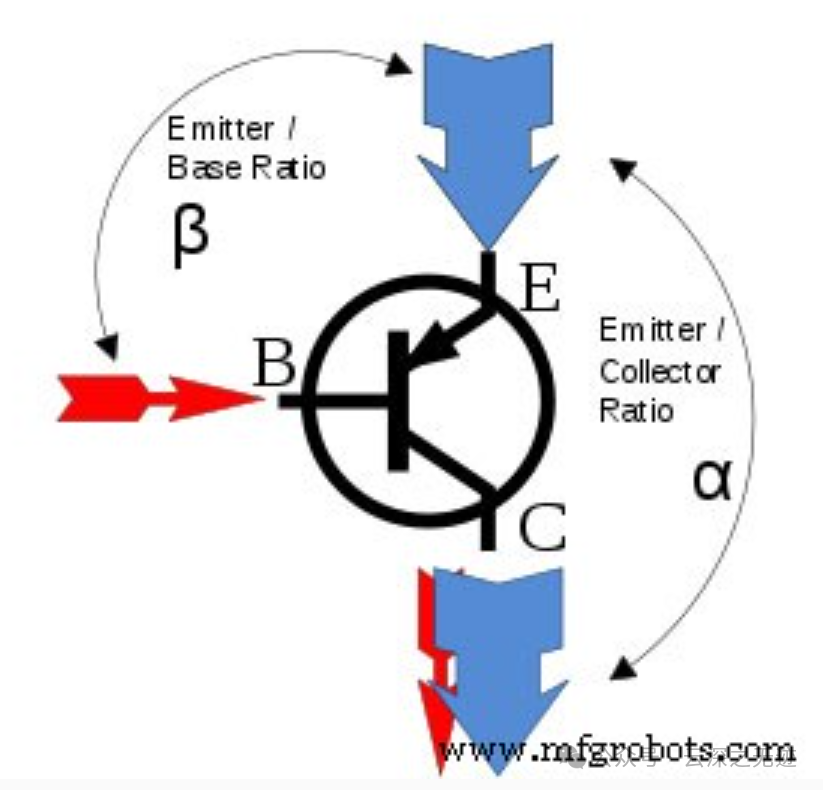

Beta (β) 是指器件在基极电流与其集电极放大水平之间的整体灵敏度。(什么呆逼翻译,就是放大倍数)

这个倍数就是这个Rb,就是偏执电阻的调节

在固定偏置型电路中,VCC 和 VBE 都具有固定值。

同时,RB 保持不变。因此,IB 也会有一个连续的值,导致一个有限的操作点。因此,这种偏置类型由于其 β+1 稳定性因子而提供较差的热稳定性。

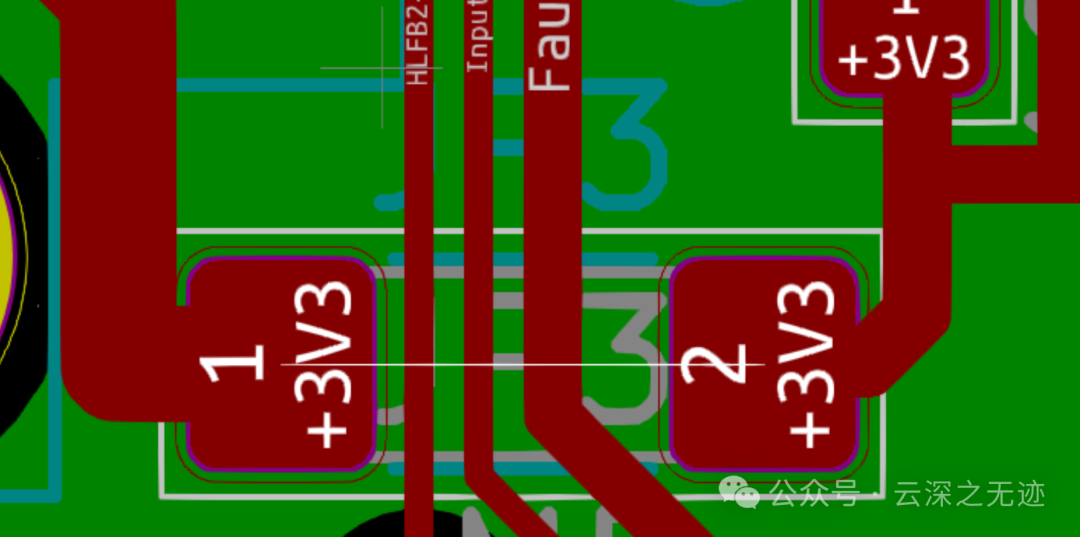

在多层PCB板中,过孔可以连接不同层的地平面。在高频电路中,磁珠可以抑制高频噪声,同时起到单点接地的作用。

短路是什么?短路是指电路中出现了低阻抗的通路,导致电流过大,可能损坏电路元件。

开路是什么?开路是指电路中出现了断路,电流无法流通。

数字电路产生的高频噪声可以通过地平面耦合到模拟电路,导致干扰。分割地平面可以有效地隔离不同功能模块之间的噪声,提高电路的抗干扰能力。

当电路中有大电流涌入或涌出时,地平面上的电压会发生波动,这种现象称为地弹。分割地平面可以减小地弹对敏感电路的影响。分割地平面可以改善电源分布,减少电源噪声,提高电源完整性。

物理分割: 在PCB上用切割线将地平面分割成多个区域。

电气隔离: 使用电容或磁珠等元件将分割的区域连接起来,形成电气隔离。

分割的位置应根据电路的功能和噪声源进行合理选择。一般来说,数字电路和模拟电路之间、高频电路和低频电路之间可以考虑分割。物以类聚,人以群分。

分割后的地平面之间需要通过适当的连接方式来保证地电位的一致性。记住电子系统是个环路,不能有分割。

分割后的地平面面积应足够大,以保证良好的接地性能。分割地平面时,应尽量减小地线环路的面积,以减少辐射和耦合。

电容我推荐这本书,写的是真好啊

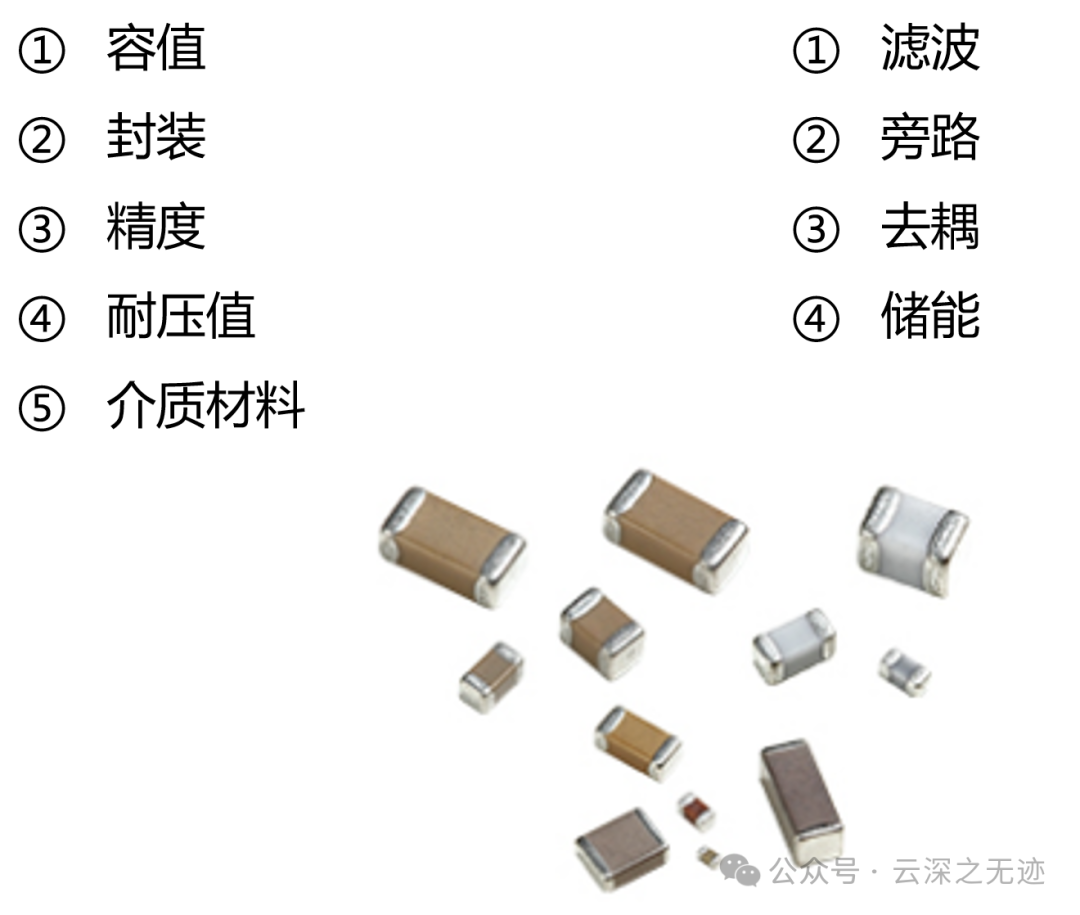

在电路中多使用电容其实是会提高电路的稳定性,以及它更多是要和电阻配合做为滤波电路出现。

这里就需要多看看数据手册了

白色是正极

建议大家多去看村田的东西,写的好好,他们的美工组加鸡腿

这是电感

是不是很可爱

这种也是

可爱

这也是

继续看

这个像方糖

这里也推荐看海老师的书,不知道为啥有电子版了

http://m.aychina.net/fhdg/37-170.htmlhttps://list.szlcsc.com/catalog/337.htmlhttps://zh.mfgrobots.com/mfg/it/1005029749.htmlhttps://forum.kicad.info/t/would-it-be-possible-to-detect-0-ohm-resistor-as-a-connection-in-drc-and-ratsnest/20145https://bbs.huaweicloud.com/blogs/378008配套资料下载pan.baidu.com/s/1Kn9zvXgO1tq2CNjaPCks9A提取码:tyz3解压密码:123456