近日,微电子所高频高压中心刘新宇研究员团队与青禾晶元公司、南京电子器件研究所等团队合作,基于新型6英寸SiC复合衬底成功实现高性能低成本1200V SiC MOSFET。

当前,碳化硅(SiC)晶圆行业正持续扩大产能以满足不断增长的市场需求。但可用于MOSFET制造的无缺陷衬底(即“高质量”衬底)的成品率通常仅为40%-60%。在6-8英寸SiC的生长和提纯过程中,自然会产生低等级衬底(即“低质量”衬底)。在目前的工业生产中,这些衬底通常被作为陪片甚至废料处理,导致高质量SiC衬底的生产成本很高,通常占最终MOSFET器件成本的50%以上。此外,SiC衬底的制造过程耗能较高,导致较高的碳排放。

国际上首次提出

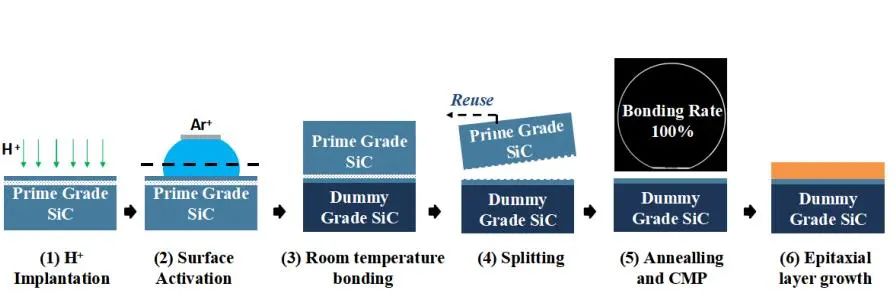

为应对这一挑战,微电子所与合作单位在国际上首次提出了一种新型6英寸单晶SiC复合衬底,通过表面活化键合技术和离子注入剥离技术,将高质量SiC薄层键合转移到低质量单晶SiC衬底上,实现了低质量单晶SiC衬底有效使用,每个高质量SiC晶圆可重复使用超过30次(即每个高质量晶圆可以产生超过30个薄层),预计成本降低40%。

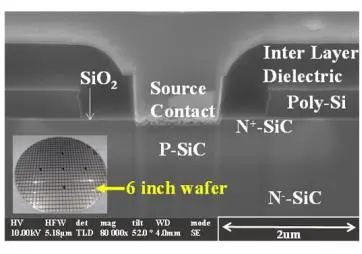

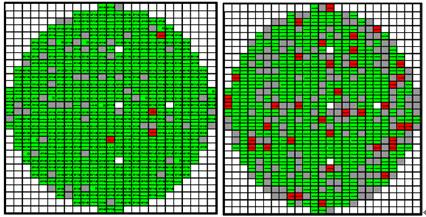

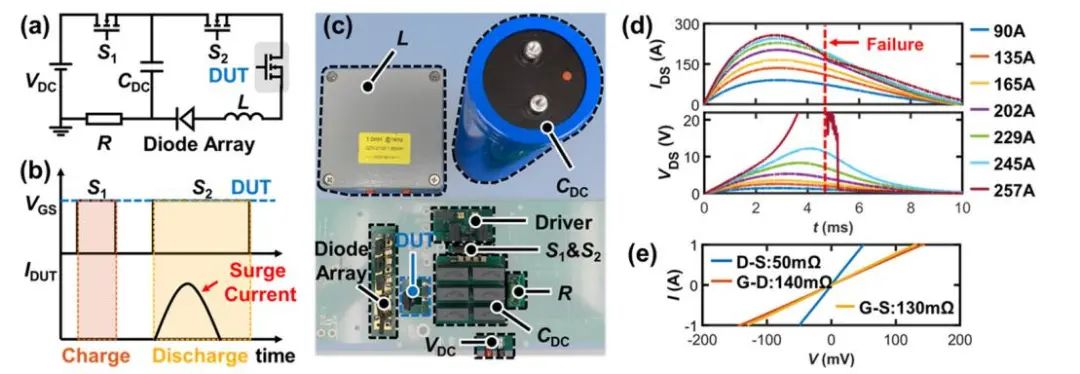

该复合衬底表现出与高质量衬底相当的缺陷密度,界面热阻低至2.8+1.4/-0.7 m²K/GW,且键合界面处电场强度很小。此界面热阻是目前国际上报道的SiC与其他材料(如SiC、GaN和Ga2O3)键合界面中最低值。在该衬底上生长的6英寸SiC外延层实现了高达99.2%的无致命缺陷良率。基于此6英寸外延层制造的1200V、20mΩ的SiC MOSFET器件展示了超过70%的良率(在IDSS<2µA,在1200V条件下测试),其性能和可靠性可同最先进的商用器件相媲美。电路鲁棒性测试显示,在超过250A、持续10ms的浪涌电流下,键合界面没有出现退化现象。该成果是首次报道基于SiC复合衬底的晶圆级器件数据及高电流鲁棒性。结果表明,这项新的衬底技术具有巨大的潜力,为更加经济和可持续的SiC功率电子器件提供了重要的发展方向。

基于该研究成果的论文“Cost-Effective 1200 V SiC MOSFETs on a Novel 150 mm SiC Engineered Substrate with Dummy Grade Material Reuse”,于12月10日以口头报告形式发表在第70届国际电子器件大会上(IEDM 2024)。微电子所王鑫华研究员为第一作者,微电子所刘新宇研究员、青禾晶元公司母凤文研究员、弗吉尼亚理工大学(现香港大学)张宇昊教授为论文共同通讯作者。

图1. 6英寸SiC-SiC键合制造过程的主要步骤

图2. 在6英寸工程衬底和外延层上制造的SiC MOSFET沟道区域的横截面高分辨率透射电子显微镜(HRTEM)图像

图3 在VGS= -4V和在VDS=1200V条件下的6英寸晶圆上制作的器件的IGSS分布图

(绿色为通过,图a良率为90%,图b良率为70%)

图4 浪涌电路测试图。(a) 为电路原理图,(b) 为理想波形,(c) 为浪涌电流测试装置照片,(d) 为被测件在不同浪涌电流水平下的电流和电压波形,(e) 失效被测件的引脚间电阻

免责声明 | 部分素材源自中国科学院微电子研究所及网络公开信息,版权归原作者所有。本平台发布仅为了传达一种不同观点,不代表对该观点赞同或支持。如涉侵权,请联系我们处理。