今日碎碎念

寻人,买过这个专辑的,加我微信退款啊,这个继续吆喝。

最近懵懵懂懂,总算把简单运放设计的流程,走了一遍。

对软件还是属于那种模模糊糊,并且有点怕怕的状态。

和当年刚入门ADS的时候,状态差不多。

当年刚开始在学校,用ADS做老师布置的项目的时候,做完了也还是感觉懵懵懂懂的,就如现在这样。

不过后来,接触多了,一回生二回熟,就慢慢好了。虽说也还是只接触了ADS里面的一小部分内容,但是遇到不会的内容,不会像刚开始那样,有畏难的情绪。

所以,继续加油~

动动手指,关注公众号并加星标哦

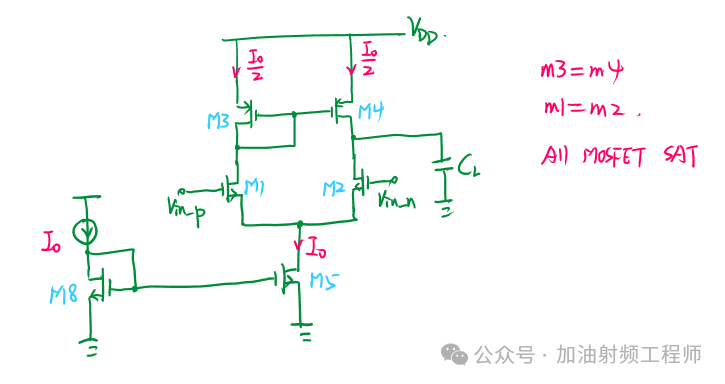

1 单级运放的设计

VDD=1.8VAv≥100(40dB),单级运放可能达不到这个值CL=10pF=1.6V=0.8V=5V/usecPower<3mWProduct>5MHz

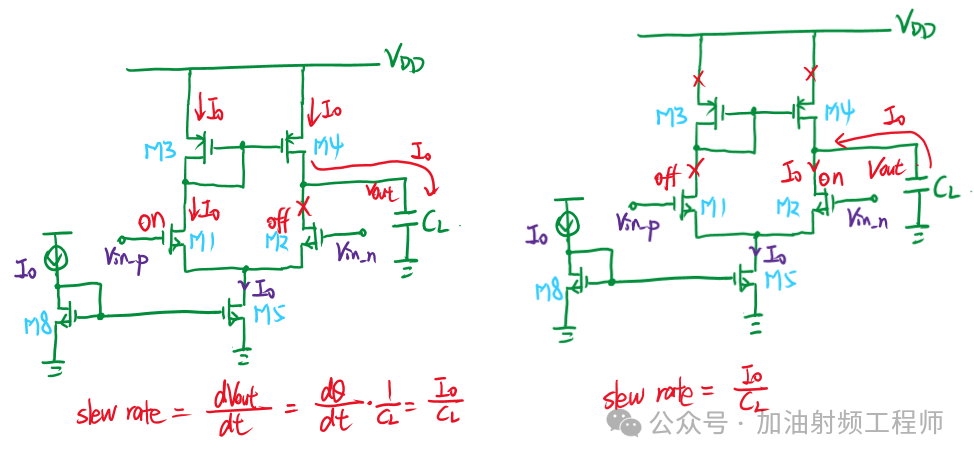

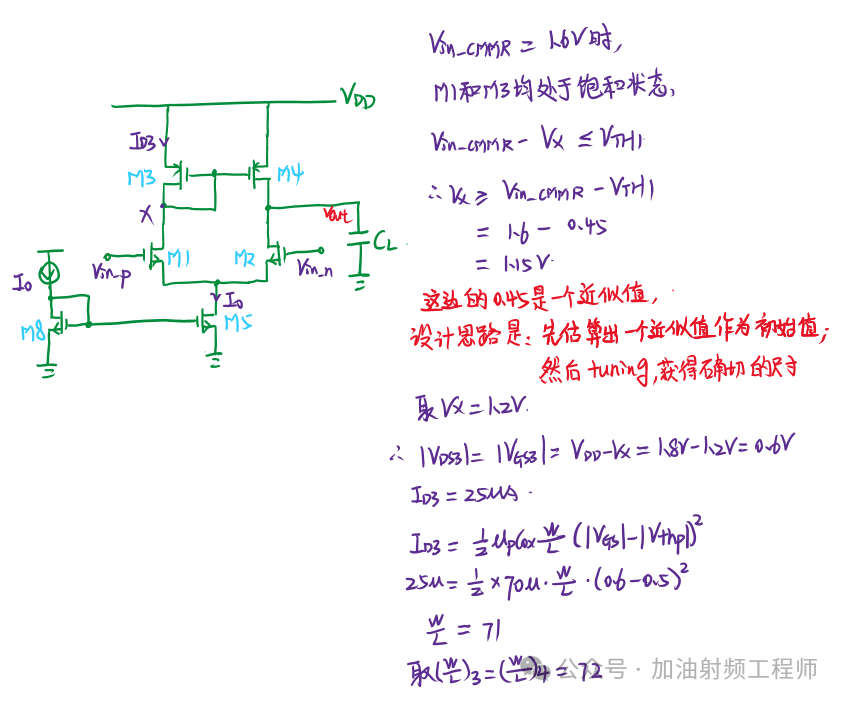

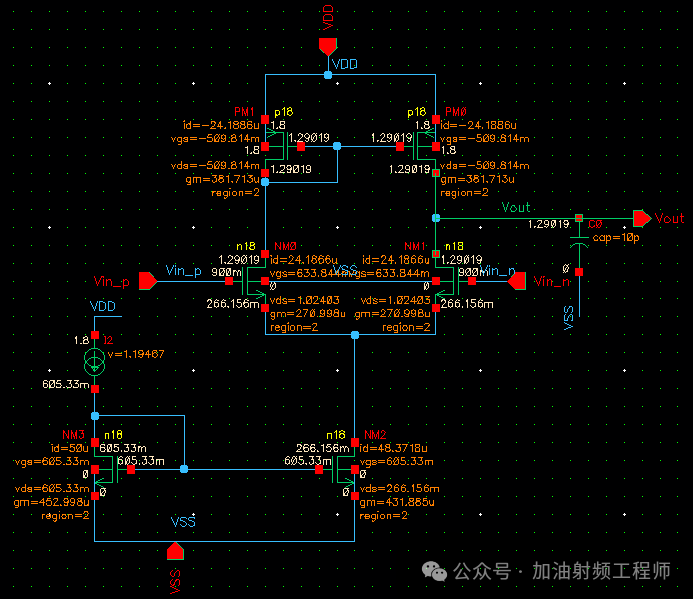

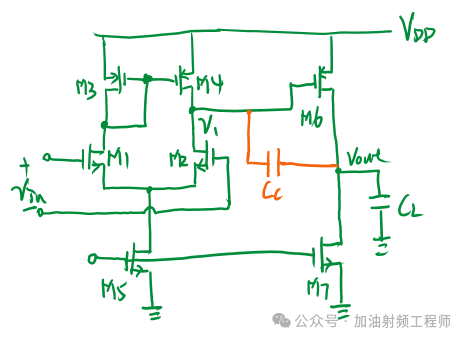

图 1 单级运放的架构

单级运放采用图 1所示架构。

在设计运放之前,需要了解的是,上面的所有的管子,都需要工作在饱和区。

同时,指标与各管子参数之间的关系是:

Slew rate由I0来决定M3,m4由maximum input common mode range来决定M1,m2由gain bandwidth product来决定M5由minimum input common mode range来决定M8由I0和m5来决定

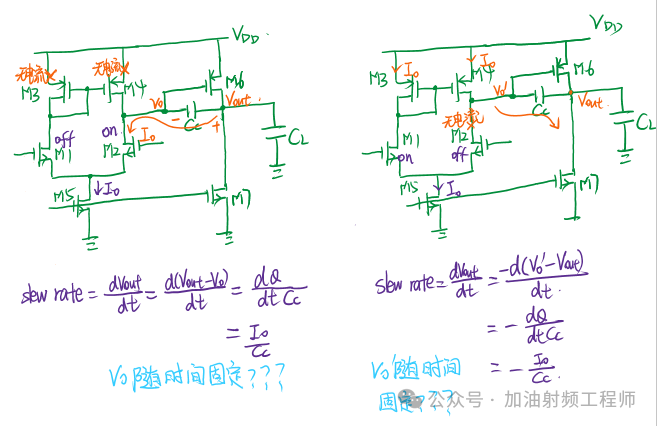

Slew rate(压摆率)是输出电压随时间变化的最大值,一般考虑slew rate的时候,一个通路是off,一个通路是on。On的那个支路,会sink或者source所有的电流,即I0,如图 2所示。

图 2 单级运放Slew rate的推算演示图

因为slew rate=5V/us,CL=10pF,所以I0=CL*slew rate=10p*5V/us=50uA。

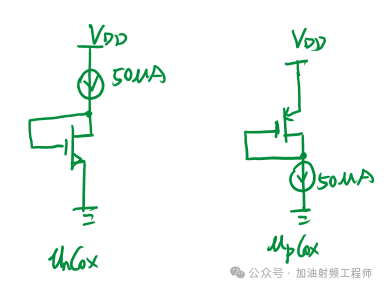

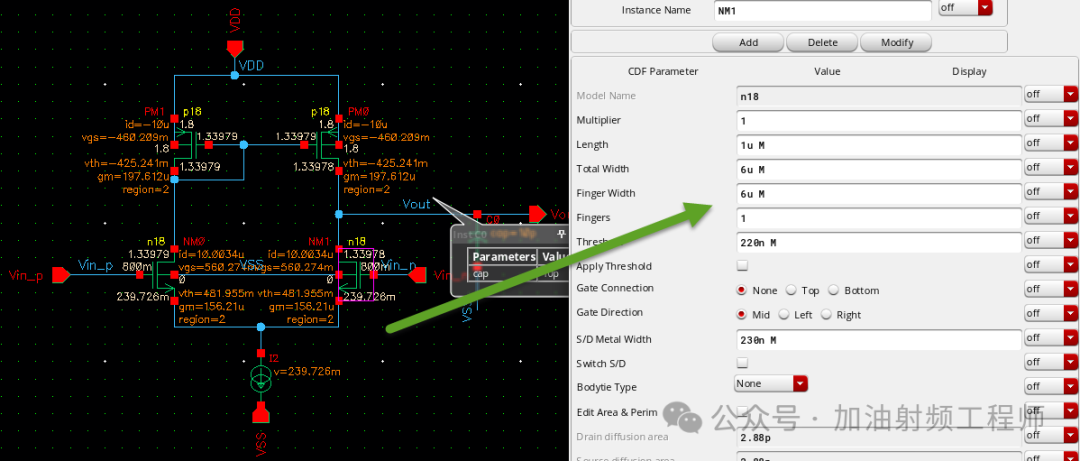

在估算M3/M4的尺寸的时候,需要知道unCox和upCox,以及Vthp,Vthn。可以通过在virtuoso软件搭建如图 3所示的电路图,然后仿真,得到上述值。

图 3 在virtuoso搭建电路的原理图

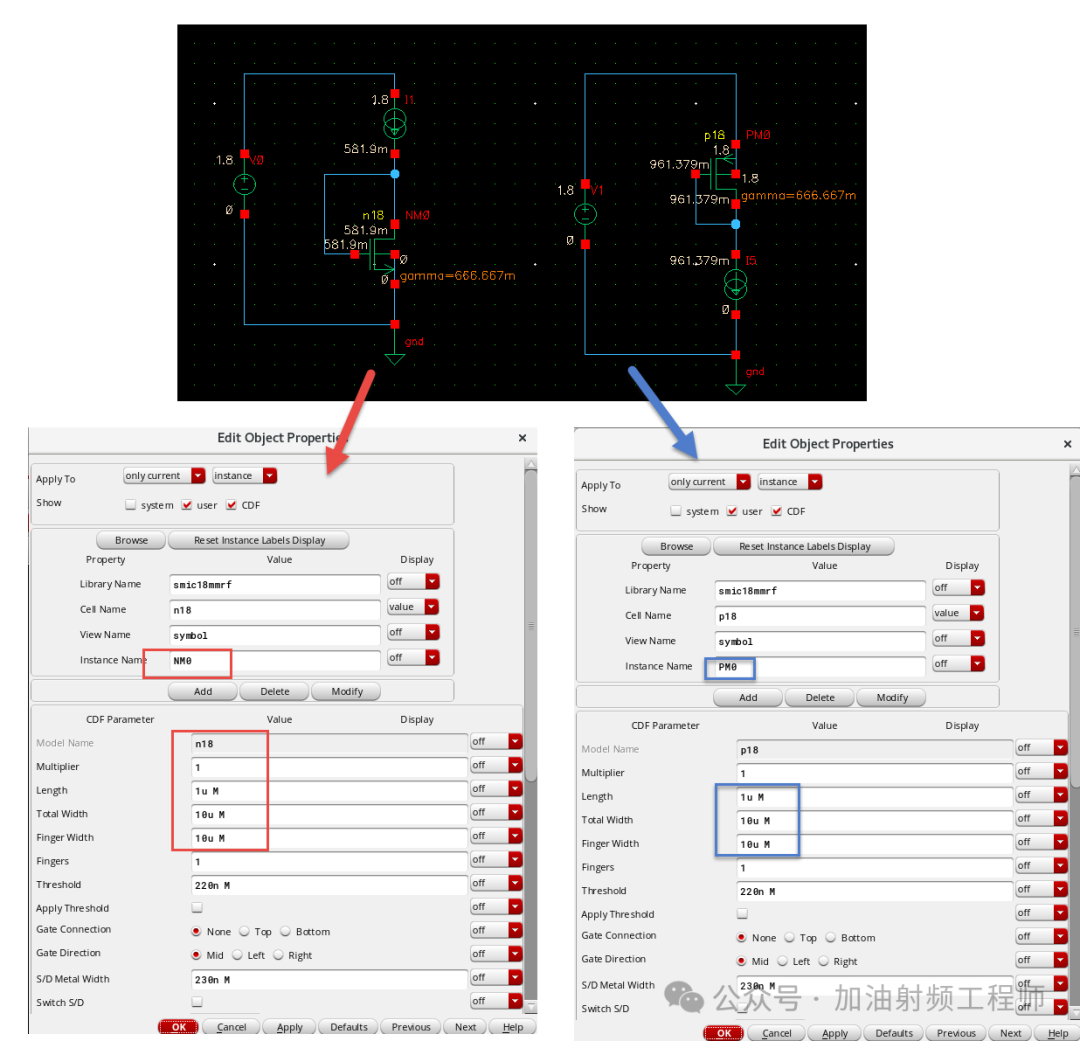

同时,为了减少沟道调制效应的影响,虽然使用的工艺Lmin=180nm,但是仍然选择L=1um。具体仿真图,如图 4所示。

图 4 获取uncox,upcox等参数的virtuoso软件中的设置

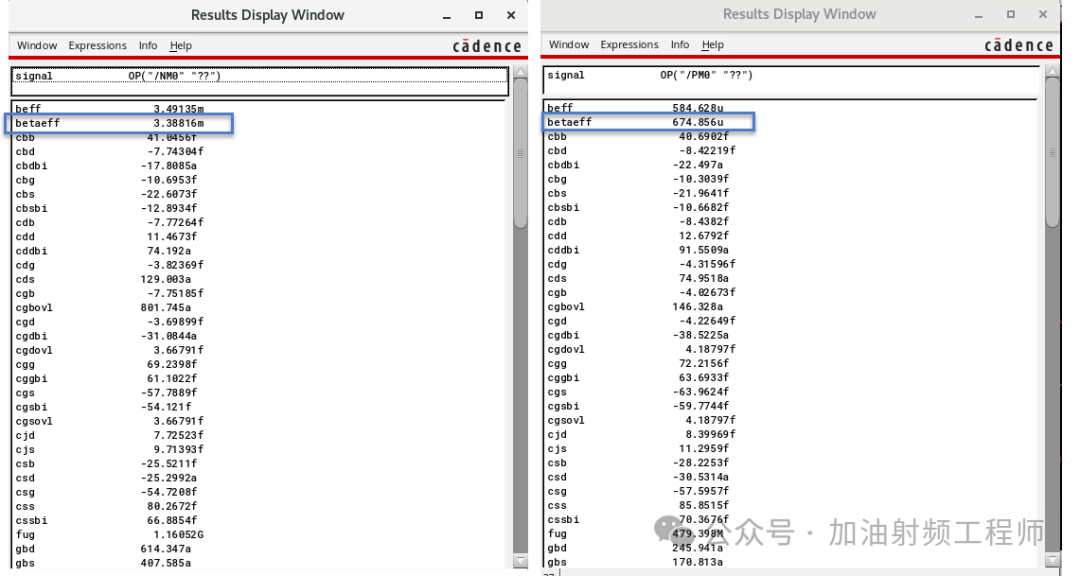

查看DC operating point,并点击管子,就可以得到管子的参数,如图 5所示。

图 5 管子的直流参数

从仿真结果可知,PMOS的betaeff=674.856u,取betaeff=700u=upCox(W/L)。因为在软件中,W/L设置的是10,所以upCox=70u。

同样的,NMOS的betaeff=3.388m,取betaeff=3.388m=unCox(W/L),因为软件中,设置W/L=10,所以可以取unCox=350u。

在进行前期设计的时候,可以取upCox=70u, unCox=350u。虽然这两个是近似值,但是作为初值计算是足够的。然后再打开上面的参数表,确认region=2,即管子处于饱和区。

同时记录下Vthp=-425.038mV和Vthn=412.644mV,m1和m2的Vth会比上面仿真的大一点,因为在上面的运放原理图中,sub接地,source没有接地,所以sub和source之间会又一个电压差,即有body effect。

在初值估算的时候,还是取和仿真值差不多的值,即:Vthp=0.5V,Vthn=0.45V。

不过在进行两级运放设计的时候,用的是接近实际电路的原理图进行的仿真,后续可以更新。

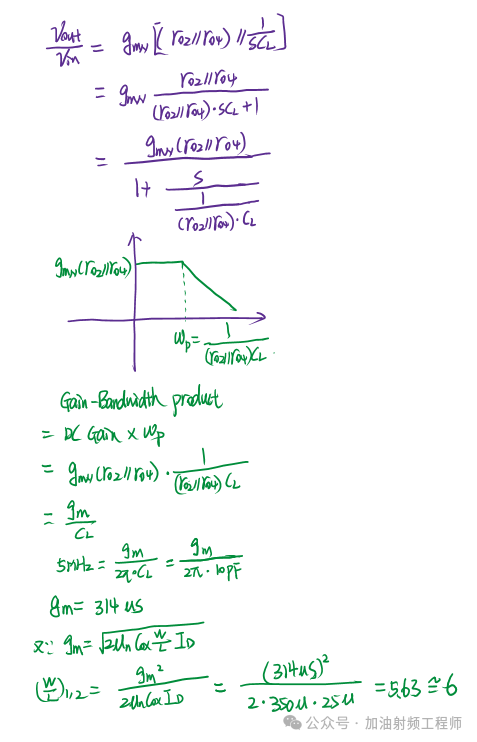

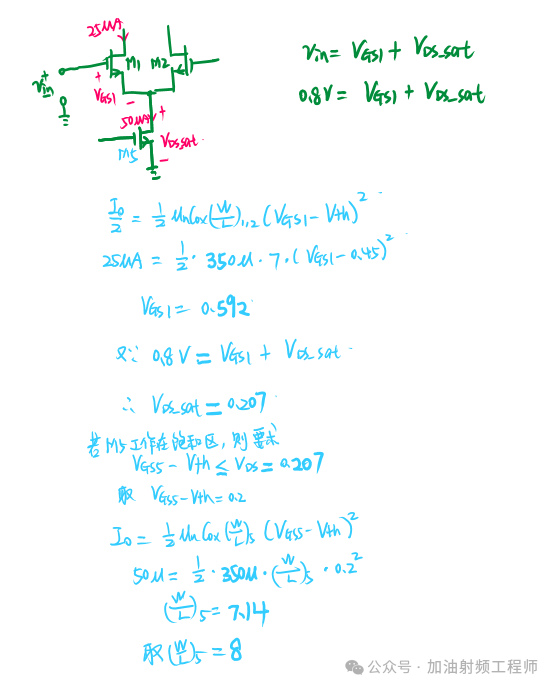

图 1所示架构所示的电路,传输函数如图 6所示:

图 6由Gain Bandwidth product推导出M1/M2的尺寸

由minimum input common mode range来决定M5的尺寸

M5由minimum input common mode range推导得到。

经过上面的推导计算后,可以得到各个管子的尺寸:

(W/L)3,4=72;

(W/L)1,2=6;

(W/L)5,8=8.

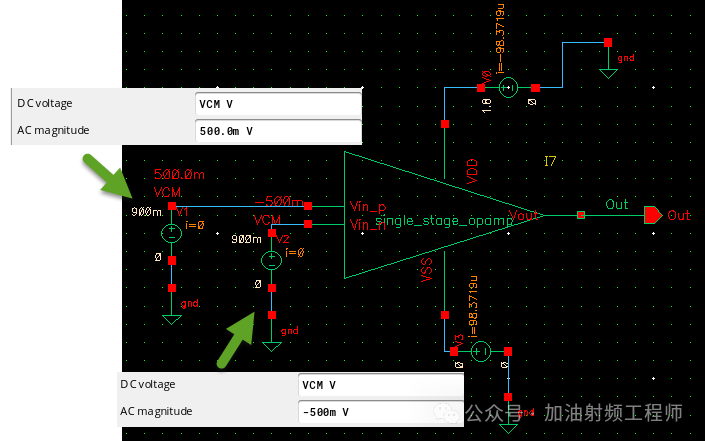

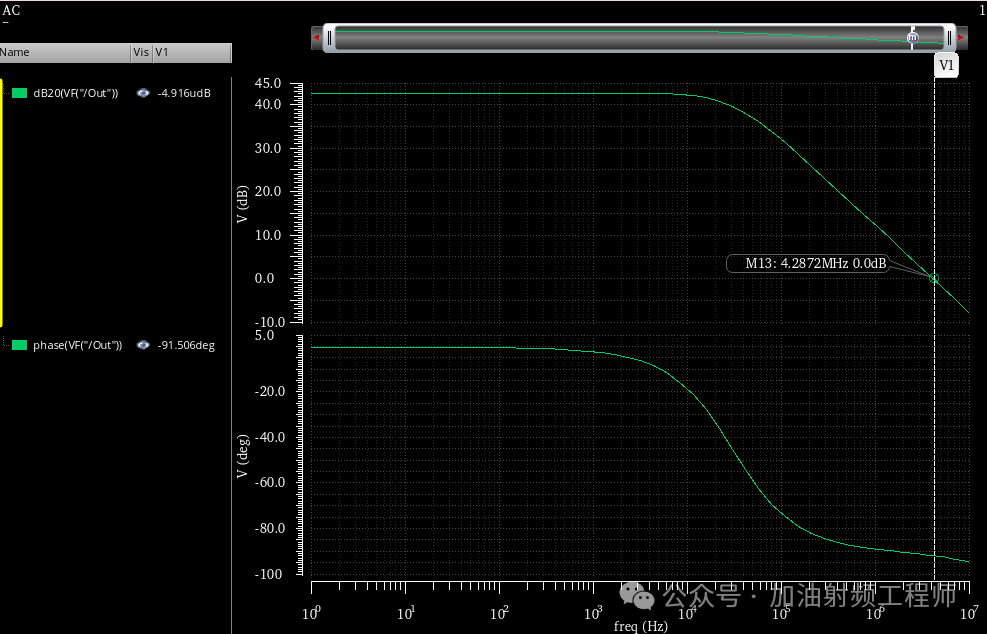

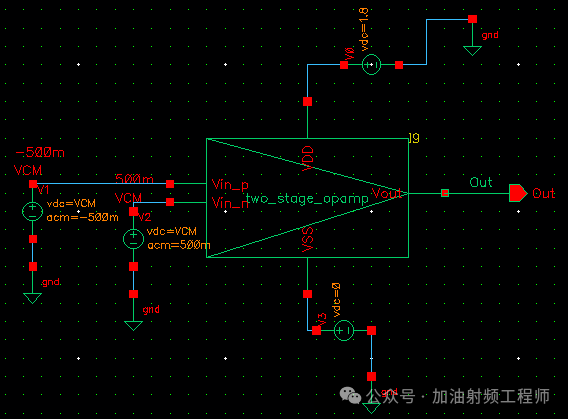

AC仿真时,设置两个信号源的直流电压为900mV,AC电压分别为500mV和-500mV。AC仿真的时候,主要由直流电压来决定直流工作点,并且AC电压的大小,不会影响该直流工作点。

这边选±500mV,是让Vin_pos-Vin_neg=1V,这样输出信号的幅度和大小,即是整个环路的幅度和大小。

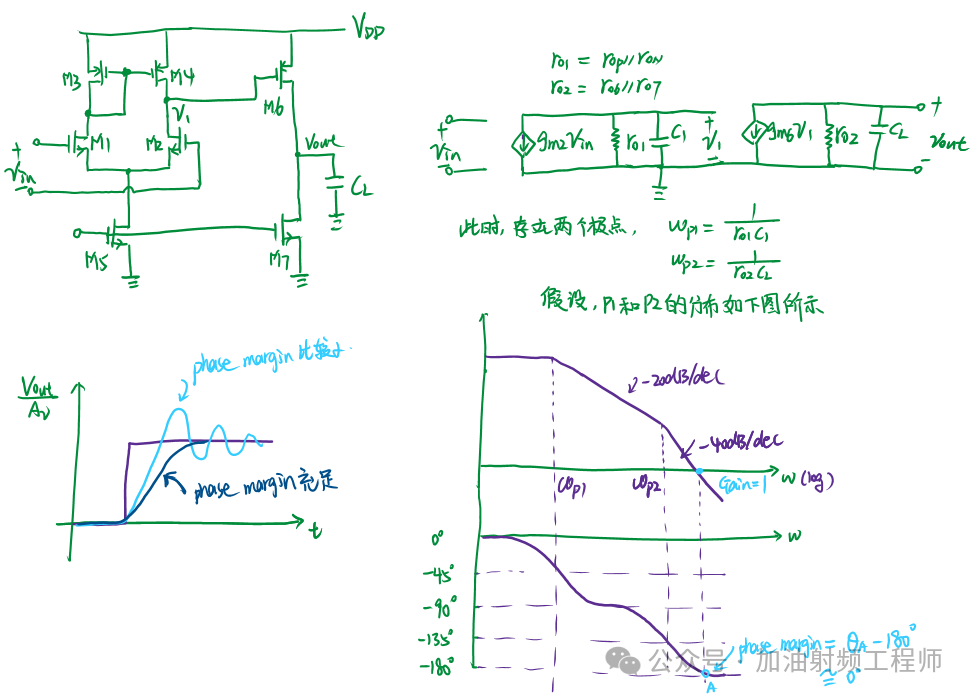

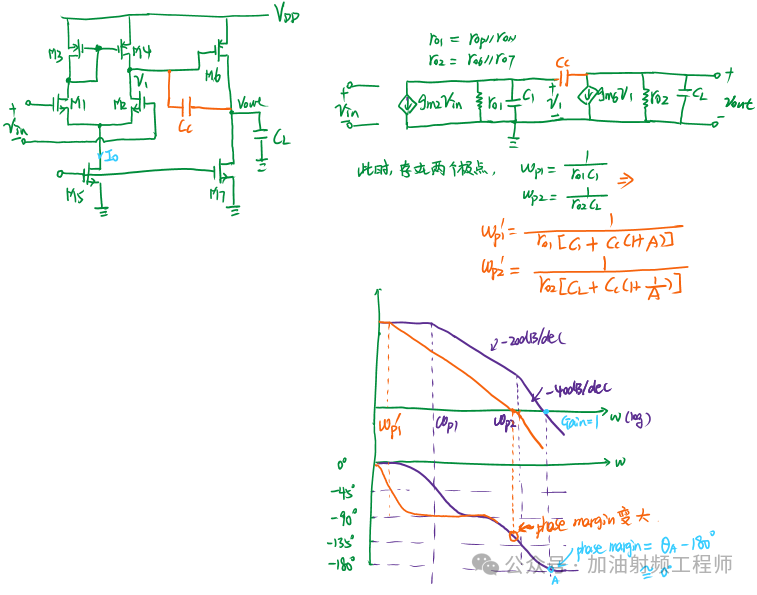

两级运放的原理框图,以及相应的分析如图 8所示,并假设p1和p2的分布也如图。

图 8未补偿的两级运放的原理图,及其小信号分析,还有波特图

如果phase margin≈0°,那怎么办呢?

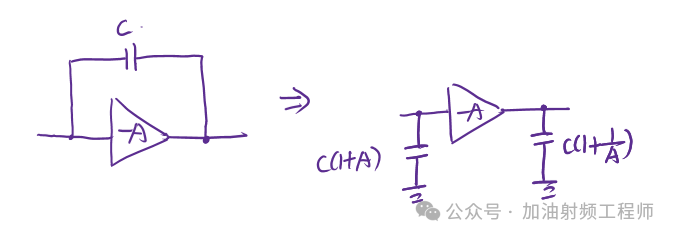

一个方法,是把把wp1往DC处移,使系统看起来像一个one-pole system。在反相放大器的输入和输出端跨接一个电容,由Miller’s theroem进行分析的话,在输入端会得到一个大电容,如图 9所示。

图 9在反相放大器的输入和输出端跨接一个电容

所以,如果在M6的输入和输出端跨接一个电容Cc,那可以使得wp1往DC处移,电路图和相应分析如图 10所示。

图 10 用Cc进行补偿后的两级运放的原理图,及其小信号分析,波特图分析

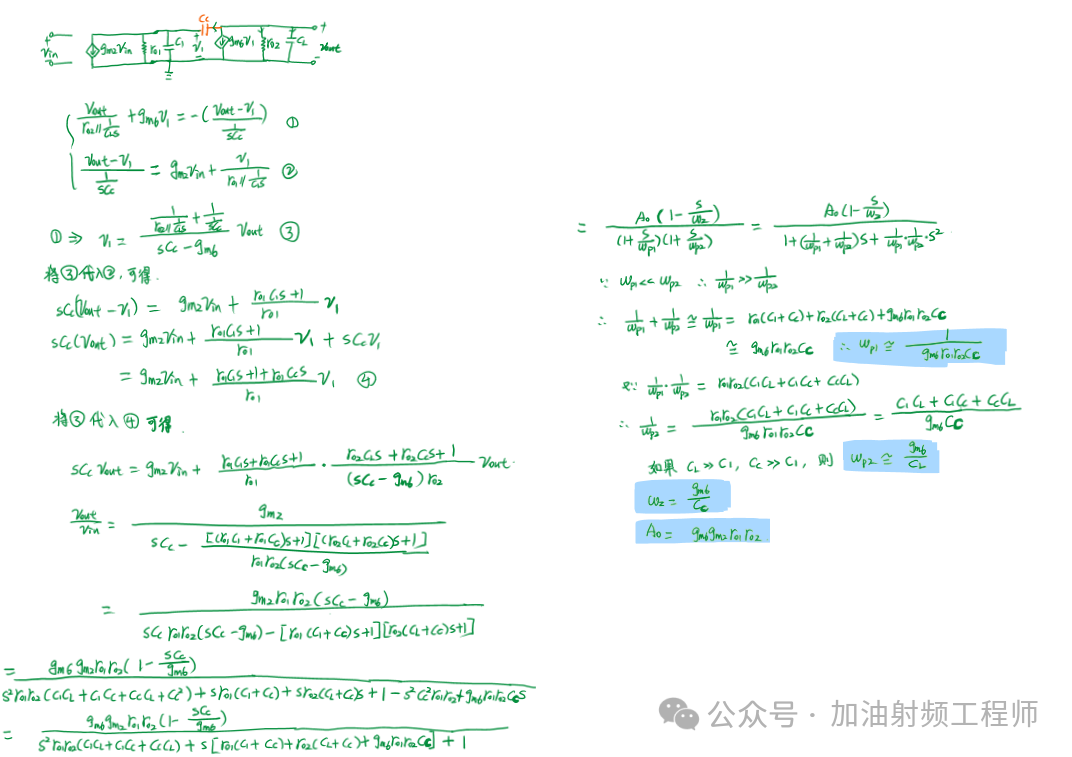

用KCL和KVL,计算上述电路的传输函数,如图 11所示。这里不使用Miller’s theorem,是因为Miller’s theroem虽然方便简单,但是会忽略到零点,同时会有pole splitting。

图 11 加入Cc电容后的两级运放的传输函数的推导

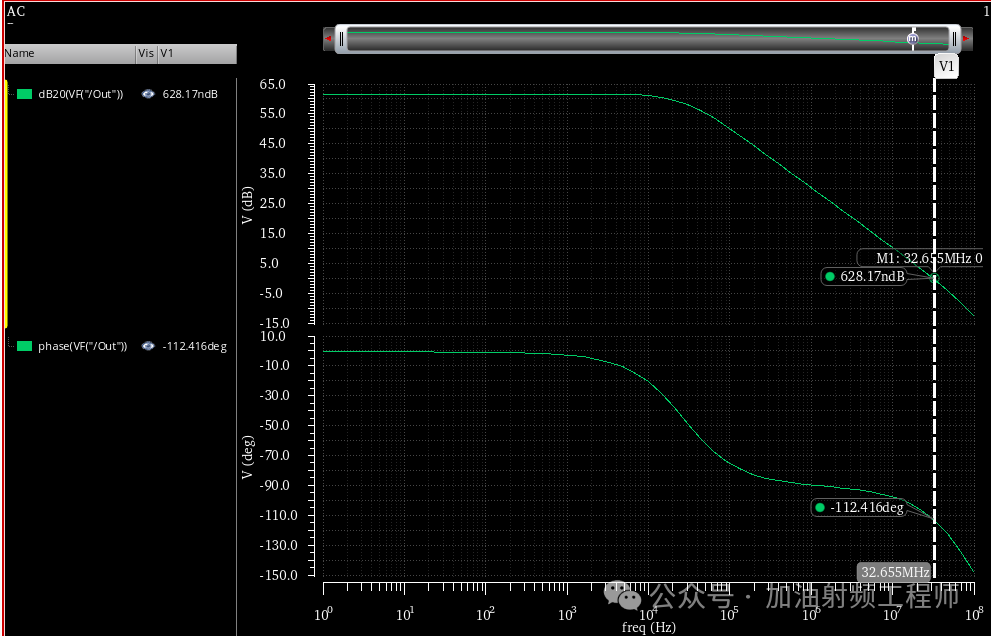

VDD=1.8VAv≥1000(60dB)GBW=30MHz,PM≥60°Slew rate=20V/usecMaximum input common mode range=1.6VMinimum input common mode range=0.8VCL=2pFPower<300uW

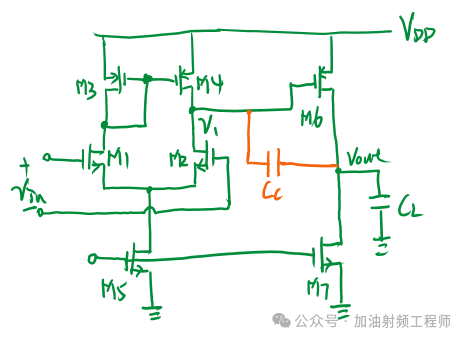

图 12 两级运放的架构

单级运放采用图 12所示架构。

在设计运放之前,需要了解的是,上面的所有的管子,都需要工作在饱和区。

同时,指标与各管子参数之间的关系是:

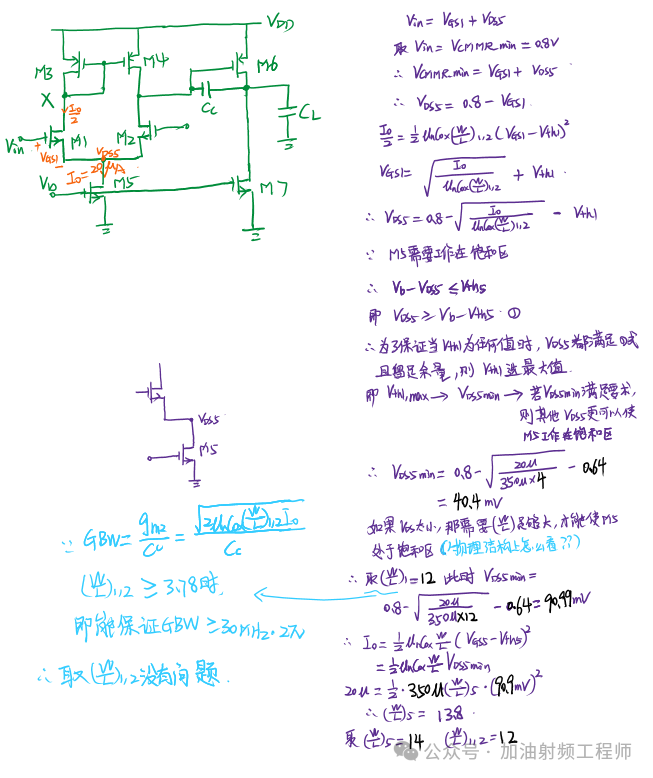

Cc由phase margin来决定Slew rate由I0和Cc来决定M3,m4由maximum input common mode range来决定M1,m2由gain bandwidth product来决定M5由minimum input common mode range来决定M7由I0和m5来决定

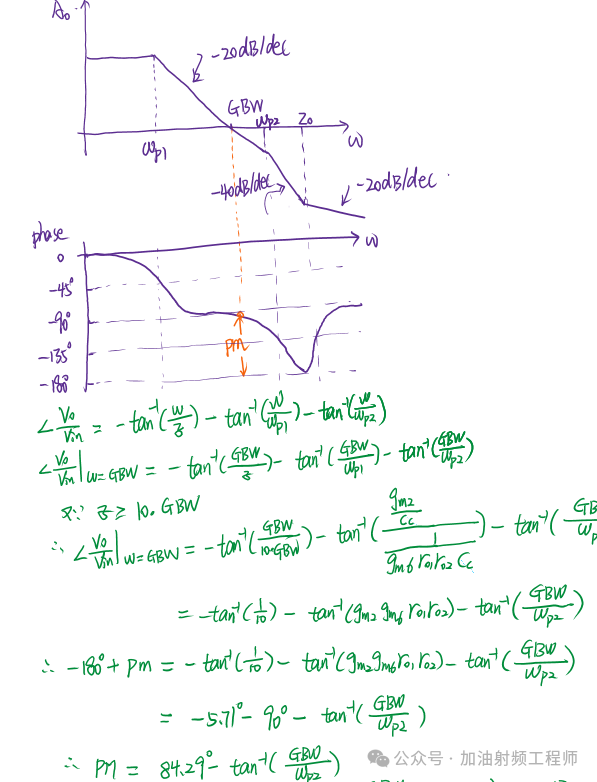

Phase margin是当增益为1时,对应的相位与-180°之间的差值。

当增益为1时,频率即为GBW,所以对应的相位裕度的计算如图 13所示。

图 13两级运放phase margin的推导

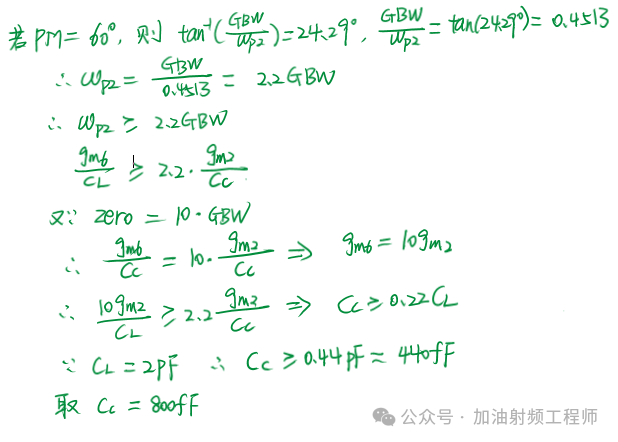

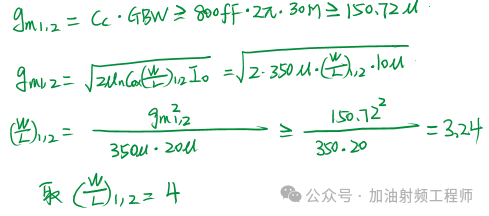

由1.2.2指标要求可知,PM=60°,CL=2pF,所以可以推导出Cc的值,如图 14所示。

图 14由phase margin推导出Cc的值

图 12所示的两级运放,在输入信号足够大时,电流I0会完全流过Cc。

图 15两级运放由slew rate来推导I0

指标要求Slew rate≥20V/usec,Cc=800fF,所以I0≥20V/usec*800fF=16uA。取I0=20uA。

通过在virtuoso软件搭建如所图 16示的电路图,然后仿真,得到上述值(确定Vt1min和Vt3max,在40min左右, series 9 )。

图 16 在virtuoso搭建电路的原理图

同时,为了减少沟道调制效应的影响,虽然使用的工艺Lmin=180nm,但是仍然选择L=1um,I0=20uA。

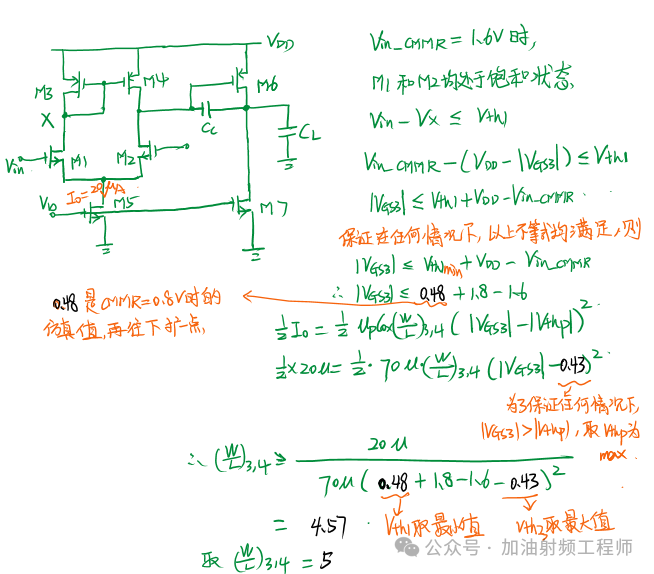

在VCM=1.6V时,可以得到Vthn≈0.633V,|Vthp|≈0.425241V;

在VCM=0.8V时,可以得到Vthn≈0.481V,|Vthp|≈0.425241V。

由下面一节的推导可知,Vthn和Vthp都各自往外扩了一点,所以取Vthn=0.48V,|Vthp|=0.43V。

借用前面的仿真,仍然取upCox=70u, unCox=350u。虽然这两个是近似值,但是作为初值计算是足够的。然后再打开上面的参数表,确认region=2,即管子处于饱和区。

推导M3和M4的尺寸,如下图所示。

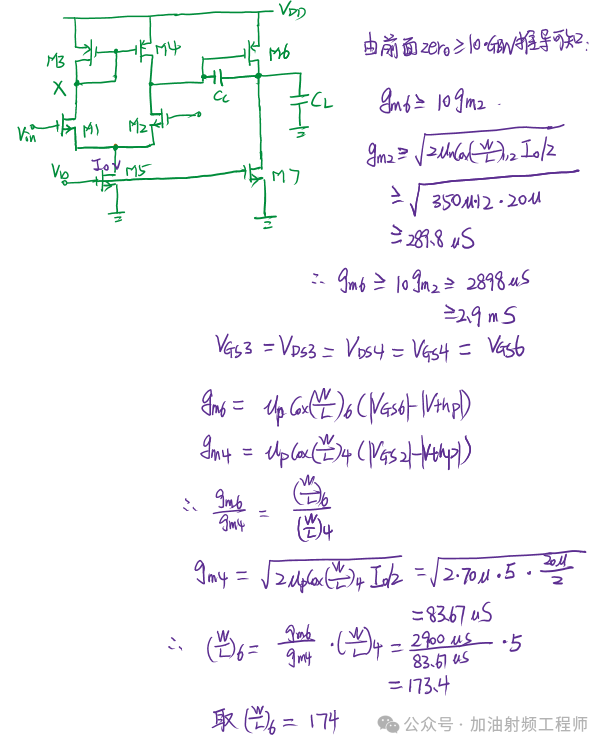

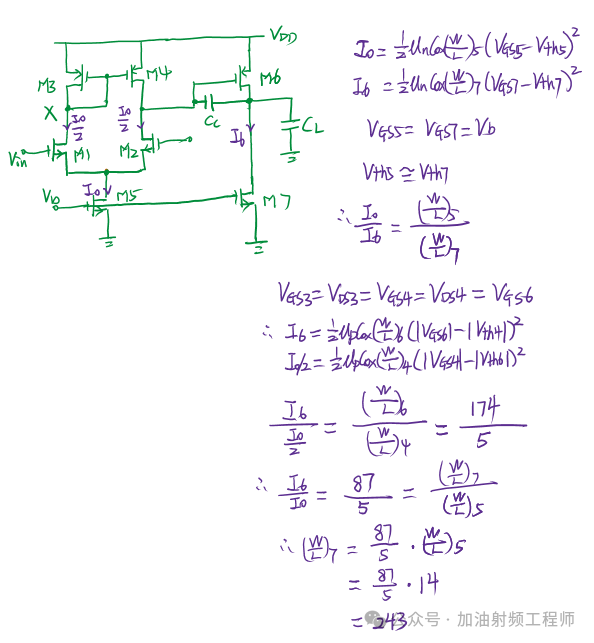

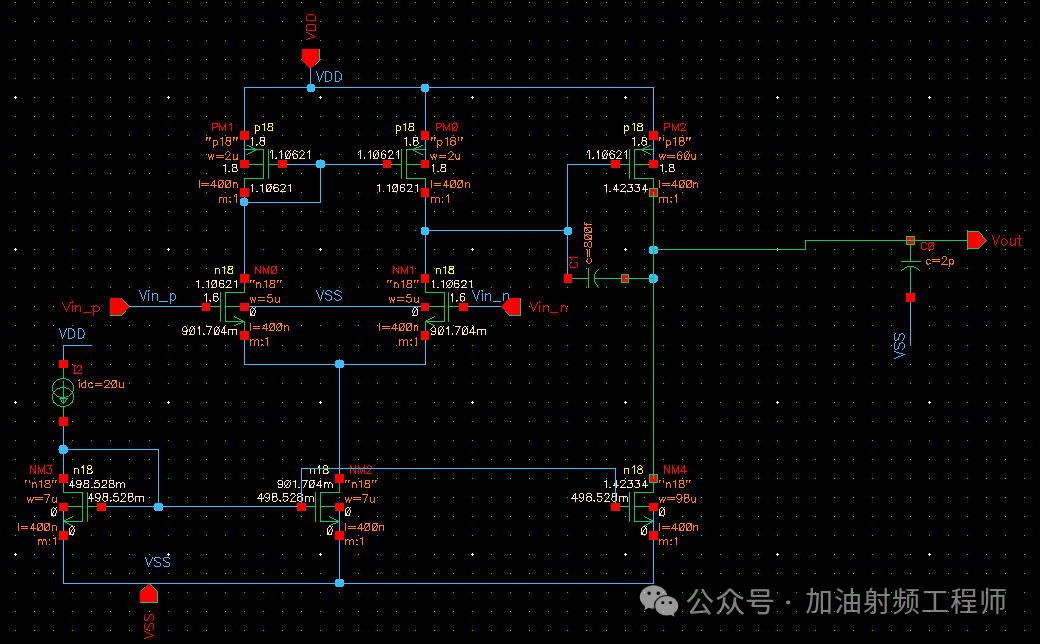

综上推算,(W/L)6=174,(W/L)7=243,(W/L)1=(W/L)2=12,(W/L)5=14,(W/L)3=(W/L)4=5,Cc=800fF,I0=20uA,原理图如下图所示。

但是进行仿真设置的时候,发现W/L的值,W最多只能是100u。

所以,把L的值设置为400nm,从而来减小W的绝对值,使其位于100um以内。

完结接收机课程吆喝处哈(已在平台上购买的同学,加我微信,领课件资料哈!)

想报名的同学,可以海报底部扫码哈!

想了解射频系统的同学,可以添加我的微信RF606yuer,备注:射频系统书籍,可以领取37本关于射频系统的书籍。

☜左右滑动查看更多

Slide for more photos