ZLG致远电子自从设计ARM核心板以来,服务了大量客户,其中有很大一部分工作是为客户调试网卡电路和驱动。既有电路设计的问题,也有驱动软件的问题,还有系统网络配置的问题。有时候解决一个问题,并不是单纯硬件或者驱动就能解决,需要多方面配合。就单看硬件方面,除了原理图设计,还有PCB布线问题。下面给出几个实际案例,从硬件设计、PCB布线以及驱动配合等方面进行阐述:

PHY复位时间不够引起网卡工作不正常;

MDIO源端没串22Ω终端电阻,信号反射导致网卡工作不正常;

PCB走线没做好等长设计,引起网卡工作异常。

复位时间不够导致网卡工作异常

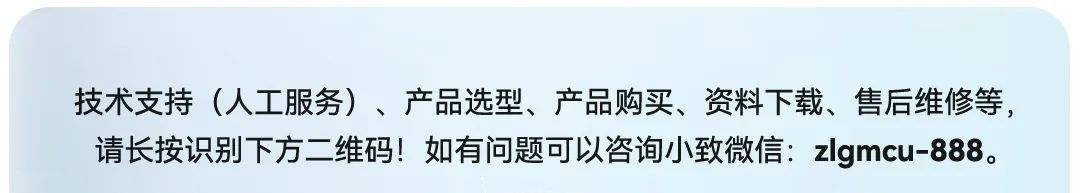

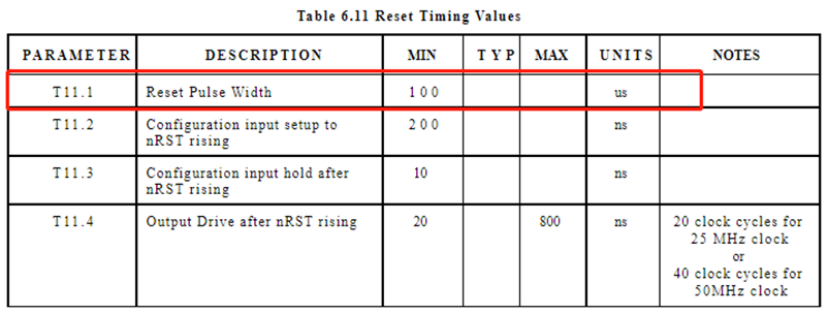

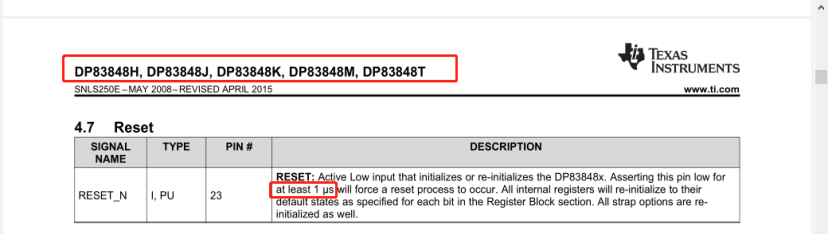

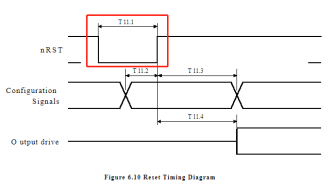

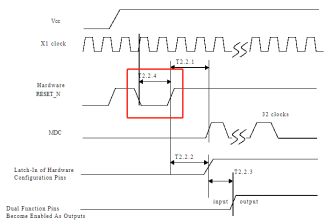

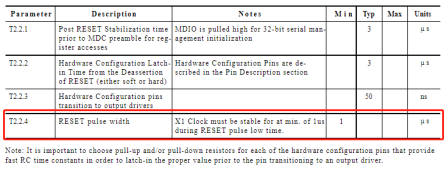

复位时间不够导致网卡工作异常LAN8720要求复位时间不得小于100us(参考图1),而参考板使用的DP83848要求的复位时间是1us(参考图2),所以采用的RC延时参数很小。在LAN8720电路上照搬了DP83848的参数,复位时间远不满足器件要求,所以网卡不能正常工作。

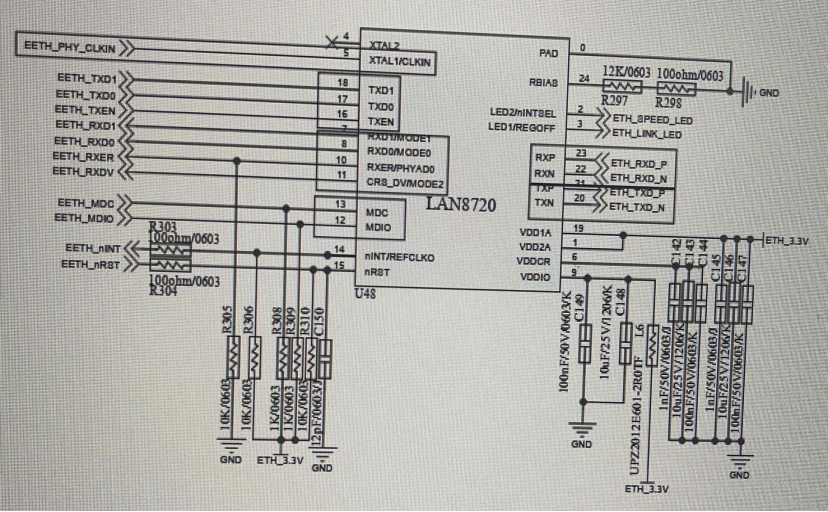

图3是客户所使用的网卡电路。

从电路图可以看到,RC复位电路,R=10KΩ,C=12pF,充电时间t = RC:(10^6*12*10^-12) = 12*10^-6 = 12us。

务必严格按照网卡芯片要求的复位时间来设计复位电路,确保网卡芯片能正常复位。

不同网卡芯片对复位时间的要求差异非常大,从微秒到毫秒都有,下面汇总一些常见网卡复位时间要求。

LAN8720:100us起,参考图4。

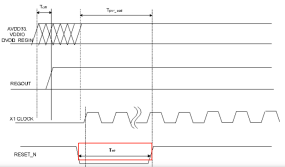

裕泰微TY8512/YT8531,10ms起,参考图6。

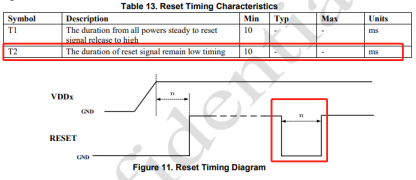

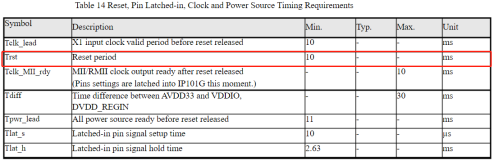

ICPlus:IP101G,10ms起,参考图7。

综上所述,在一般设计中,建议采用主控芯片的GPIO来控制PHY芯片的复位,并在靠近PHY芯片的附近并联RC电路,增强稳定性;对于主控芯片IO资源紧张,可以采用RC延时复位,但务必计算好需要的复位时间,并预留充足的裕量。

另外满足了这个手册要求的复位时间也不一定就能够正常工作。设计中如果采用MAC给PHY提供参考时钟的工作方式,由于主控的参考时钟默认可能是输入模式,需要加载驱动后将软件配置为输出模式,所以还要保证复位释放前,以太网驱动已经加载完毕,设计RC复位参数时需要将这些时间都计算在内。

其实不仅仅是网卡芯片,其它带复位引脚的芯片,在设计电路的时候都需要考虑芯片的复位时间要求,以设计满足条件的电路,确保其能正常工作。