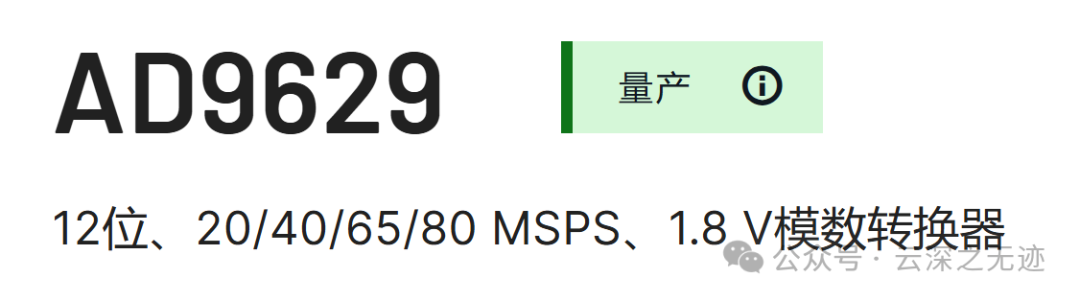

20号的时候,润石又发了一个新品(14位单通道AD转换芯片RS1520,采用Pipeline架构设计,带有片上采样保持电路和时钟占空比稳定器,支持全差分输入,转换速率支持20M、40MSPS。

我没有查到这个AD9629是什么时候发布的,18年就有一个贴子在用了,而且现在可以很方便的买到,润石加油啊!

这个片子来者不善,就是来攻击ADI的:

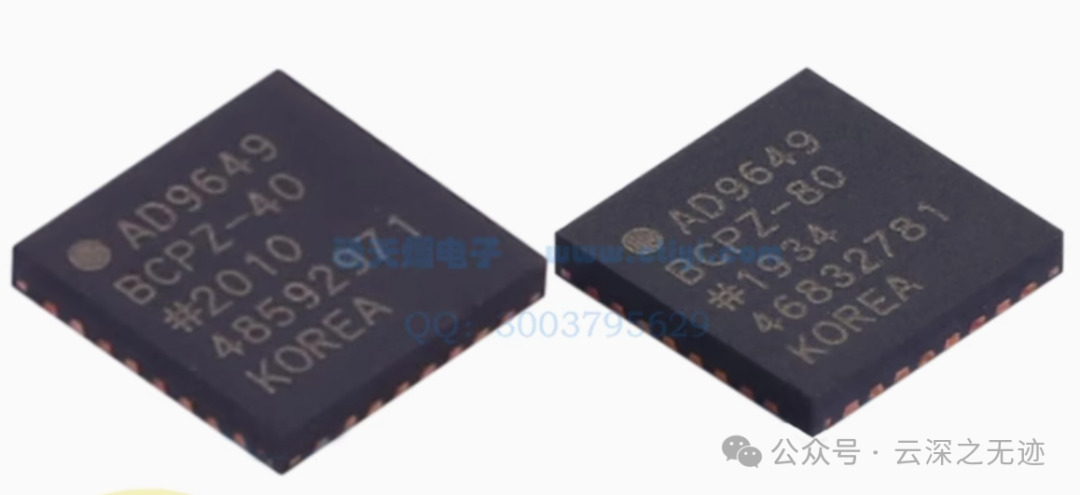

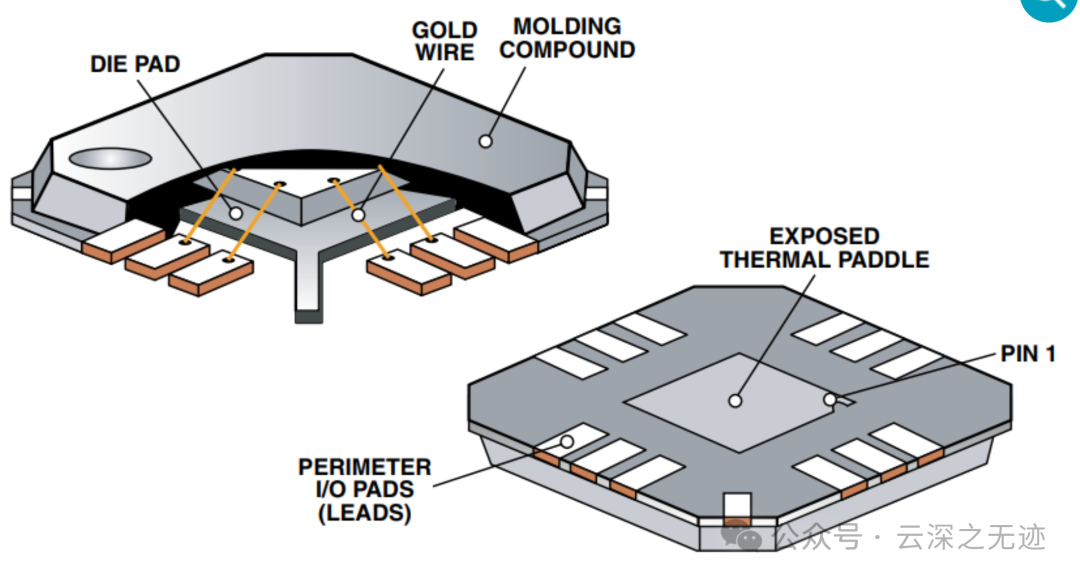

这个AD9629的后庭

咋说呢,破不了招,参数上面没什么比头,那就看后面片子的价格了,ADI还有一个转换速率到80M的.

emmmm,因为又是云发布,这里就看ADI的了,因为一直不会FPGA就不看这些高速的东西,但是现在准备学了,就看看吧,而且我还没有研究过并行的ADC。

首先是看产品定位,高速转换,就是牺牲位数获得转换带宽

润石再云发布不写了,不够意思,芯片的样子

淘宝估计是翻新的,225就能拿下80后缀的

以及还有这样的封装:

LFCSP(ADI自己起的名字)就是"引线框CSP",在转包封装厂那里也称为QFN、MLF、MLP以及LPCC。

外观是这样的

与标准塑封相比,LFCSP技术具有多种重要优势:

芯片尺寸更接近封装尺寸,减少了板安装空间。

消除了铅料,缩短了从芯片到PCB的电通路长度,从而提高了电气特性。

裸露焊盘焊接至PCB,降低了热阻。

引脚架构工艺采用行之有效的现有引脚架构封装技术。

可使用标准的SMT装配设备;无需底部充胶。

低质封装在焊锡固化期间具有自动对齐特性,有利于提高装配成品率。

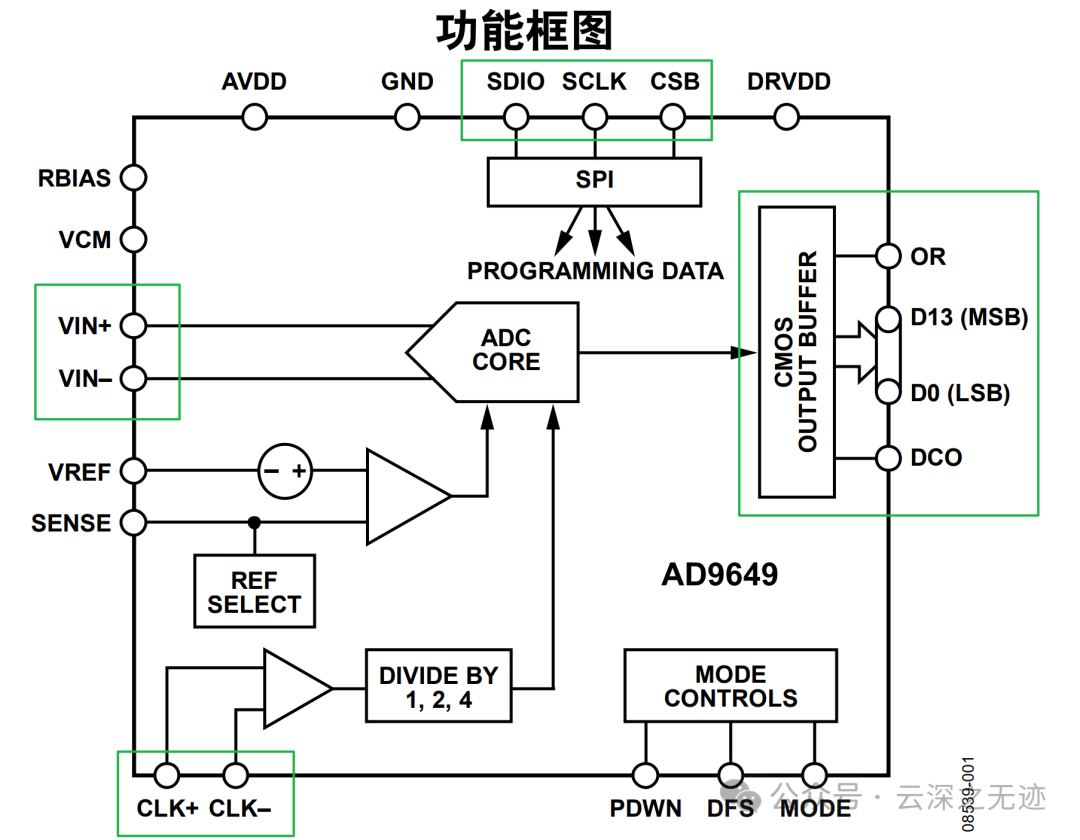

也是时钟,可以看到可以分频,一个Flash的ADC,流水线架构,为了应对大数据流,这就是FPGA的主场了。

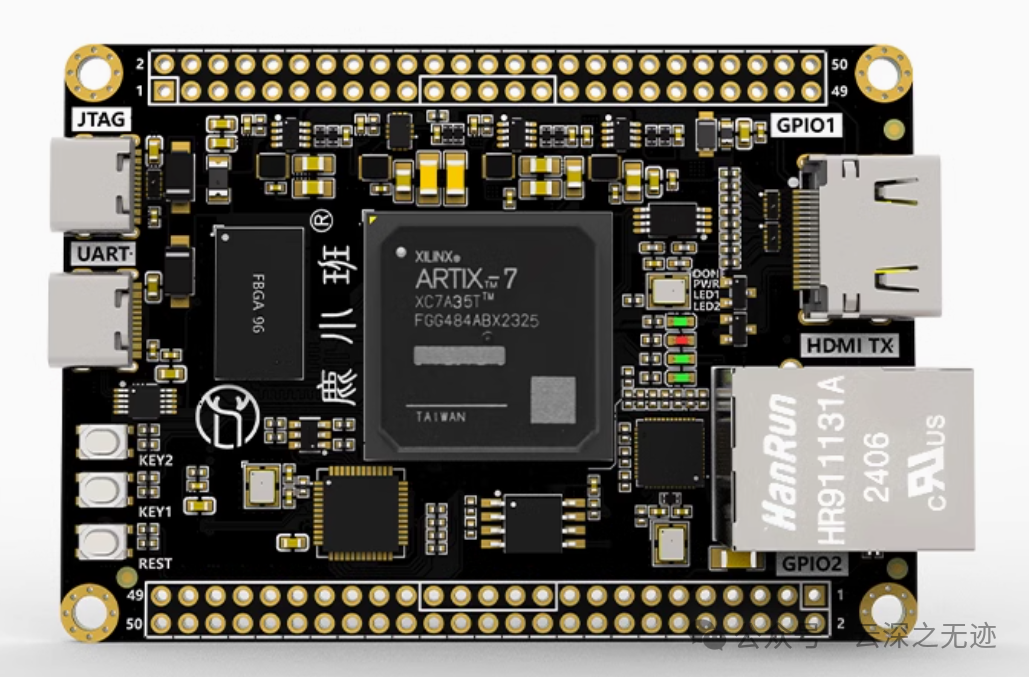

买了这个,嘿嘿

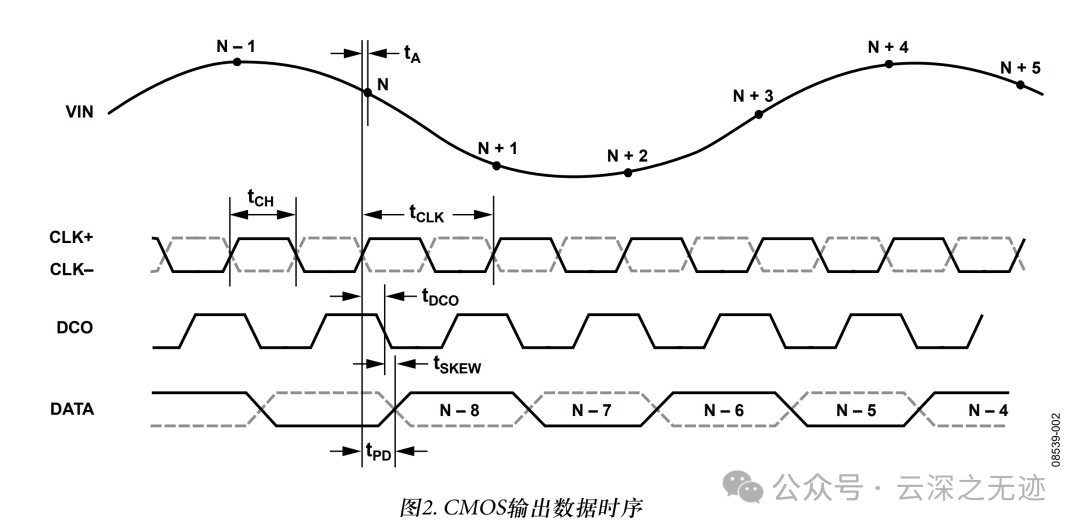

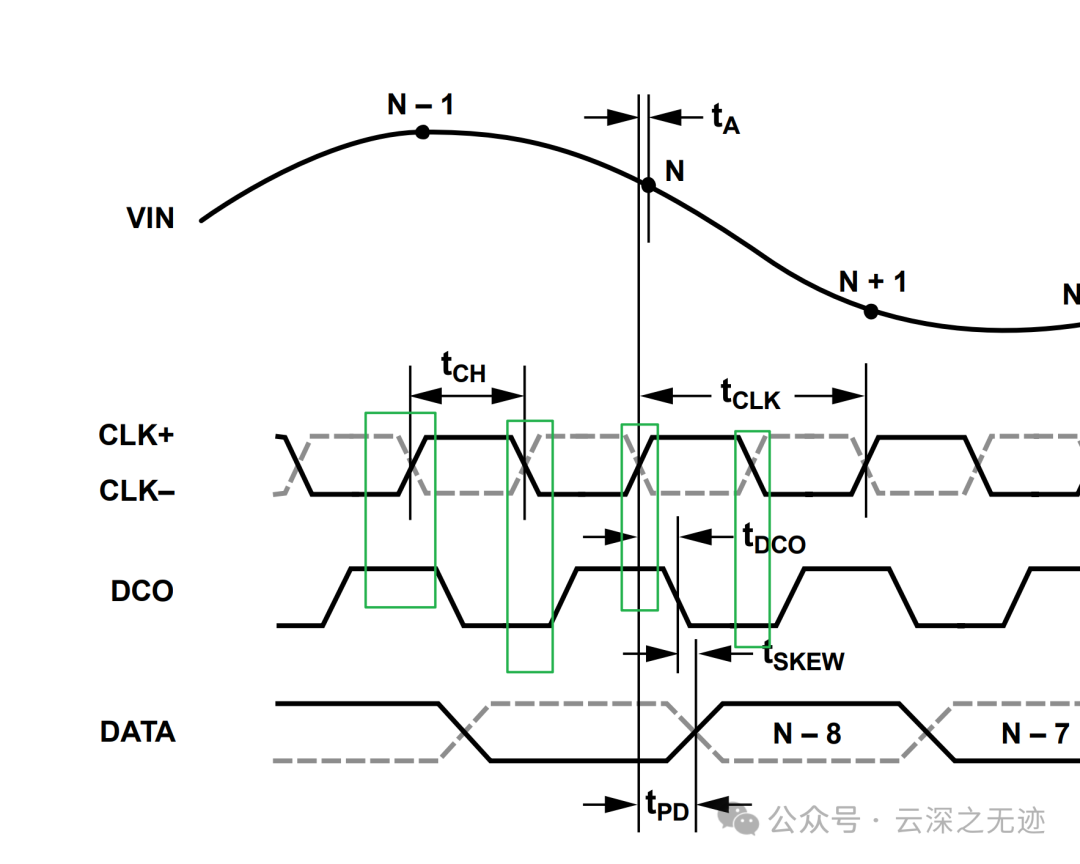

有个时序图,在编写驱动程序的时候需要看

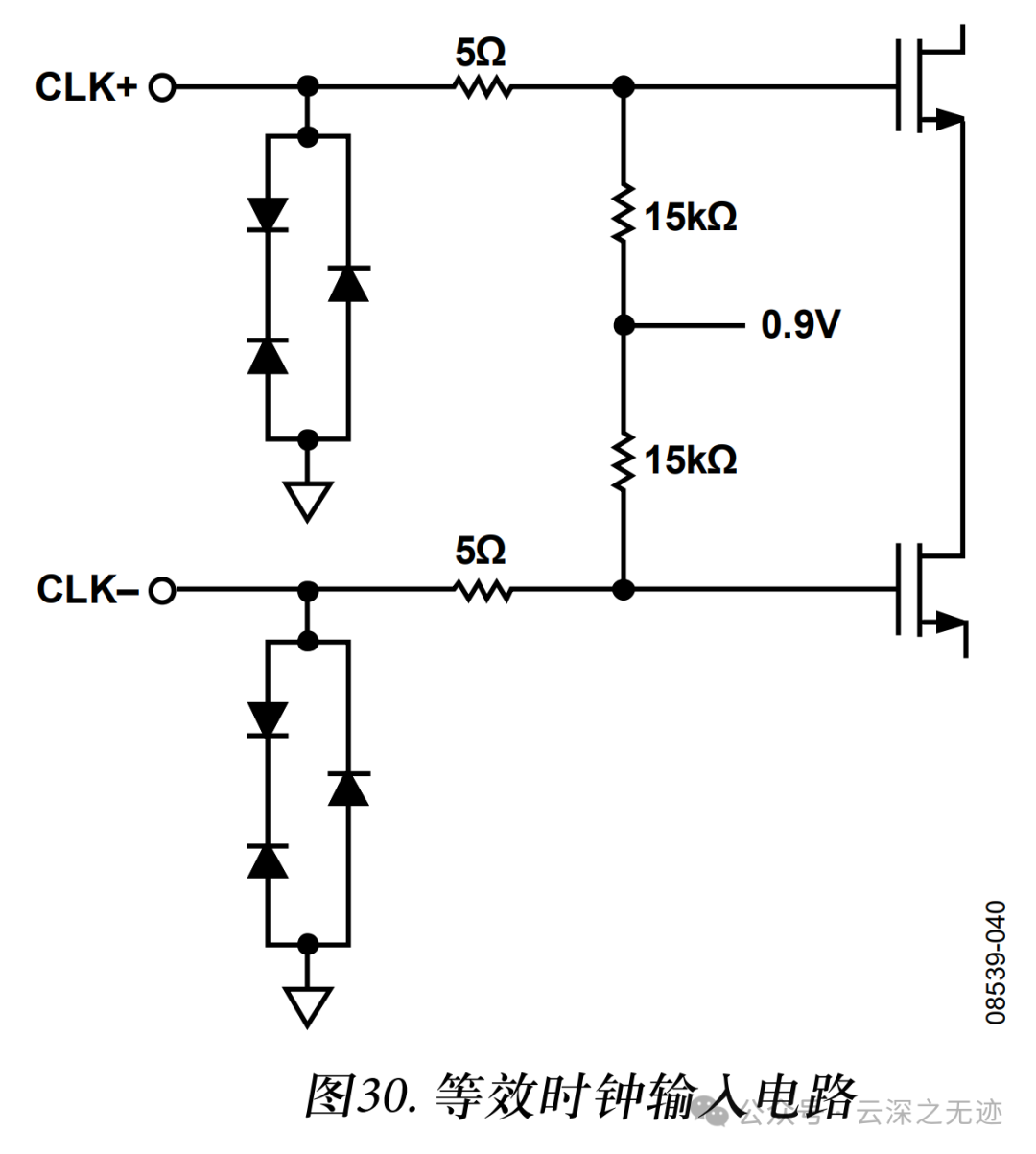

这里出现了一对儿差分时钟:(差分都是为了抗噪音)

共模噪声抑制: 差分信号通过两条导线传输,信号幅值相等但极性相反。当外部噪声干扰这两条导线时,由于噪声通常是共模的,即同时作用于两条导线且幅值相等,因此在差分接收端,共模噪声会被抵消,从而提高信号的抗噪能力。抑制地线噪声: 差分信号对地线噪声的敏感度也较低。因为地线噪声通常会同时影响两条导线,而在差分接收端,地线噪声也会被抵消。

辐射更小: 差分信号的两条导线产生的电磁场方向相反,相互抵消,从而减少了电路对外界的电磁辐射。抗干扰能力强: 差分信号对外部电磁干扰的敏感度也更低,因为外部电磁场产生的感应电流在两条导线上会产生相位相反的电流,从而抵消了外部电磁场的影响。

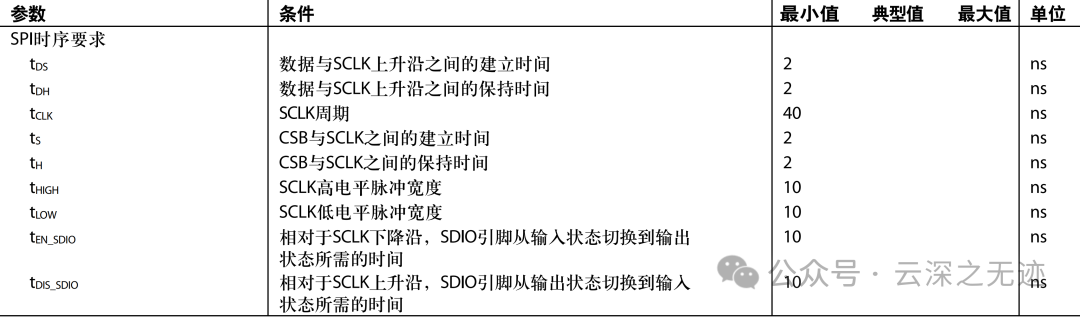

这个是一些参数,就是一个SPI的参数

VIN: 模拟输入信号。它的变化会触发ADC的采样和量化过程。

CLK+,CLK-: 差分时钟信号。这两个信号相位相反,用于驱动采样保持电路。

DCO: 数字控制振荡器输出信号。它通常用来控制采样保持电路的开关时间。

DATA: 数字输出数据。这是ADC将模拟信号转换成的数字信号。

ta, tcH, tcLK, tpco, tSKEW, tpD: 这些都是表示不同时序参数的时间间隔,它们共同决定了ADC的采样时间、保持时间以及数据输出的时间。

看时序图,就是并行的看,当一个信号工作的时候其他的在干嘛,由于物流世界的不完美,会导致边沿不完美:

实际上直上直下的,所以这个就叫边沿时间

还有就是数据之间的协同作用,必须有另外的信号参与进来。至于数据的输出,始终记住输出的是01,也就是码元。

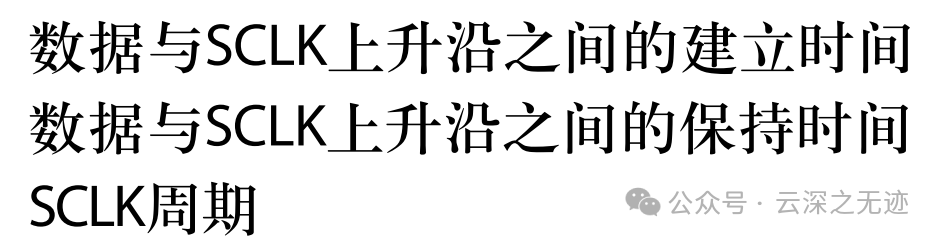

建立稳定的时间,因为你信号还在变,状态不确定,在稳定以后会持续多久?周期是计算时钟用的。

采样时刻: 当CLK+上升沿到来时,采样保持电路开始采样模拟输入信号VIN。此时,VIN的值被锁存到一个内部的采样保持电容上。

保持时间: 在采样时刻之后,采样保持电容上的电压需要保持一段时间,以保证ADC能够准确地对采样值进行量化。这个保持时间由tcH决定。

数据输出: 在采样和量化完成后,ADC会将数字结果输出到DATA引脚上。tpD表示数据输出的延迟。

时钟偏移: tcLK表示时钟信号的周期,而tSKEW表示DCO信号相对于CLK信号的偏移。这两个参数的精确控制对于保证采样时刻的准确性非常重要。

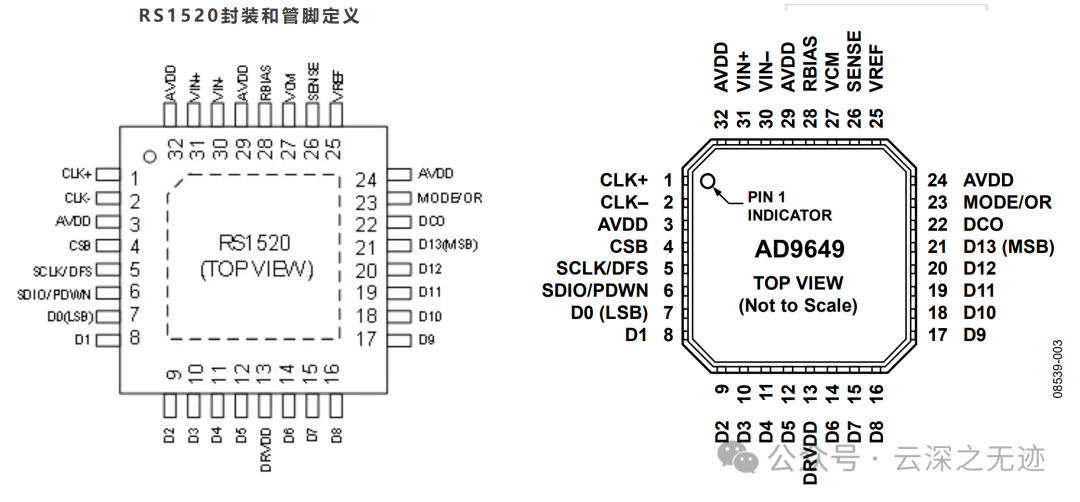

引脚是兼容的

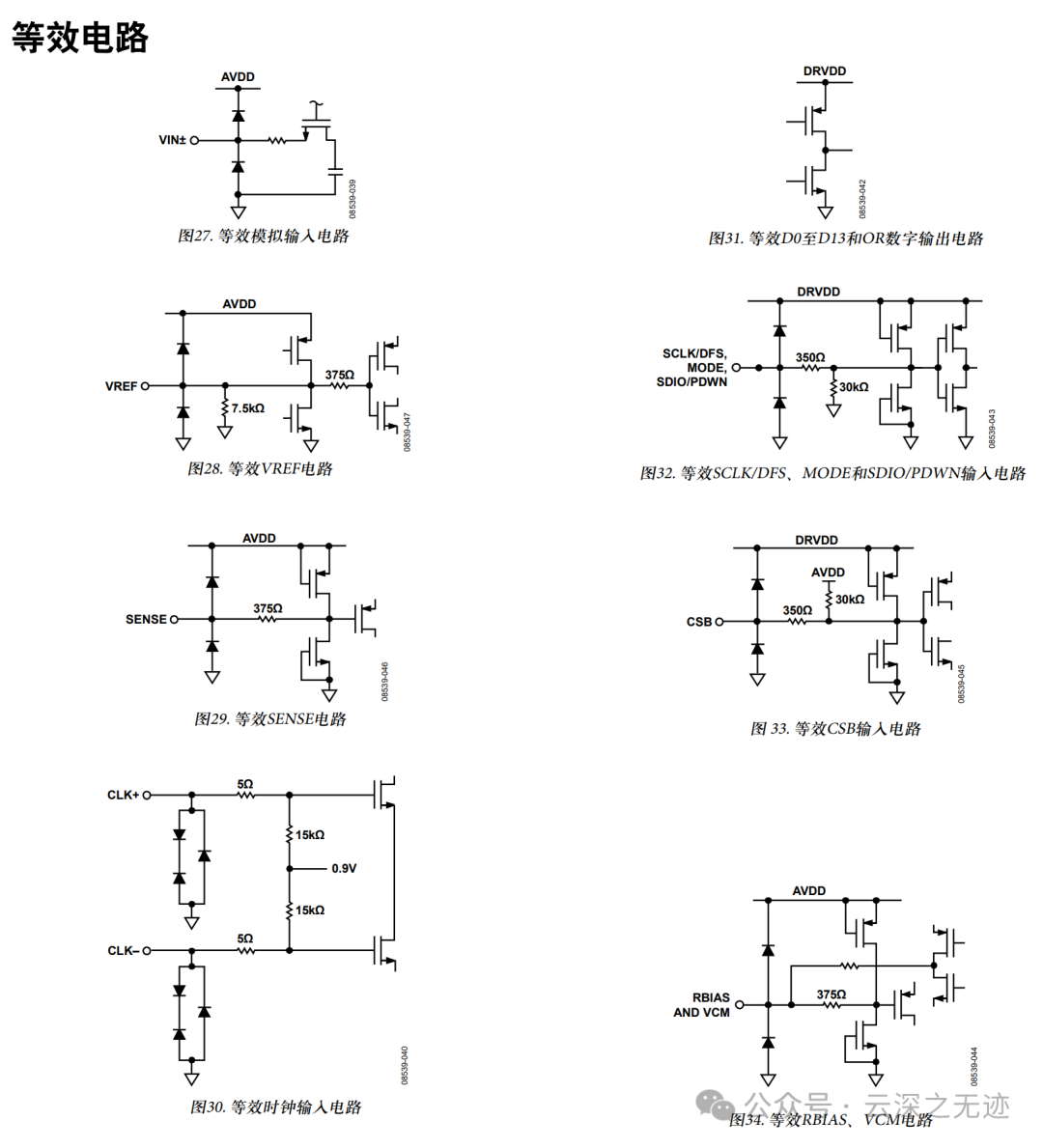

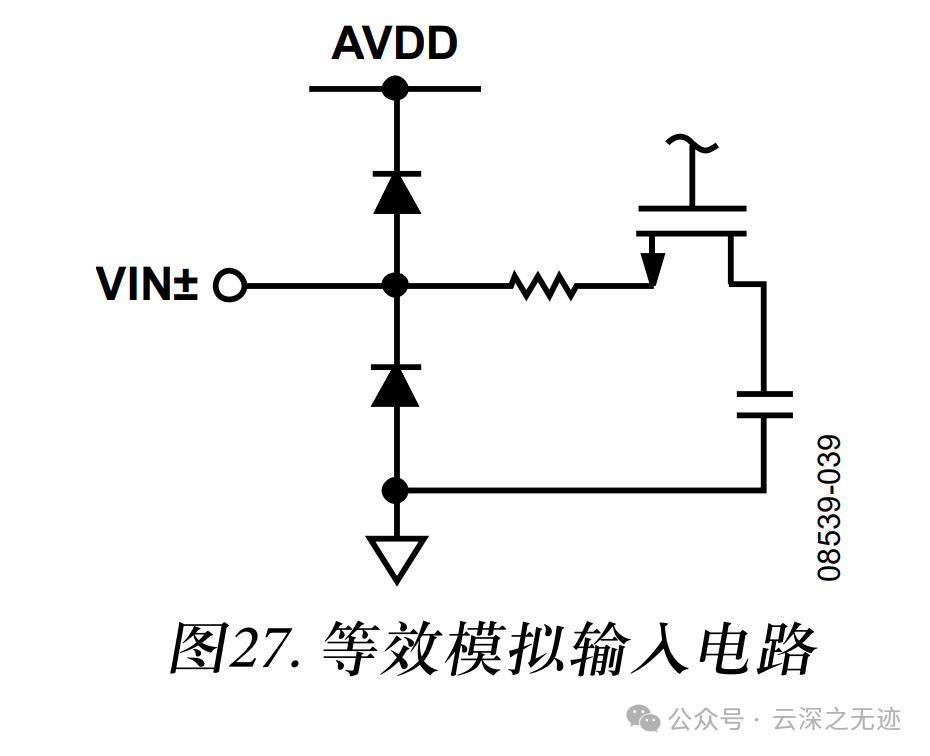

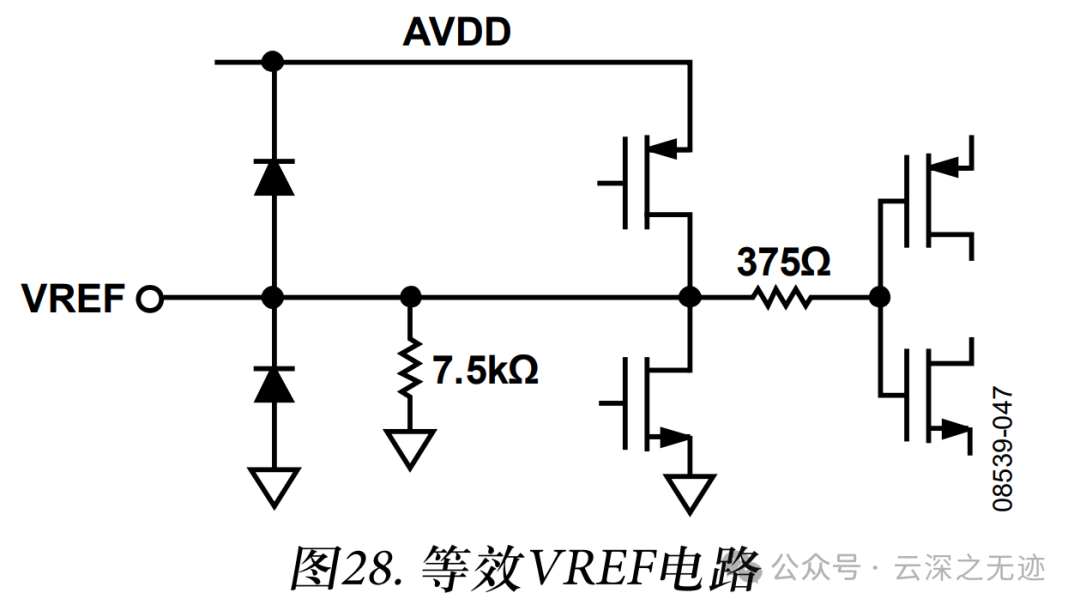

给了一个等效电路,其实就是大概咋工作的,我一眼就看出来了

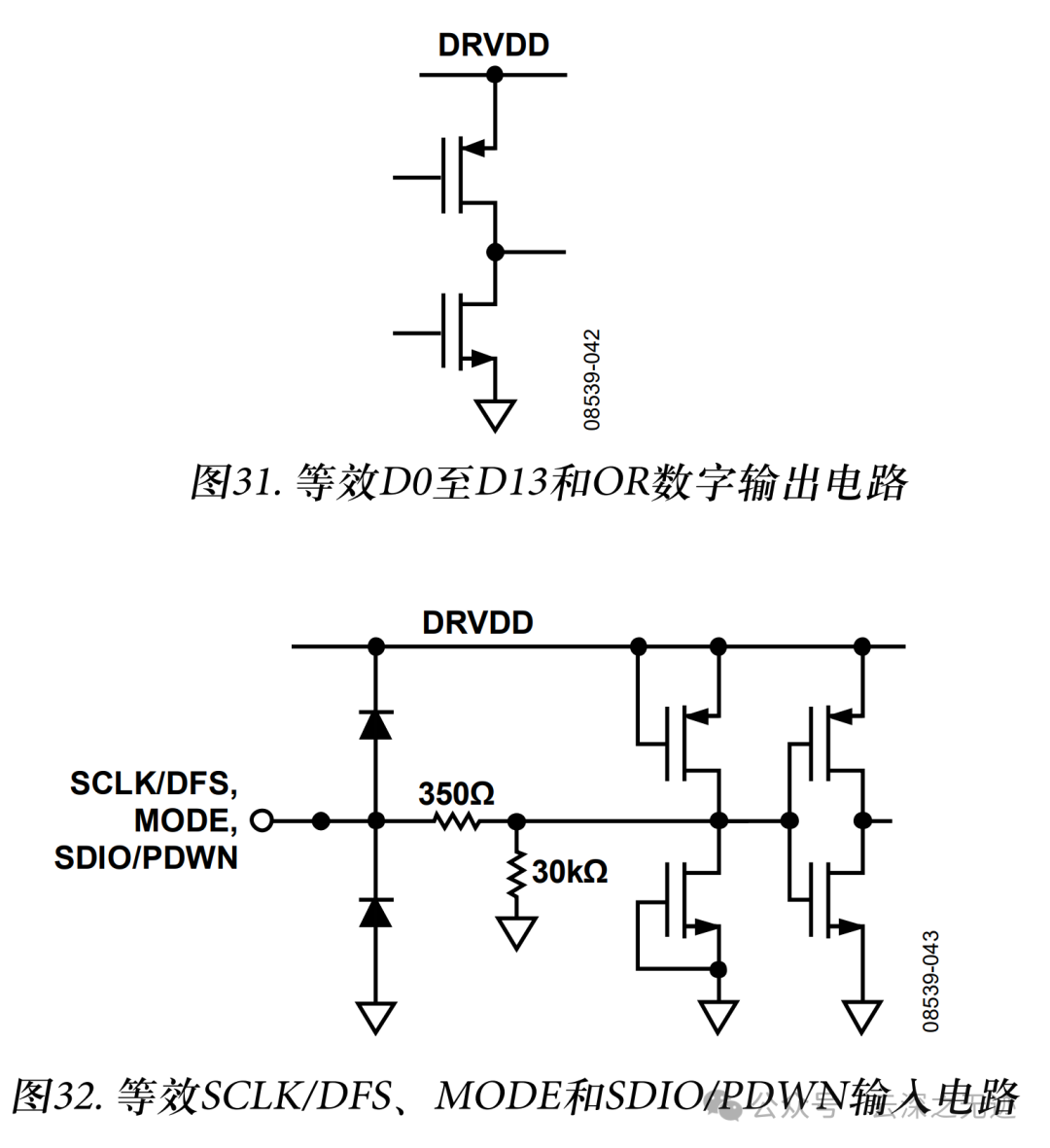

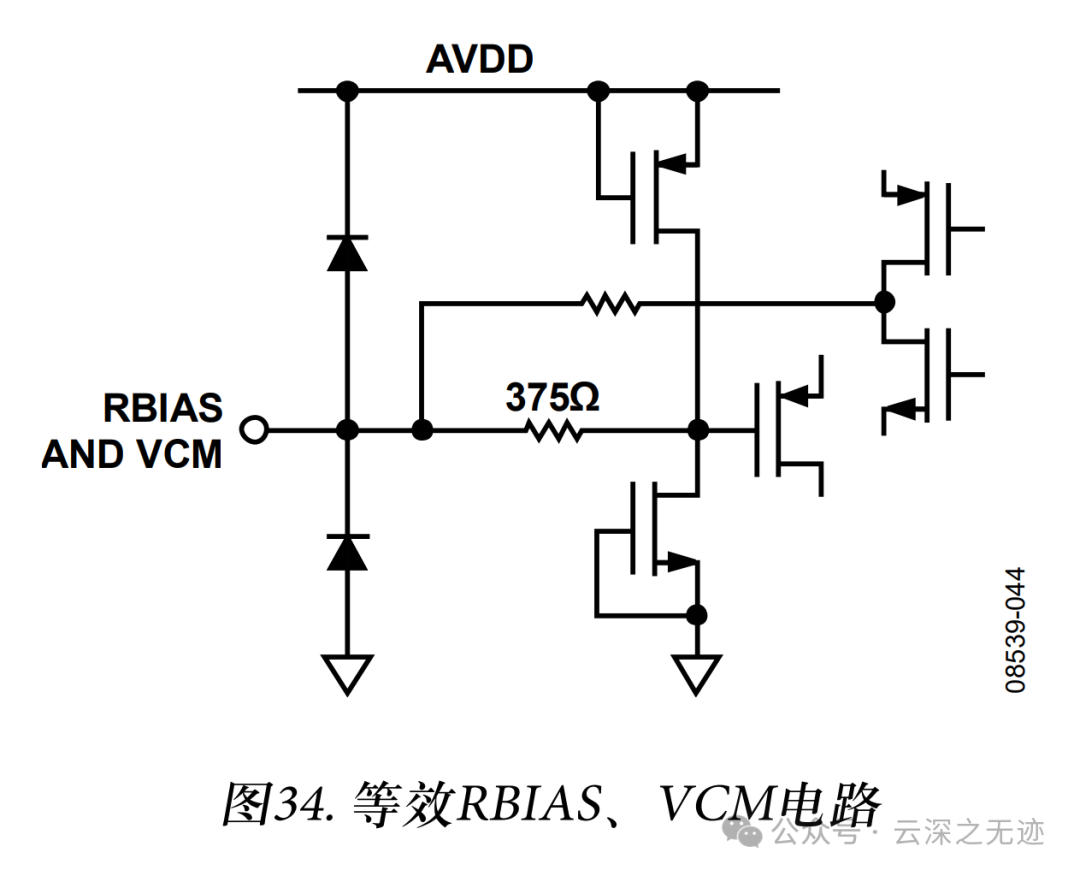

这些电路图展示了芯片内部如何处理这些信号,为了解芯片的工作原理提供了直观的参考。

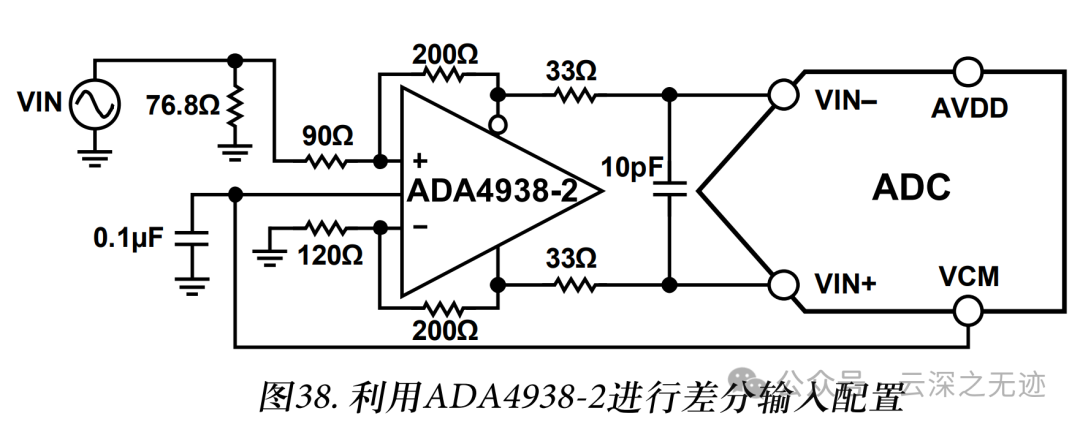

将外部模拟信号VIN+和VIN-输入到芯片内部。采用差分输入方式,提高抗噪性。输入信号经过缓冲放大,增强驱动能力。

提供一个稳定的基准电压VREF,用于ADC的转换参考。采用分压电路实现,稳定性较高。VREF的精度直接影响ADC的转换精度。

接收差分时钟信号CLK+和CLK-。采用差分输入方式,提高抗噪性。输入阻抗匹配,减小信号反射。

接收CSB、SCLK/DFS、MODE/OR、SDIO/PDWN等控制信号。大部分信号采用上拉或下拉电阻,提高信号稳定性。部分信号可能具有多重功能,根据不同的工作模式而变化。

提供模拟输入端的偏置电流和共模电压。RBIAS通过一个电阻连接到地,提供稳定的偏置电流。VCM通过一个电阻分压网络连接到AVDD,设置模拟输入的共模电压。

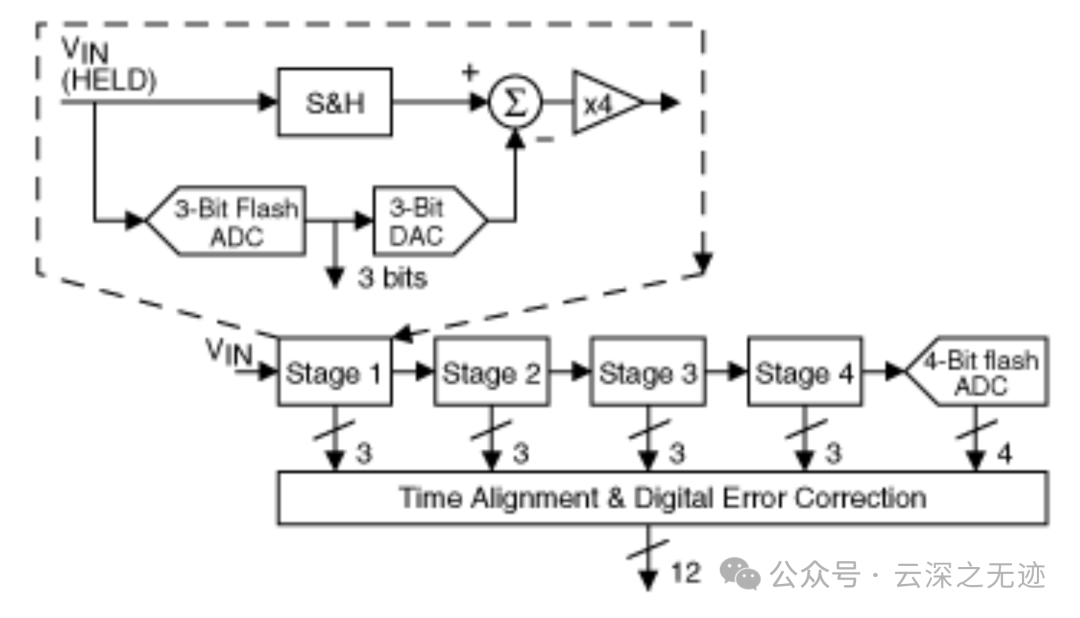

流水线 ADC 是采样率从几 Msps 到 100Msps+ 的首选架构。设计复杂性仅随位数线性增加(而不是指数增加),从而为转换器提供高速、高分辨率和低功耗。流水线 ADC 非常适用于各种应用,尤其是在数字通信中,转换器的动态性能通常比传统的 DC 规格(如差分非线性 (DNL) 和积分非线性 (INL))更重要。在大多数应用中,流水线 ADC 的数据延迟并不重要。

ADI

世界上的器件这么多,没关系,研究架构就好了,一通百通。

接下来说构架,事实上,我们以前写的都是积分比较这种架构的,但是速率高了,明显就倒腾不过来。一般大规模的事情,我们就考虑能不能并行,就是很多模块一起干!GPU来了。以及能不能流水线,就是把一个工序进行拆分,谁也别闲着,一边转换,一边输出,一边进行下一次的工作准备。

上面的就是一个单独的转换模块,一起转换,转完给下一级

在此原理图中,模拟输入 V IN首先由采样保持 (S&H) 进行采样并保持稳定,而第一阶段的闪存 ADC 将其量化为三位。然后将 3 位输出馈送到 3 位 DAC(精确到大约 12 位),并从输入中减去模拟输出。然后将此“残余”放大四倍并馈送到下一级(第 2 阶段)。此放大的残余继续通过管道,每级提供三位,直到到达 4 位闪存 ADC,后者解析最后 4LSB 位。由于每个阶段的位都是在不同时间点确定的,因此在馈送到数字纠错逻辑之前,与同一样本相对应的所有位都与移位寄存器进行时间对齐。请注意,当一个阶段完成样本处理、确定位并将残余传递到下一个阶段时,它就可以开始处理从每个阶段中嵌入的采样保持接收到的下一个样本。这种流水线操作是高吞吐量的原因。

采样保持:模拟输入信号首先被采样保持电路捕获,确保在后续的量化过程中信号保持稳定。

第一级量化:采样值被第一级Flash ADC量化为3位。3位数字输出被转换为模拟信号,并从原始输入信号中减去。

余量放大:上述得到的差值(即量化误差)被放大4倍,以提高后续级的分辨率。

后续级处理:放大后的残余信号进入下一级,重复上述过程。每级都对上一级的量化误差进行校正,逐渐提高转换精度。

数字校正:各级产生的数字输出被送入数字校正逻辑,进行组合和校正,得到最终的14位转换结果。

时间对齐:由于各级处理的时间不同,需要通过移位寄存器将同一采样点的各个位对齐,以便进行数字校正。

上面就是流水线的常规操作了:

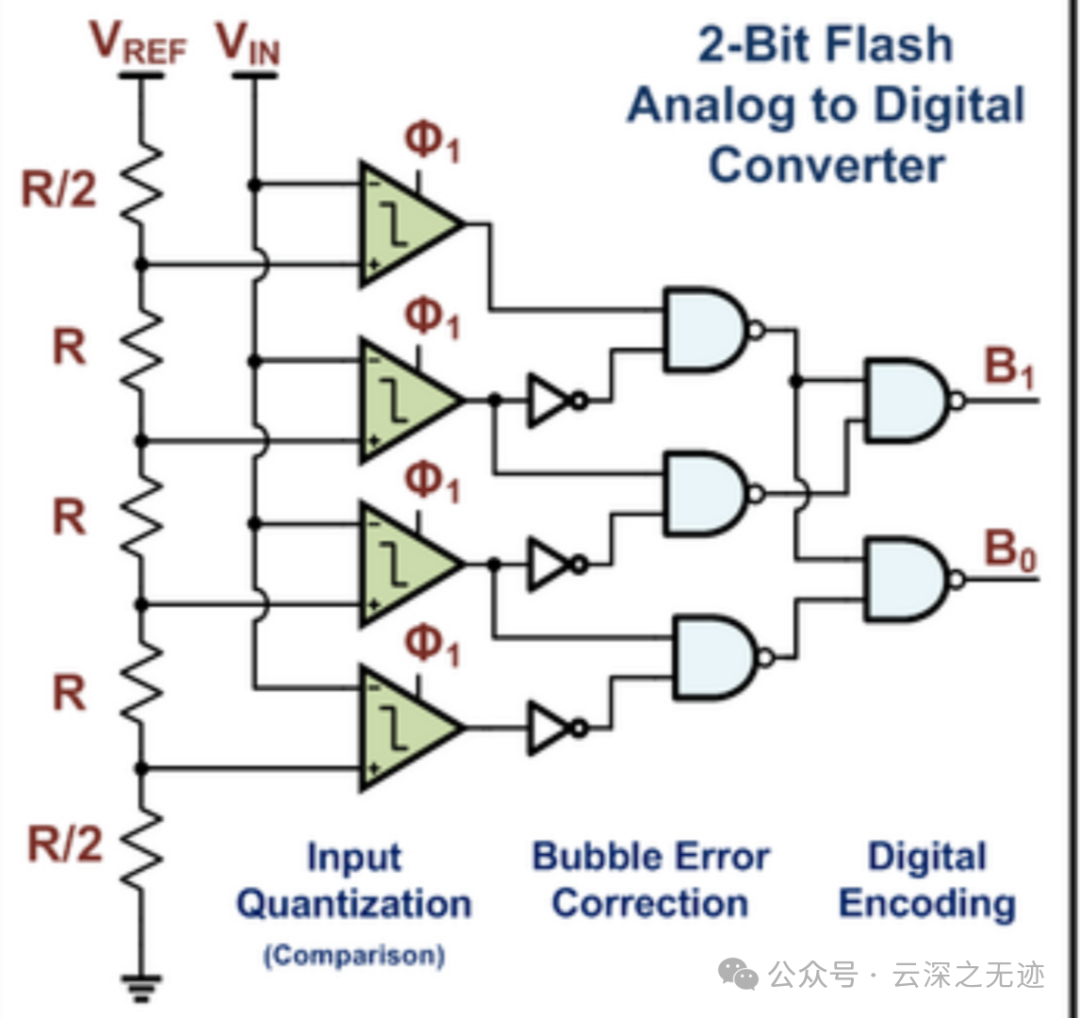

这个东西叫flash ADC

有感觉没有?积分的是慢慢的算,比较的是二进制搜索。这个就更快了,并行的比较输出结果。

你可以把它想象成一个同时进行许多次比较的电子赛跑比赛。

起点和终点: 想象一下,我们有一条赛道,起点是模拟信号的电压,终点是多个不同的参考电压。

选手: 每个参考电压都对应一位选手。

比赛开始: 模拟信号和所有的参考电压同时开始“赛跑”。

胜出者: 哪个参考电压最接近模拟信号的电压,对应的选手就“获胜”。

记录成绩: “获胜”选手的编号就是模拟信号的数字表示。

工作原理就是:

并行比较器: Flash ADC内部有大量的比较器,每个比较器负责将输入信号与一个特定的参考电压进行比较。同时比较: 所有比较器同时开始工作,将输入信号与所有的参考电压进行比较。快速得出结果: 由于是并行比较,所以能够非常快速地得到比较结果。数字编码: 比较结果被编码为一个二进制数,就代表了模拟信号的数字值。快就快在了六亲不认。

你可以把Flash ADC想象成一个同时进行多场比赛的体育场。每个赛道代表一个参考电压,所有的选手(比较器)同时起跑,通过比较,快速得出比赛结果。

AD9649采用多级流水线结构,将模数转换过程分解为多个阶段,每个阶段由一个低分辨率的Flash ADC、一个开关电容DAC和一个余量放大器组成。

这种结构的优势在于:并行处理: 各级可以并行处理不同的采样点,提高转换速度。误差校正: 每一级都对上一级的误差进行校正,提高了整体的转换精度。高线性度: 通过多级流水线结构,可以实现较高的线性度。

工作流程是:

采样: 在时钟上升沿,模拟输入信号被采样并保持。

逐级量化: 采样值依次经过各级Flash ADC进行量化,每一级都会产生一个量化误差。

余量放大: 量化误差被放大,并反馈到下一级,用于校正下一级的量化误差。

数字校正: 最终的数字输出经过数字校正逻辑处理,得到14位的转换结果。

里面的模块有以下这些:

Flash ADC: 低分辨率的ADC,用于初步的量化。

开关电容DAC: 根据Flash ADC的输出,产生一个模拟量,用于反馈到下一级。

余量放大器: 放大上一级产生的量化误差,为下一级提供校正信号。

数字校正逻辑: 对各级产生的数字输出进行组合和校正,得到最终的转换结果。

输出缓冲器: 将数字输出转换为CMOS兼容的信号,并提供可调的输出电压摆幅。

剩下的就是应用要点了,下次写

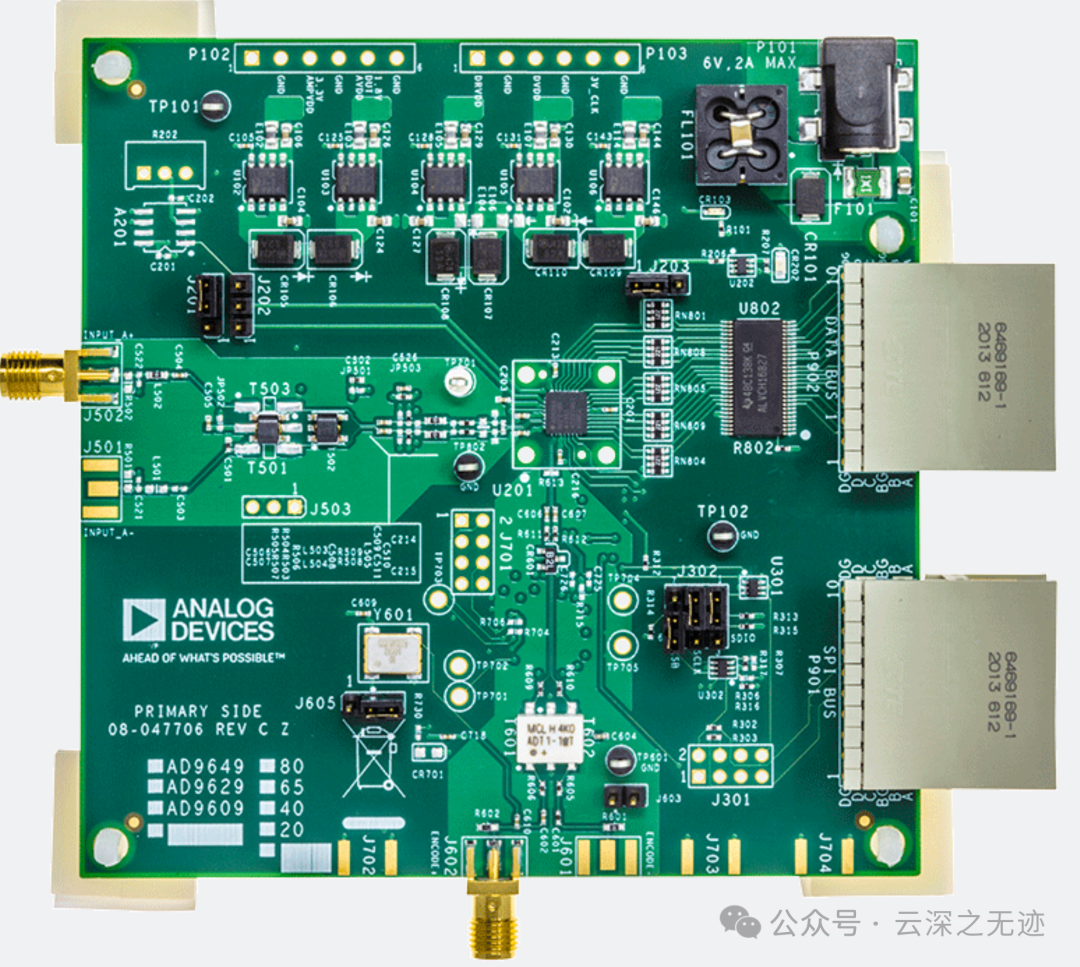

官方的PCB真漂亮啊,这布局就是一个顺畅

好的,滚回我的低速世界抓泥鳅去了。

https://www.analog.com/en/resources/technical-articles/understanding-pipelined-adcs.htmlhttps://mp.weixin.qq.com/s/xmxgUnaBJnTV2MrmbnDofwhttps://www.analog.com/media/cn/technical-documentation/data-sheets/AD9649_CN.pdfhttps://www.taobao.com/list/item/626012986512.htmhttps://www.analog.com/cn/resources/app-notes/an-772.html