新一代CMOS图像传感器可以利用所有图像数据来感知场景、理解情况,并通过在传感器中嵌入AI进行干预。由于智能图像传感器在智能手机、汽车和医疗设备中的高性能成像能力,对智能图像传感器的需求正在迅速增长,因此CEA-Leti研究人员报告了这一设计突破。

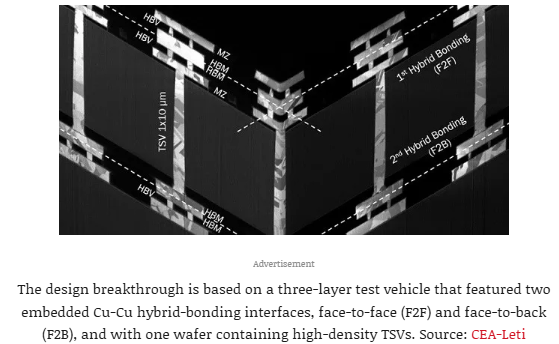

该设计突破基于混合键合和HD TSV技术的结合,有助于将图像传感器阵列、信号处理电路和存储元件等各种组件集成到图像传感器中,并具有精度和紧凑性。

在图像传感器设计中,不同层之间的通信需要先进的互连技术。CEA-Leti提出的新设计采用了混合键合,因为它在微米和亚微米范围内具有非常精细的间距。它还使用HD TSV,具有相似的密度,可以通过中间层传输信号。

该论文的主要作者Renan Bouis说:“混合键合和HD TSV技术的使用有助于缩短线长,这是提高3D堆叠架构性能的关键因素。”他的论文题为《高密度TSV在3层集成中的后侧减薄工艺开发》。他补充说,堆叠多个芯片来创建3D架构,例如三层成像仪,已经导致了传感器设计的范式转变。

本文介绍了制造3D多层智能成像仪所需的关键技术,这些成像仪能够解决需要嵌入式AI的新应用。CEA-Leti项目经理、IRT Nanoelec智能成像仪项目主管Eric Ollier表示:“这为展示功能齐全的三层智能CMOS图像传感器奠定了基础,该传感器具有边缘AI,能够解决高性能语义分割和目标检测应用。”

位于法国 Grenoble的研究机构CEA-Leti是同样位于法国 Grenoble的研发机构IRT Nanoelec的主要合作伙伴。

值得一提的是,在ECTC 2023上,CEA-Leti的科学家们报告了一辆两层测试车,该测试车采用F2B结构组装,结合了10 um高、1 um直径的HD TSV和高度可控的混合键合技术。现在,他们将HD TSV的高度缩短到6um,从而开发出具有低分散电气性能和更简单制造的两层测试车。

这主要是由于优化的减薄工艺,使基板厚度减少,具有良好的均匀性。这篇题为《3层CMOS图像传感器的低电阻和高隔离HD TSV》的论文的主要作者表示:“高度的降低导致电阻降低40%,与长度的减少成正比。”同时降低宽高比增加了隔离衬垫的台阶覆盖范围,从而提高了耐压性能。

CEA-Leti的科学家们相信,这种智能图像传感器技术将实现各种新的应用。

原文链接:

高端微信群介绍 | |

创业投资群 | AI、IOT、芯片创始人、投资人、分析师、券商 |

闪存群 | 覆盖5000多位全球华人闪存、存储芯片精英 |

云计算群 | 全闪存、软件定义存储SDS、超融合等公有云和私有云讨论 |

AI芯片群 | 讨论AI芯片和GPU、FPGA、CPU异构计算 |

5G群 | 物联网、5G芯片讨论 |

第三代半导体群 | 氮化镓、碳化硅等化合物半导体讨论 |

存储芯片群 | DRAM、NAND、3D XPoint等各类存储介质和主控讨论 |

汽车电子群 | MCU、电源、传感器等汽车电子讨论 |

光电器件群 | 光通信、激光器、ToF、AR、VCSEL等光电器件讨论 |

渠道群 | 存储和芯片产品报价、行情、渠道、供应链 |

< 长按识别二维码添加好友 >

加入上述群聊

带你走进万物存储、万物智能、

万物互联信息革命新时代