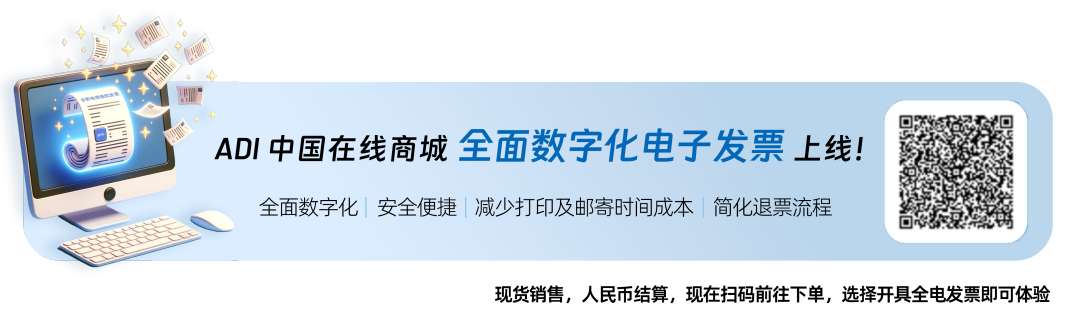

图1. 典型测量信号链

由于对超宽输入动态范围的需求增加,许多上述应用采用了最先进的高分辨率ADC。随着动态范围的增加,系统性能预计会提高,模拟调节链会减小,拥堵、能耗,甚至是材料成本都会下降。

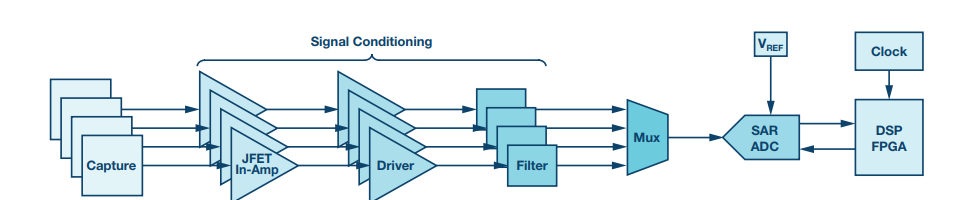

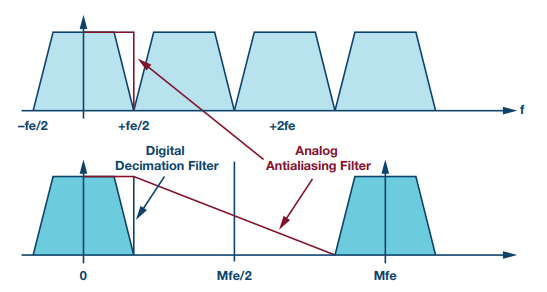

图2.通过添加数字抽取滤波器比较频谱噪声密度

以高于奈奎斯特定理要求的最小值的FSE速率对信号进行采样,可以通过处理和增加编码器的信噪比来执行增益运算,并因此增加有效位的数量。实际上,量化噪声和热噪声被同化为白噪声,该噪声在整个奈奎斯特频带及以外均匀分布。过采样之后,通过滤波和严格以最小所需采样速率(或2×BW)限制有用频带,频带每降低一个倍频程,噪声能量将降低3dB,如图2所示。换句话说,过采样因子为4时最为理想,在理论上使信噪比增加了6dB;即是说,增加了一位,如等式1所示:

图3.过采样分布在-3dB条件下截止频率与阻带起点之间的过渡带

相反,除LTC2512和LTC2500-32以外,大多数SAR ADC不包括数字滤波器,因此其运行不受一些不可避免的数字低通滤波的阻碍或限制,否则,就会在计算精度、带通纹波、衰减阻带抑制、传播时间和功耗之间进行平衡。在大多数情况下,用户无法控制这些∑-Δ转换器的内部滤波器系数值,不得不凑合了事。

LTC2378-20和AD4020的采样速率分别为1MSPS和1.8MSPS,为过采样带来了具有重要意义的可能性,特别是音频频段或更高频段。为此,必须在外部FPGA或DSP中搭载定制型抽取滤波器。如前所述,可以绕过后者,以在必要时将其延迟降至最低。基于这些初级采样速率值,考虑到0kHz至25kHz频段,相应的过采样因子约为16或32,处理增益为12dB至18dB,同时还严格按照奈奎斯特定理,简化了常规操作条件下的抗混叠低通滤波器。

故定义最大采样频率,其构成为:

其本身由输出数据的读取速率调理,其中,

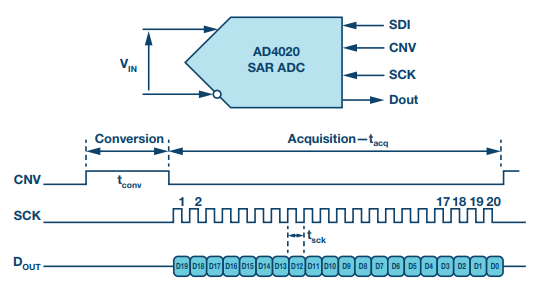

图4.AD4020的时序图

幸运的是,AD4020的转换时间超短,为325ns,采样速率为1MSPS,采样时间为675ns,基于此,其串行数据读取频率低于33MHz,与DSP同步串口(如SHARC®ADSP-21479)相当,功耗也非常低。

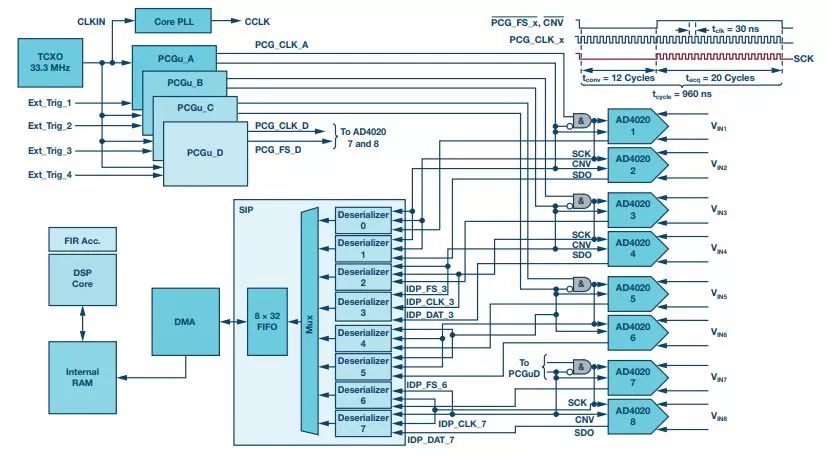

图5.通过解串行将8个20位1MSPSSAR ADC接入SHARC DSP;DMA数据传输进DSP内部RAM

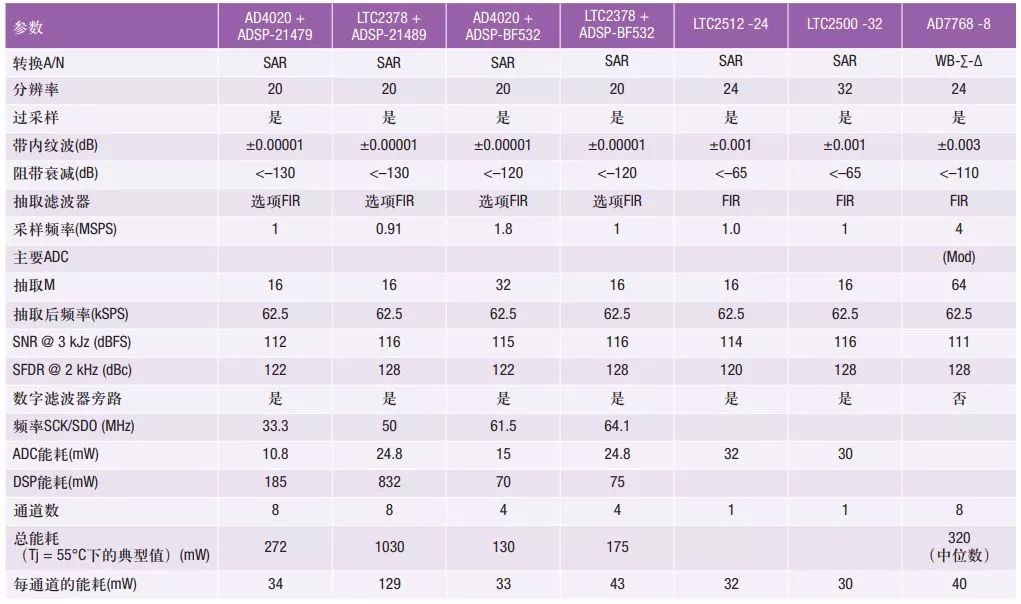

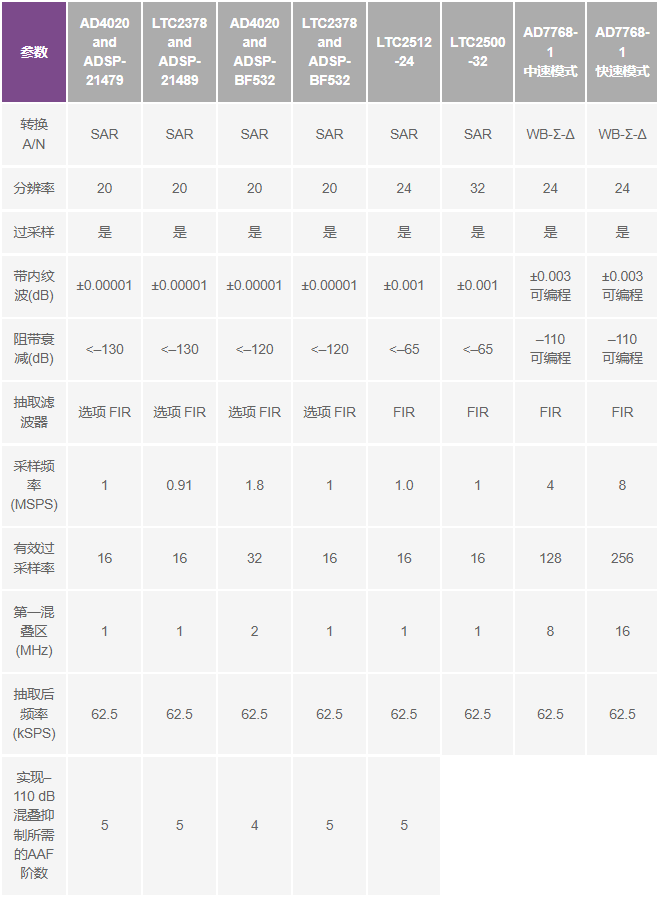

表1.不同SAR ADC与DSP相比的情况对比

同样,ADCLTC2378-20可以与ADSP-21489相关联,因为它能够在高达50MHz的外设时钟频率下工作,在这种情况下,采样速率为900kSPS,如表1所示。遗憾的是,静态电源电流(Iddint)或后者的泄漏电流远高于动态电流,使得该配置的总功耗超过可用功率,达到不可接受的程度。

抽取专用直接或优化FIR滤波器

级联多速率FIR滤波器(1/2频段)

多相FIR滤波器

无论是FIR还是IIR类型的多相滤波器都是抽取或插值滤波器最有效的实现方案之一。然而,传统数字处理方案要求在抽取之前进行滤波。在此假设下,1/M抽取滤波器由低通滤波器和紧随其后的采样频率降级组成(图6a)。预先对信号滤波,避免频谱混叠,然后以M-1的速率定期消除样本。然而,常规FIR或其他结构针对这些抽取滤波器的直接实现方案存在资源浪费问题,因为被拒样本是几十甚至几百次累乘(MAC)的结果。使用分解成若干滤波器组的多相滤波器或是针对抽取进行优化的滤波器,可以基于某些特点(如图6b所示)形成高效的滤波器。

图6a和6b.常规抽取滤波器和采用多相方案的抽取滤波器

支持IEEE-754定点或浮点32位算术格式„

有四个并行运行的累乘单元„

支持单速率和多速率处理模式(抽取或插值)„

一次简单迭代可以处理最多32个FIR滤波器,总共多达1024个系数

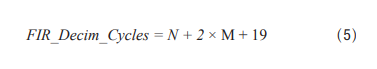

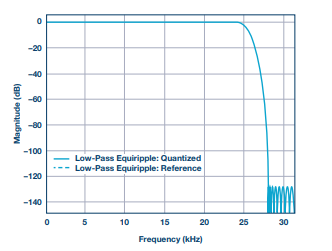

N为滤波器的系数的个数,M为抽取速率。

图7.抽取滤波器的滤波器响应

对于实时和DSP负载,滤波操作以62.5kSPS的频率重复,代表9,375,053个CCLK周期,而8个ADC转换通道的重复频率则略多于8倍,因为每个滤波器的存储器指针值都存储在SHARC数据地址生成器中,可以实现快速保存和恢复。这相当于,在SISD模式下,一个SHARCDSP为每秒8000万个执行周期(或80MIPS),在SIMD模式下,由于两个处理单元并行运行,则为该值的一半。在前述两种模式下,这8个抽取器FIR滤波器在执行时,分别以30%和15%的速率以及266MHz的时钟频率占用ADSP-21479。

表1. 不同SAR ADC与DSP相比的情况对比

👇点击探索ADI“芯”世界