前面设备树相关文章提到了重点要关注中断相关的内容,中断是最核心的部分,在调试其他外设驱动之前,先要调试好中断系统。

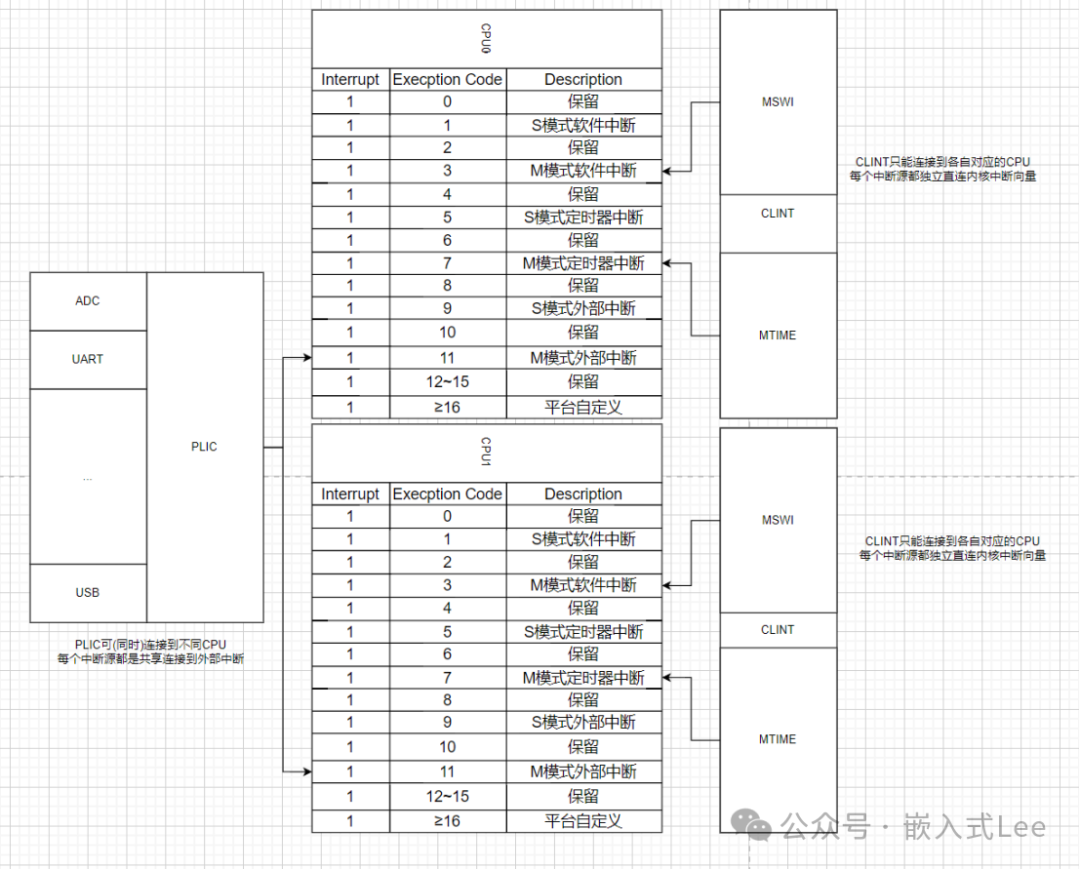

中断系统一般架构如下:CPU内核级中断/异常向量->中断控制器->各个设备中断。

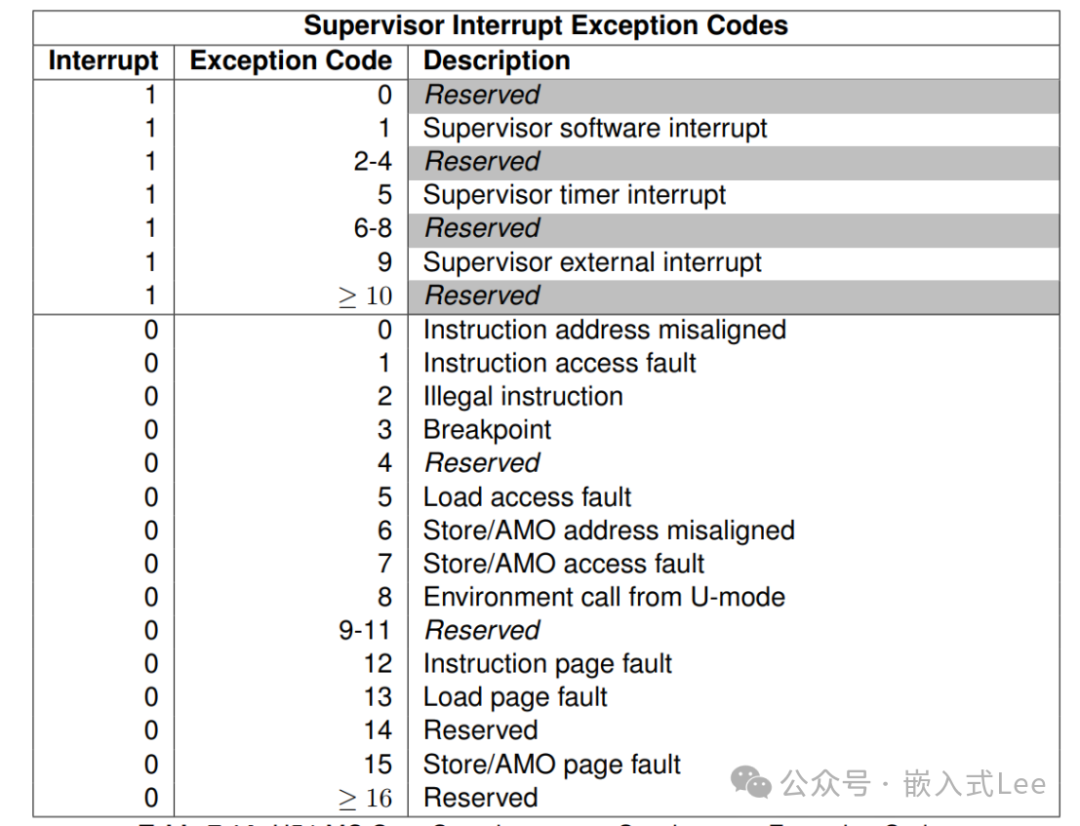

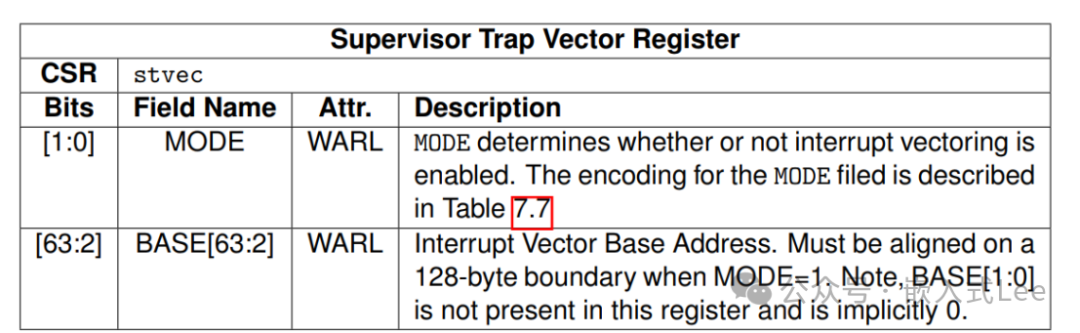

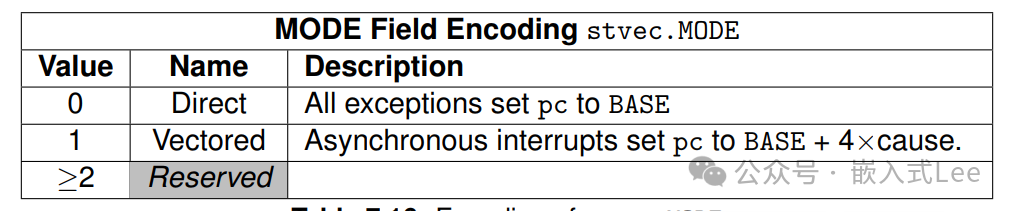

其中CPU内核级别中断/异常向量是RISCV标准定义好的,定义了有哪些中断和异常源,对应一个中断向量表。stvec和mtvec的低2位为0指定异常入口都走stvec/mtvec指定的地址(地址低两位始终为0)(固定地址模式),为1按照中断编号走stvec+i*4/stvec+i*4对应的地址(向量模式),linux代码中默认走的固定地址模式。在arch/riscv/kernel/head.S中以下代码,默认使用的是固定地址模式, .align 2表示2^2=4字节对齐,所以地址低两位为0.

.align 2

setup_trap_vector:

/* Set trap vector to exception handler */

la a0, handle_exception

csrw CSR_TVEC, a0

然后上述中断向量中引出S和M模式的外部中断(中断9和11),接下一级的中断控制器平台级中断控制器plic挂在其下,所有的平台级中断控制器中的中断都统一走这里,然后进入对应的驱动中进一步进行具体的设备中断处理。

RISCV中有个clint,核心本地中断的概念,提供定时器和软件中断直接映射到了内核中断向量,因为这两个功能是核心需要高效频繁使用的,这样更高效。

上面提到了plic和clint的概念,

Clint即Core Local Interruptor内核本地中断器,本地的意思是CPU内核独享的,即中断源只能接到对应一个CPU核心。

Plic即Platform-Level Interrupt Controller平台级中断控制器,平台级的意思是可整个平台共享的,即中断源可接到多个CPU核心。

整个拓扑逻辑示意如下:

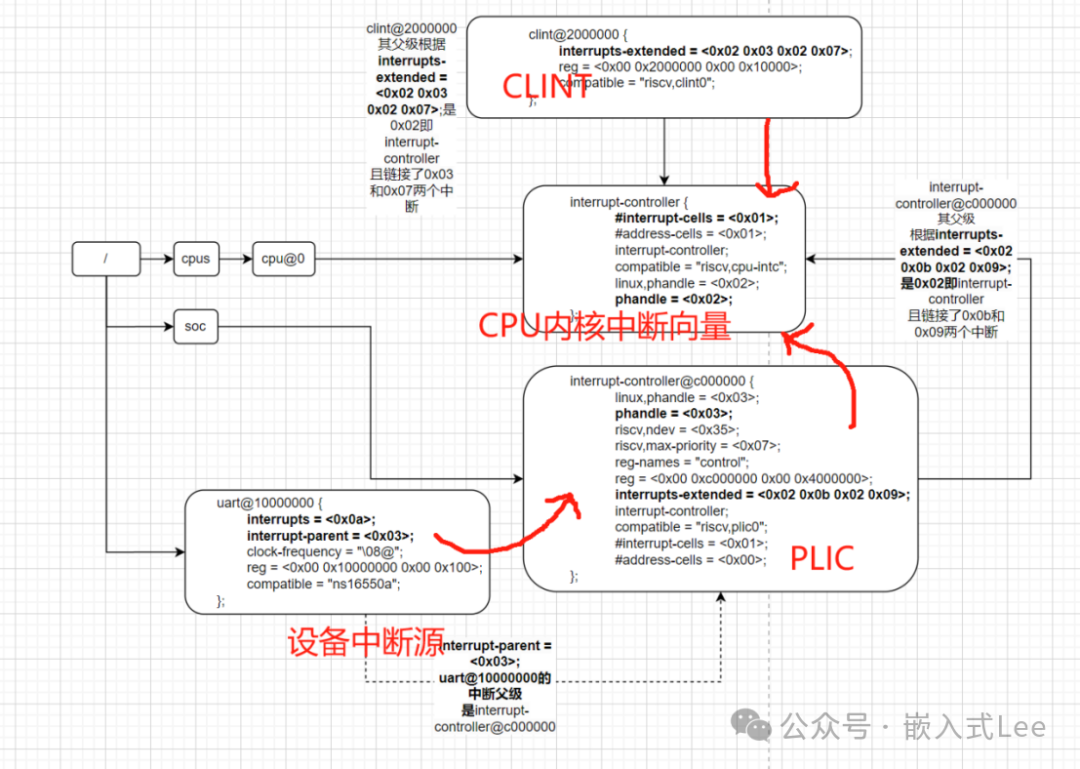

对应如下设备树的中断拓扑

当然中断控制器也是可以级联的,但是一般的系统不会有这么复杂,一般一个平台只有一个中断控制器供各CPU共享。

我们就分两篇来了解下CLINT和PLIC,为后面分析整个linux的中断系统做准备。

Linux代码中实现的plic驱动是兼容sifive,plic-1.0.0的中断控制器,其手册可以从https://static.dev.sifive.com/U54-MC-RVCoreIP.pdf下载,参考第8章。

CLINT由开始的CLINT发展为了最新规范的ACLINT,其实际就是提供了两个功能:

inter-processor interrupts IPI处理器间中断

Software interrupts SWI软件中断

这两个功能是核心紧耦合的,但是架构设计是可以模块化非紧耦合的。也就是设计是独立的中断控制器模块在内核之外,但是其各个中断源直接独立映射到内核的中断向量,这样可以高效响应。

最开始CLINT相关内容是分散在privileged规格书中的(1.0和之前), 直到1.1之后,单独形成ACLINT规范说明。

Core Local Interrupt (CLINT)核心本地中断器。最先是SiFive核心本地中断器(CLINT)设备在RISC-V中被广泛采用,以提供机器级IPI和定时器功能,可以参考SiFive U54-MC Core Complex Manual v1p0第9章,所以后面以该参考来说明。

SiFive CLINT的IPI和定时器功能寄存器映射是统一在一起的,且不提供supervisor-level IPI功能。ACLINT则改善了这两部分。

CLINT维护了与软件中断和定时器中断相关的,内存映射的控制和状态寄存器。这些寄存器映射到了CSR寄存器,可以直接使用csr指令访问,但是实际是内存映射的寄存器(参考特权级规格书的3.2 Machine-Level Memory-Mapped Registers)。

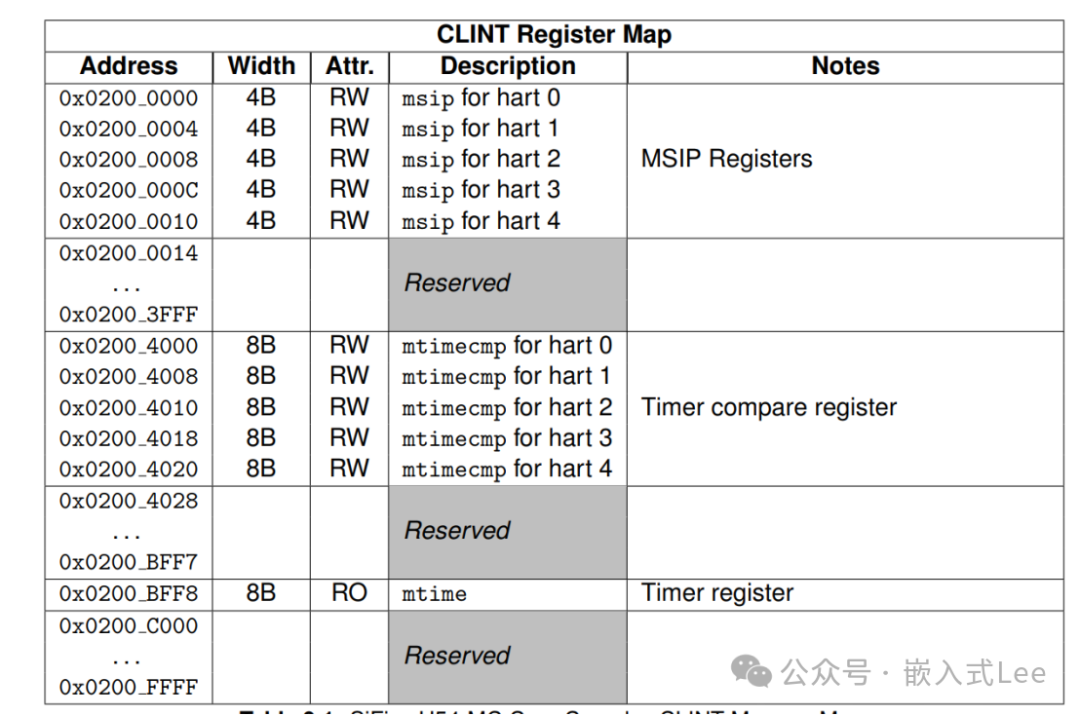

CLINT下只有3种寄存器

寄存器名字 | 偏移(字节) | 大小(位) | 复位值(hex) | 描述 |

msip |

| 32 | 0 | RW |

mtimecmp |

| 64 | 0 | RW写该寄存器清除定时器中断 |

mtime |

| 64 | 0 | RW |

在SiFive U54-MC Core Complex中寄存器布局如下,每个hart一个msip,每个hart一个mtimecmp,各核共用一个mtime。

MSIP

通过写入内存映射控制寄存器msip而产生机器模式软件中断。msip寄存器是一个32位宽的WARL寄存器,其中LSB反映在mip寄存器的msip位中。msip寄存器中的其他位被硬连线为零。复位时,msip寄存器被清零。

即写对应hart的MSIP寄存器的位0为1,触发该hart的机器级别软件中断,当然前提是要通过MIE.MSIP置位使能中断。此时该hart的MIP.MSIP为1表示中断挂起,.

软件中断对于多hart系统中的处理器间通信非常有用,因为hart可以写入彼此的msip位来实现处理器间中断。

MTIMECMP

mtime是一个64位读写寄存器,其计数频率由实现决定。只要mtime大于或等于mtimecmp寄存器中的值,计时器中断就会挂起, mip.mtip置位。当然前提是mie.mtip使能了。复位时mtime清零,mtimecmp未定义(SiFive U54-MC Core Complex中则不复位)。

写该寄存器清除中断(写的值要大于MTIME足够多,否则又很快产生中断了)。

MTIME

一个始终递增定时器,设计为64所以能够在足够精度下计数足够长时间而不会绕回。

所以每次产生定时器中断,都是将MTIMECMP在MTIME基础上增加一个时间间隔,用于指定定时器中断周期,而不是清除MTIME(看到这里实现是只读的)。

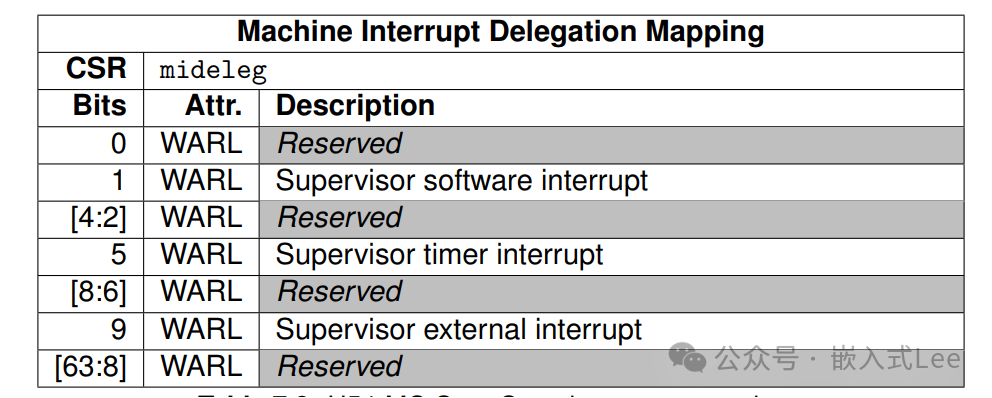

参考特权级规格书的章节3.1.8 Machine Trap Delegation Registers (medeleg and mideleg)。

默认情况下,所有trap都在机器模式下处理。机器模式软件可以通过在mideleg(委托中断)和medeleg(委托异常) CSR寄存器中设置相应的位,有选择地将中断和异常委托给S模式。

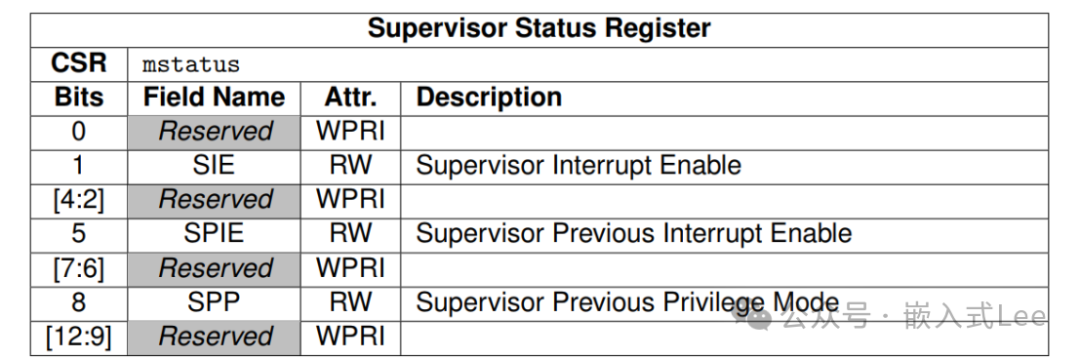

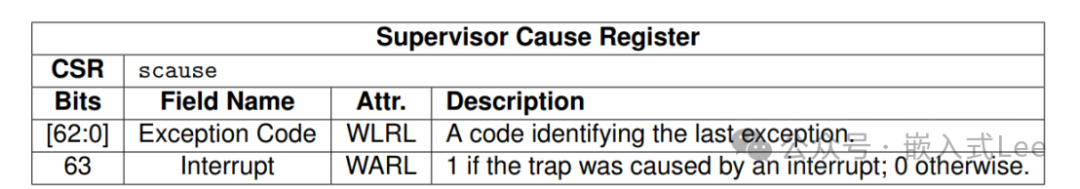

此时通过S模式寄存器sip,sie,scause,stvec来管理S中断。

机器模式软件还可以直接写入sip寄存器,有效地将中断挂到S模式。这对于定时器和软件中断特别有用,因为可能需要在机器模式和S模式下处理这些中断。

在采取委托trap后,mcause被复制到scause,mepc被复制到sepc,hart将在S模式下trap到stvec地址。

相关寄存器

ACLINT (Advanced Core Local Interruptor)高级核心本地中断器,规范定义了一组内存映射设备,用于为多HART(或多处理器)RISC-V平台的每个HART提供处理器间中断IPI(软件中断SWI)和定时功能。

相对CLINT,RISC-V ACLINT规范采用了一种更模块化的方法,为IPI和定时器功能定义了单独的内存映射设备。这种模块化设计允许RISC-V平台在某些场景时省略一些RISC-V ACLINT设备。除了模块化之外,RISC-V ACLINT规范还为supervisor-level IPI定义了一个专用的内存映射设备SSWI。

规格书见:https://github.com/riscv/riscv-aclint,最新版本是riscv-aclint-1.0-rc4.pdf

最开始这部分内容是分散在The RISC-V Instruction Set Manual Volume II: Privileged Architecture中的,后来把它单独拿出来了。可见官方的设计思路是不把aclic作为riscv内核的一部分,而是一个模块化的可定制组件,只要按照该规格书实现都可,方便模块化和自定义。这也是RISCV设计哲学的一个重要思想。之前是clint现在优化叫做aclint(Advanced Core Local Interruptor)。

ACLINT定义了以下3种设备

名字 | 特权级 | 功能 |

MTIMER | Machine | 固定频率计数和定时器事件 |

MSWI | Machine | 处理器间或者软件中断 |

SSWI | Supervisor | 处理器间或者软件中断 |

RISC-V ACLINT规范与原来的SiFive CLINT规范向后兼容。MTIMER和MSWI设备的寄存器定义和寄存器偏移量与SiFive CLINT规范定义的定时器和IPI寄存器兼容。RISC-V平台上的SiFive CLINT设备在逻辑上可以看作是一个MSWI设备和一个MTIMER设备,它们在内存地址空间中彼此相邻。

SiFive CLINT偏移范围 | ACLINT设备 | 功能 |

0x0000_0000 - 0x0000_3fff | MSWI | Machine-levelIPI/SWI |

0x0000_4000 - 0x0000_bfff | MTIMER | Machine-level固定频率计数和定时器事件 |

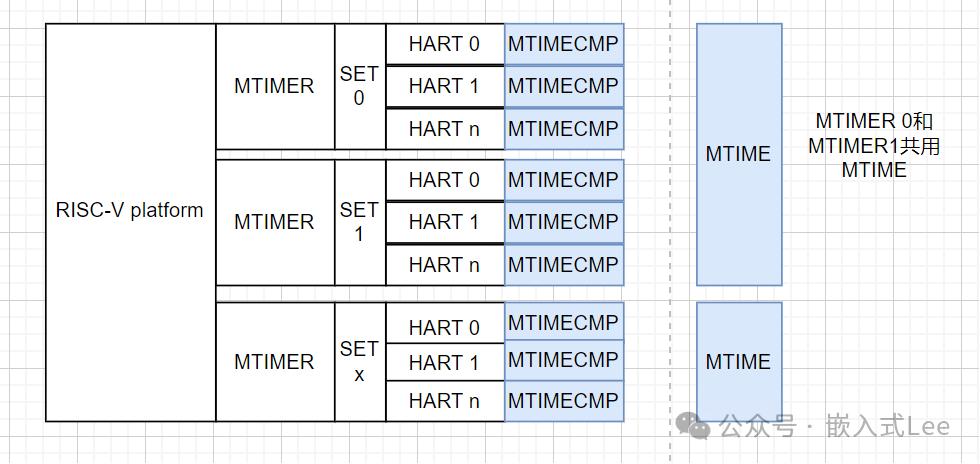

MTIMER设备为RISC-V平台上的一组HART提供机器级定时器功能,这一组HART共用一个固定频率单调递增的计数器(MTIME)寄存器。给连接到MTIMER设备的每个HART各提供一个时间比较寄存器(MTIMECMP)。未连接到任何HART的MTIMER设备只有MTIME寄存器,没有MTIMECMP寄存器。

一个RISCV平台可以有多个定时器设备。单个MTIMER设备支持的最大HART数量为4095,相当于MTIMECMP寄存器的最大数量是4095(下图的n)。

一个HART不能连接到不同的定时器设备上,也就是定时器设备下连接的HART不能相交。

定时器设备下连接的HART从0开始索引,这个索引可能和hart id有关也可无关。

多个定时器设备可以共享MTIME,但是各个HART的MTIMECMP必须和HART一一对应。

定时器设备下的MTIME和其下的MTIMECMP比较,而不能一个定时器设备下的MTIME和其他定时器设备下的MTIMECMP比较。

MTIMER设备有两个单独的地址空间:一个用于MTIME寄存器,另一个用于MTIMECMP寄存器,两者的基地址由实现决定。MTIME:MTIMECMP是1:多的关系。

MTIME寄存器

偏移 | 宽度 | 属性 | 名字 | 描述 |

0x0000_0000 | 8B | RW | MTIME | Machine-level定时计数寄存器,定时器复位时清零。计时频率由实现决定。 |

MTIMECMP寄存器

该区域地址大小是32760字节/8=4095个寄存器。

MTIME大于等于MTIMERCMP时产生中断(假设中断使能),反之中断清除。所以产生中断后写MTIMERCMP比MTIME大指定值,以设定下一次中断间隔。

偏移 | 宽度 | 属性 | 名字 | 描述 |

0x0000_0000 | 8B | RW | MTIMECMP0 | HART 0 machine-level定时器比较寄存器。 定时器复位时值不确定。 |

0x0000_0008 | 8B | RW | MTIMECMP1 | HART1 machine-level定时器比较寄存器 |

… | … | … | … | … |

0x0000_7FF0 | 8B | RW | MTIMECMP4094 | HART4094 machine-level定时器比较寄存器 |

RISC-V架构要求,所有MTIME寄存器相互之间以及所有HART time CSR相互之间都应能同步到一个MTIME tick偏差内。平台允许一个最大的MTIME tick偏差数,大于该偏差则要同步。

所有MTIME寄存器应具有相同的输入时钟,以避免各个MTIME寄存器(及其相关timeCSR)之间的运行时漂移。

系统复位后,硬件必须初始化所有MTIME寄存器并将其同步为零。

当MTIMER设备因电源管理操作而停止并再次启动时,软件应将此MTIME寄存器与所有其他MTIME寄存器重新同步。

软件使用RISC-V 64位汇编序列来同步MTIME寄存器与另一个MTIME寄存器的示例:

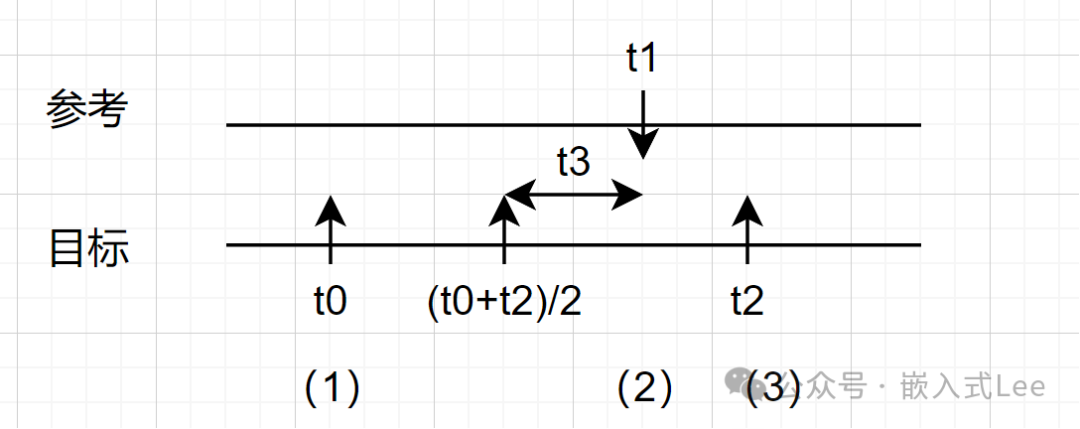

可能需要重复同步几次,直到目标MTIME寄存器和参考MTIME寄存器之间的增量为零(或非常接近零)。

/** unsigned long aclint_mtime_sync(unsigned long target_mtime_address,* unsigned long reference_mtime_address)*/.globl aclint_mtime_sync aclint_mtime_sync:/* Read target MTIME register in T0 register */ld t0, (a0)fence i, i/* Read reference MTIME register in T1 register */ld t1, (a1)fence i, i/* Read target MTIME register in T2 register */ld t2, (a0)fence i, i/** Compute target MTIME adjustment in T3 register* T3 = T1 - ((T0 + T2) / 2)*/srli t0, t0, 1srli t2, t2, 1add t3, t0, t2sub t3, t1, t3/* Update target MTIME register */ld t4, (a0)add t4, t4, t3sd t4, (a0)/* Return MTIME adjustment value */add a0, t3, zeroret

该算法的示意如下

(1)先读目标t0,(2)再读参考t1,(3)再读目标t2

要比较参考和目标的偏差,理论上必须要同一时刻读两者的MTIME,这个软件上做不到,那么怎么办呢? (1)(2)(3)按顺序读,那么(2)是在(1)(3)的中间的(具体中间多少是不确定的),以(1)和(3)的正中间作为和(2)是同一时刻, 这个作为不是准确的,因为(1)(2),(2)(3)之间时间不一定一样,即(2)不一定在正中间,但是可以重复调整多次则统计意义上等效于平均在中间。

所t1-(t0+t2)/2即认为是等效的偏差,目标值加上这个偏差即可。

问题?既然各个MTIME需要同步,为什么不就用一个MTIME呢,即各个SET都使用一个MTIME?猜测一个原因可能是功耗管理,需要开关时钟,即一些场景只有部分SET在运行要关闭其他SET。那么为什么是以SET为单位,而不是每个HART一个MTIME呢,这就是颗粒度综合考虑了,每个HART对应一个MTIME虽然功耗管理更精细但是资源消耗更多,一个权衡的取舍问题罢了。

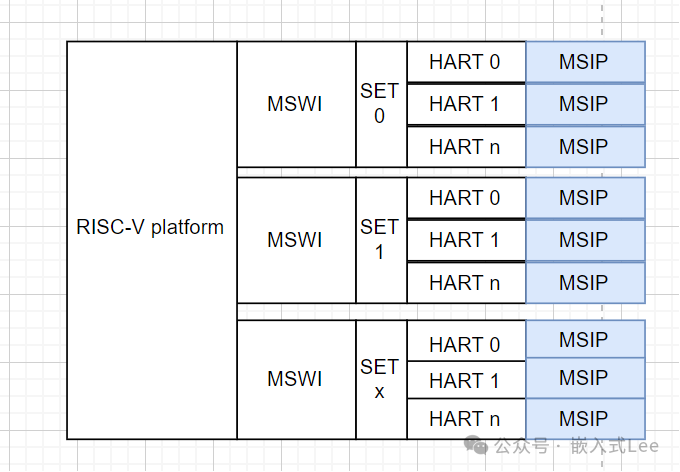

MSWI设备为RISC-V平台上的一组HART提供机器级IPI功能。连接到MSWI设备的每个HART都有一个IPI寄存器(MSIP)。

RISC-V平台可以有多个MSWI设备,每个MSWI设备为不同(不相交)的一组HART提供机器级IPI功能。MSWI设备为与其关联的每个HART分配一个从零开始的HART索引。该索引可能与hart id有关也可无关。

单个MSWI设备支持的HART的最大数量为4095,相当于MSIP寄存器的最大个数是4095(下图的n)。

基地址实现决定,寄存器复位值为0

每个MSIP寄存器都是一个32位宽的WARL寄存器,其中高31位被连接到零。最低有效位反映在CSR寄存器MIP.MSIP中。分别向相应的MSIP寄存器写入1来触发对应HART的软件中断,写0来清除中断。

偏移 | 宽度 | 属性 | 名字 | Description |

0x0000_0000 | 4B | RW | MSIP0 | HART 0 machine-level IPI 寄存器 |

0x0000_0004 | 4B | RW | MSIP1 | HART 1 machine-level IPI 寄存器 |

… | … | … | … | … |

0x0000_3FFC | 4B | RESERVED | 保留 |

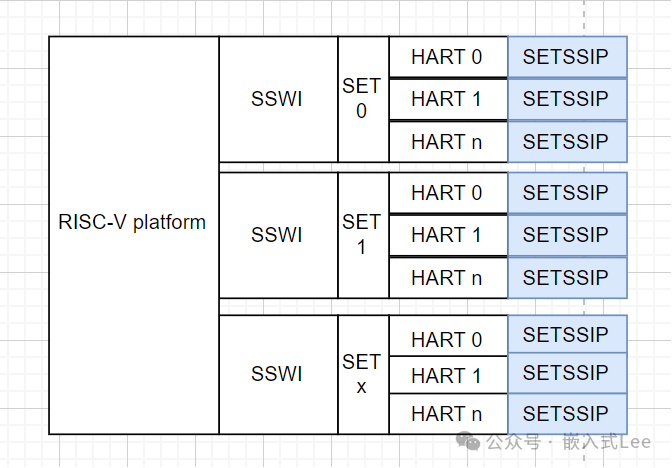

SSWI设备为RISC-V平台上的一组HART提供Supervisor-level IPI功能。为连接到SSWI设备的每个HART提供了设置IPI(SETSSIP)寄存器。

RISC-V平台上可以有多个SSWI设备,每个SSWI设备为不同(或不相交)的一组HART提供Supervisor-level IPI功能。SSWI设备为与之关联的每个HART分配一个从零开始的HART索引。该索引可能与hart id有关或者无关。

单个SSWI设备支持的最大HART数量为4095,相当于SETSSIP寄存器最多4095个。

偏移 | 宽度 | 属性 | 名字 | 描述 |

0x0000_0000 | 4B | RW | SETSSIP0 | HART 0设置supervisor-level IPI寄存器 |

0x0000_0004 | 4B | RW | SETSSIP1 | HART 1设置supervisor-level IPI寄存器 |

… | … | … | … | … |

0x0000_3FFC | 4B | RESERVED | 保留 |

每个SETSSIP寄存器都是一个32位宽的WARL寄存器,其中高31位被连接到零。SETSSIP寄存器的最低有效位始终为0。将0写入SETSSIP寄存器的最低有效位没有效果,而将1写入最低有效位会向相应的HART发送边沿敏感中断信号,使对应HART的 CSR寄存器的mip.SSIP置位产生中断。对SETSSIP寄存器的写入保证会反映在对应HART的mip.SSIP中,但不一定立即反映出来。

RISC-V特权架构将CSR寄存器中mip和sip的SSIP位定义为可写位,因此M模式或S模式软件可以直接清除SSIP中断。

drivers/clocksource/timer-clint.c

需要配置CONFIG_CLINT_TIMER,Kconfig配置只在不支持MMU的RISC-V处理器上运行M-mode Linux的环境中使能,S模式LINUX不走该驱动,

而是走的drivers/clocksource/timer-riscv.c

需要配置CONFIG_RISCV_TIMER

会通过ecall调用sbi接口,因为S模式不能直接访问mtimecmp这些寄存器,通过ecall调用来实现。