动动手指,关注公众号并加星标哦

(1)

今天终于把运放的设计系列视频,给理顺了。

虽然还有疑问,然后还没上仿真软件验证,但是起码熟悉程度大大增加了要是有朋友对这个设计视频感兴趣的话,就去瞄一眼这篇文章的留言运放设计视频,看了3遍了,还是没内化成自己的:(。

边熟悉边记录,也慢慢形成了一个文档,目前心里预期,针对运放设计,能从理论推算,到原理图仿真验证,再到版图仿真验证,都能走一遍。

(2)

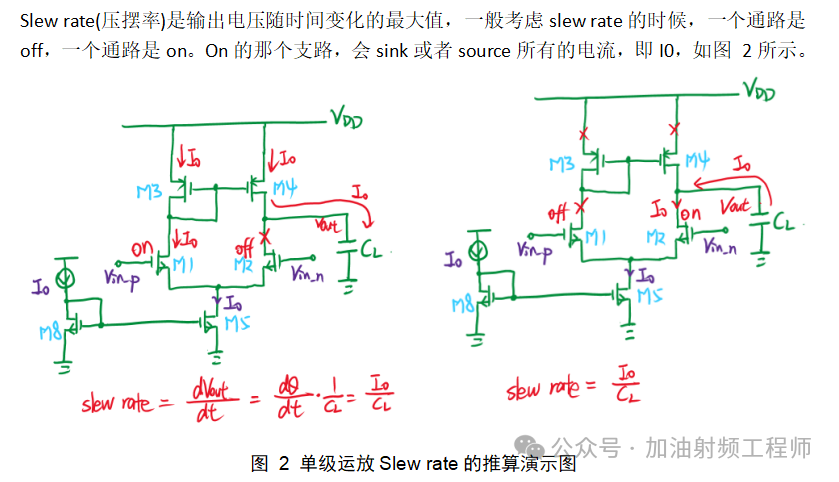

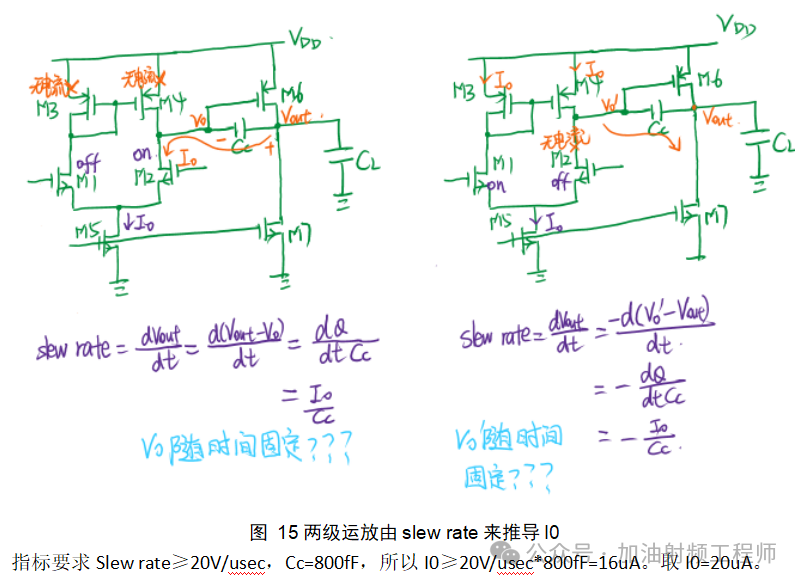

视频中运放设计时的理论推算,基本都是从slew rate开始的。因为slew rate和电流I0相关,而后面管子尺寸的计算基本都是基于这个I0。

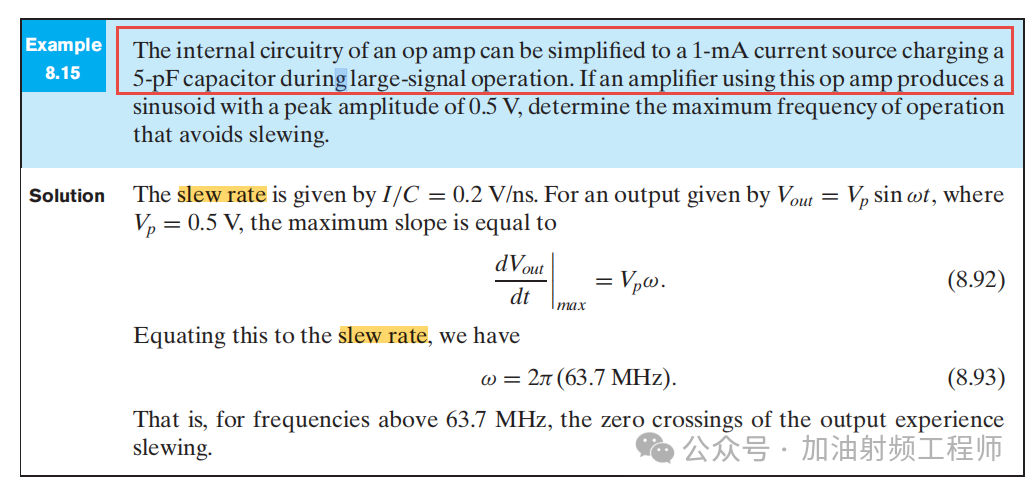

razavi在微电子基础中的Example 8.15有讲到,在大信号的情况下,运放可以看成一个电流源对电容进行充放电。

视频中讲解运放设计,由slew rate推导出I0时,也确实是这样,都是基于恒电流对电容的充放电。

只是说单级运放和两级运放设计时,充放电的电容不一样,一个是CL,一个是Cc。

对于单级运放的slew rate,我基本没有疑问;但是对于两级运放的slew rate,着实想不太明白。

视频中,是直接给出了I0/Cc这样一个结论。不过严谨起见,我不得不说,也有可能是因为那个印式英语基本听不懂,然后那个视频还正好字幕不能显示,然后错过了up主的解释。

和号友探讨了一下,他说,当M2 on的时候,V0基本被拉到地了;当M2 off的时候,V0基本被拉到VDD了。

不过号友的说法,我也还没有想通,形成闭环。

(3)

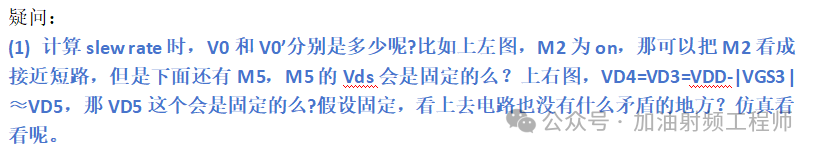

上面讲的是芯片的slew rate指标对芯片设计的影响;接下来,就聊聊芯片的slew rate对板级信号的影响。

如下图所示,当运放是理想运放的时候,输出完全跟上输入,就差一个比列关系;但是当运放的slew rate小于dVout/dt|max时,输出就有时候会跟不上输出,即当输出的斜率高于运放的slew rate时,运放就不能完全响应了,即输出信号就产生了失真。

参考文献:razavi,Fundamentals of Microelectronics

完结接收机课程吆喝处哈(已在平台上购买的同学,加我微信,领课件资料哈!)

想报名的同学,可以海报底部扫码哈!

想了解射频系统的同学,可以添加我的微信RF606yuer,备注:射频系统书籍,可以领取37本关于射频系统的书籍。

☜左右滑动查看更多

Slide for more photos