MIPI是什么意思? MIPI是什么接口?

MIPI全称为:Mobile Industry Processor Interface,由MIPI联盟开发,是一种高性能、低功耗、低成本的串行通信接口,目的是把设备内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少设备设计的复杂程度和增加设计灵活性。统一接口标准的好处是厂商可根据需要灵活选择不同的芯片和模组,更改设计和功能非常快捷方便,MIPI主要用于移动设备和嵌入式设备中,比如手机、电脑、车载娱乐系统、可穿戴设备及物联网(IoT)设备等。

MIPI Alliance即移动产业处理器接口联盟(Mobile Industry Processor Interface 简称MIPI)。于2003 年由ARM,Nokia,ST,TI 等公司成立的为移动应用处理器制定的开放标准和一个规范,目前MIPI已经成为移动领域最主流的视频传输接口规范,应用最广泛的是MIPI D-PHY和MIPI C-PHY两组协议簇,C-PHY中的许多模块借鉴于D-PHY,两种标准的接口可共用相同引脚实现双模。

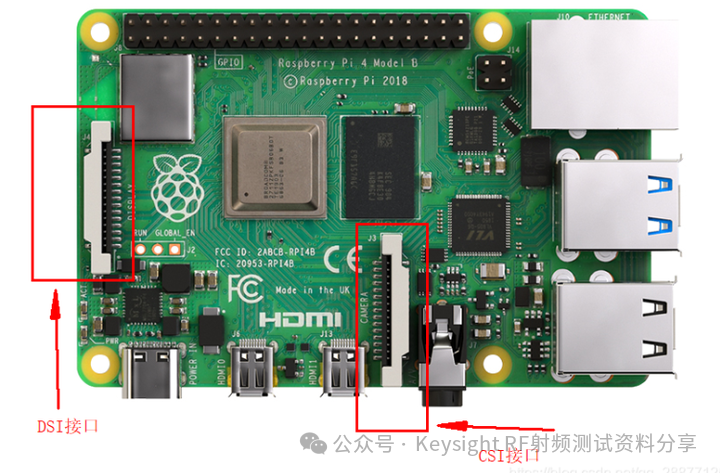

MIPI接口图片

MIPI接口图片

MIPI接口具有什么优势?

MIPI接口具有以下优势:

高速数据传输:MIPi接口支持高速数据传输,最高可达数Gbps,满足移动设备对高分辨率、高刷新率显示的需求。

低功耗:MIPi接口采用低电压信号,降低功耗,延长移动设备的续航时间。

灵活性:MIPi接口支持多种数据通道和时钟频率,可以根据不同的应用场景进行配置。

兼容性:MIPi接口具有很好的兼容性,可以支持多种类型的显示设备和摄像头设备。

MIPI有哪些接口协议?

MIPI名词解释

DCS (Display Command Set):DCS是一个标准化的命令集,用于命令模式的显示模组。

DSI, CSI(Display Serial Interface, Camera Serial Interface)

DSI 定义了一个位于处理器和显示模组之间的高速串行接口。

CSI 定义了一个位于处理器和摄像模组之间的高速串行接口。

D-PHY:提供DSI和CSI的物理层定义

CSI概述

CSI协议分为三层:

1.应用层(Application Layer),主要描述了上层数据流中的数据编码和解析。CSI-2 规范中规定了像素数据到字节的映射(Mappingof pixel values to bytes)。

2.协议层(Protocol Layer),包含了几个不同的子层,每个子层都有各自的明确职责。主要包括,像素/字节打包/解包层(Pixel/Byte Packing/Unpacking Layer),Low Level Protocol Layer(LLP),通道管理(LaneManagement)层。

3.物理层(PHY Layer),定义了传输介质 (electrical conductors,导体),输入/输出电路信号的电气特性(electricalparameters)和时钟机制(时序)。即如何从串行位流(Bit Stream)中获取“0”和“1”信号。规范中的这一部分记录了传输介质的特性,并依据时钟和数据通道之间发信号和产生时钟的关系规定了电学参数。

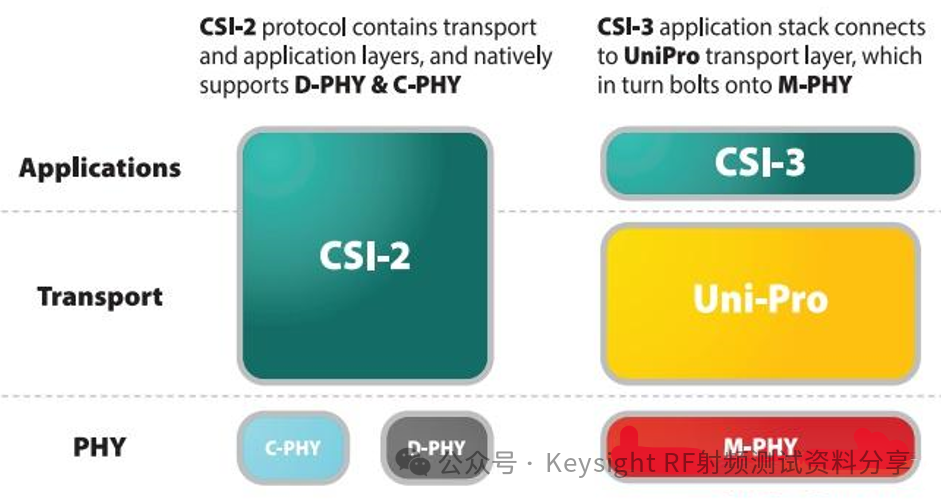

CSI分为CSI2和CSI3。他们的组成如下图:

DSI概述

DSI全称Display Serial Interface,主要用于显示模块的一个接口,它基于MIPI协议而产生,基于MIPI协议的还有CSI (camera serial interface), DBI(display bus interface), DPI(display pixel interface)。相对于一般的RGB接口,DSI有成本低,高速率的优势。

如下为简单的主机与显示模块的连接图:

DSI分四层,对应D-PHY、DSI、DCS规范、分层结构如下:

PHY 定义了传输媒介,输入/输出电路和和时钟和信号机制。

Lane Management层:发送和收集数据流到每条lane。

Low Level Protocol层:定义了如何组帧和解析以及错误检测等。

Application层:描述高层编码和解析数据流。

DSI的模式

Command Mode

Video Mode

Video mode表示无论当前显示是否有数据更新,DSI host端一直送数据给panel显示。Command mode表示只要当数据画面有变化时,DSI host端才送数据给panel显示。

MIPI应用场景 - 移动通信的内部接口。

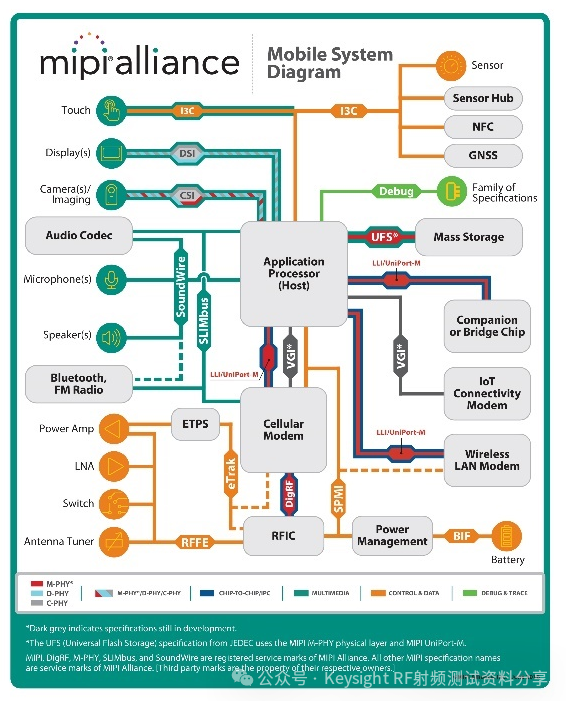

下图是MIPI系统框图和多媒体规范:

图:MIPI系统框架

图:MIPI系统框架

源自MIPI Alliance官网

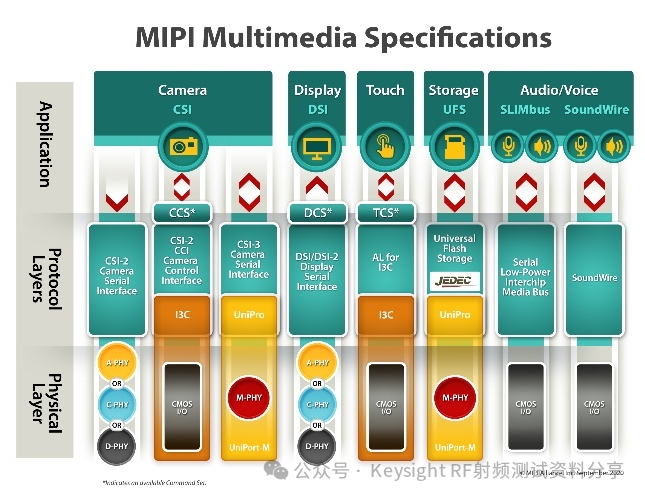

图:MIPI多媒体规范

图:MIPI多媒体规范

扫描二维码推荐应用指南:如何使用 ParBERT 表征 MIPI D-PHY?

“了解 MIPI D-PHY 标准、如何使用 ParBERT 强调 MIPI D-PHY 接收器以及通道在操作过程中如何在两种模式之间切换。”

MIPI接口多少引脚?

MIP接口作为移动设备中的通用接口,为连接摄像头、显示器、传感器等设备提供了更多的选择和灵活性。在MIPl接口中,D-PHY和C-PHY是主要的接口协议,它们有着不同的引脚定义和功能,如时钟信号、高速/低速数据线等。除此之外,MIPI CSI-2、MIPIDSI MIPIRFFE、 MIP1 13C等协议也在不断的发展和更新中,为移动设备提供更多的功能和新的技术优化。

MIPI接口引脚定义

在MIPl接口中,具有不同功能的引脚有不同的标签和定义,以下是MIPl接口中常见的引脚定义:

1.D-PHY接口定义

D-PHY是MIP!总线的物理层,用于在发送和接收设备之间传输数据。D-PHY总共有19根线,其中16根是数据传输线。下面是D-PHY接口中的引脚定义:

CLOCK:时钟信号,用于同步序列化和反序列化的数据

HS-Data0~15:高速数据线,可传输16位高速数据。正常情况下,只使用其中几条高速数据线。

LP-Data0~2:低功耗数据线,可传输1至3位的低速数据。

Lane 0~3:高速和低速数据线的组合。每组包括1条高速数据线和1至了条低速数据线。

ULPS CLK: Ultra Low Power State 时钟信号,用于设备进入低功耗状态

ULPS DATA: Ultra Low Power State 数据线

2.C-PHY接口定义

C-PHY是MIPI总线的新一代接口,支持更高的数据传输速率和更节能的设计。与D-PHY不同,C-PHY共有22个引脚,其中4个是时钟引1脚。下面是C-PHY接口中的引脚定义:

CLKIN:输入时钟,用于指定时序。通常采用LVCMOs电平.

CLKOUT:输出时钟,用于与接收设备对齐数据:

Lane 0+:高速串行数据线

Lane 0-:高速串行数据线

Lane 1+:高速串行数据线

Lane 1-:高速串行数据线

Lane 2+:高速串行数据线

Lane 2-:高速串行数据线

Lane 3+:高速串行数据线

Lane 3-:高速串行数据线

ANA OUTP:表示输出端为模拟信号

ANA OUTN:表示输出端为模拟信号

ANA INP:表示输入端为模拟信号

ANA INN:表示输入端为模拟信号

REG OUT:用于根据硬件内存检查中的读或写信号进行寄存器读取/写入。

REG IN:用于根据硬件内存检查中的读或写信号进行寄存器读取/写入。

LPDTI:低速数据传输接口

LPDTI 1P5V:低速数据传输接口1.5V电压级别

LPDTI GND:地线

ULPMIPI CLK: 用于设备进入Ultra Low Power Mode的时钟信号

ULPMIPI DATA:用于设备进入Uitra Low Power Mode的数据信号

而MIPI技术是分层的包括物理层、协议层和应用层,相同的PHY物理层可以承载不同协议。

MIPI D-PHY技术概览

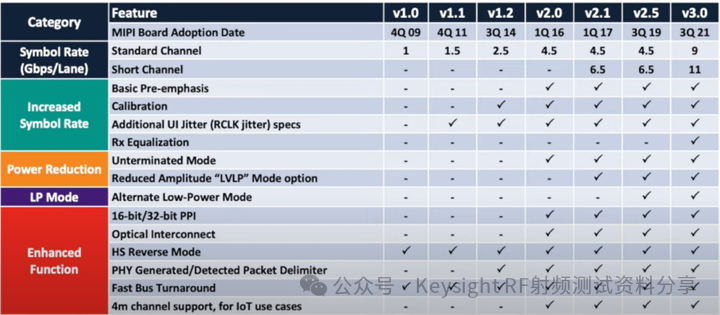

图:摘自MIPI Alliance

图:摘自MIPI Alliance

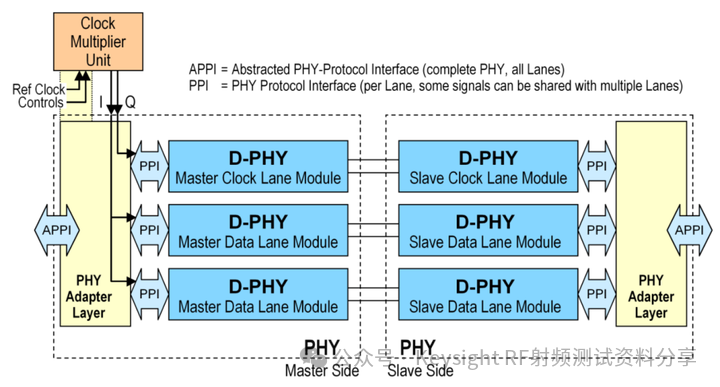

D-PHY实现了Camera/Display(摄像头/显示屏)与AP(应用处理器)之间的互连,具备高速、低功耗、低成本等特点,不仅适合移动应用,也适合IoT。D-PHY提供了主从间源同步MIPI接口,包含1对单向差分时钟,支持SSC、1~4对单向或双向差分数据线。数据传输采用DDR方式,即在时钟的上下边沿都有数据传输,下图是D-PHY 双数据通道 PHY 配置:

图 D-PHY 双数据通道 PHY 配置

图 D-PHY 双数据通道 PHY 配置

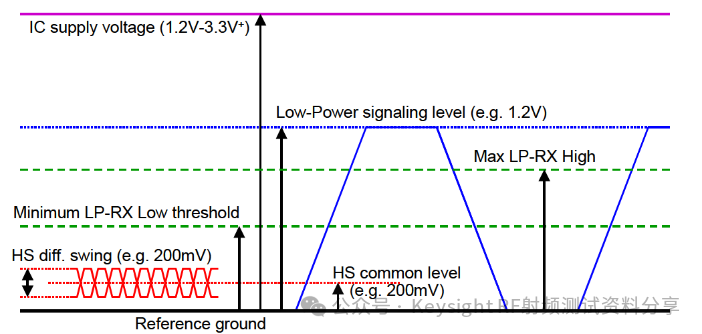

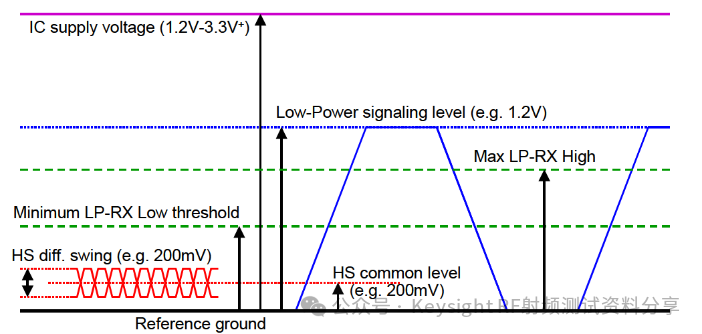

D-PHY 的物理层支持高速HS(High Speed)和低功率 LP(Low Power)两种工作模式。

HS(High Speed)模式下采用低压差分信号,有端接,可以传输很高的数据速率(数据速率为 80M~1.5Gbps/without skew cal、1.5G~2.5Gbps/with deskew cal、2.5G~9G/with equalization)。

LP(Low Power)模式下采用单端信号,未端接,数据速率很低(<=10Mbps),但是相应的功耗也很低,考虑EMI,产生的信号slew-rate及驱动电流受到限制。可选支持的交替低功耗模式采用有端接的低压差分信号,数据速率最低前向4Mbps,反向最低1Mbps,最高与HS速率保持一致。

高速HS(High Speed)和低功率 LP(Low Power)两种模式的结合保证了 MIPI总线在需要传输大量数据(如图像)时可以高速传输,而在不需要大数据量传输时又能够减少功耗。

下图5是高速HS和低功率LP模式下的信号电平示意图。

下图6是用示波器捕获的MIPI D-PHY信号,可以清楚地看到HS高速信号和LP低功率信号。

图5:HS高速和低功率LP模式下的信号电平

图5:HS高速和低功率LP模式下的信号电平

图6:示波器捕获的MIPI D-PHY信号

图6:示波器捕获的MIPI D-PHY信号

扫描二维码推荐应用指南: MIPI M-PHY 发射机验证的示波器注意事项

“了解 Keysight 示波器中的 M-PHY 协议解码功能如何调试信号完整性问题,从而加速多通道 MIPI M-PHY 设计验证。”

虽然MIPI D-PHY 的板级设计简单,但是MIPI芯片的内部架构、I/O技术非常复杂。

MIPI芯片复杂体现在如下几个方面:

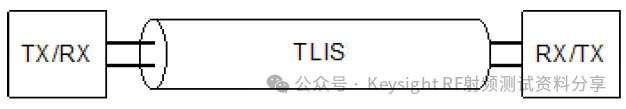

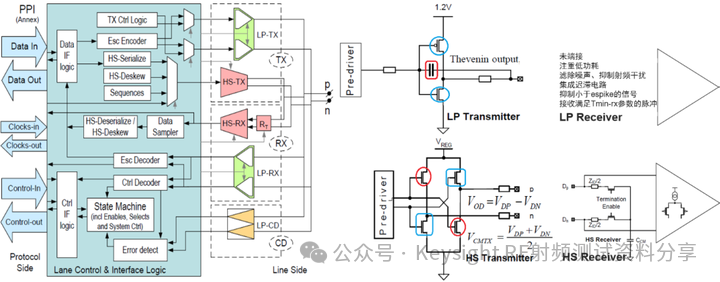

1)MIPI通信架构包含发送(通常是master)、接收(通常是slave)及互连通道。

2)MIPI芯片通道类型包括时钟通道、单向数据通道及双向数据通道。收发通道模块包括线路接口、控制/接口逻辑及协议接口。控制/接口逻辑可实现Escape mode encoder这与LP-TX相关、HS-Deskew、Sequences这与HS-TX相关、HS-RX可以实现数据采集、HS-Deskew,LP-RX可实现控制模式下的解码与Escape模式下的解码,LP-CD用于双向数据通道可实现冲突/竞争检测。

电气层面涉及Slew-Rate受控的推挽电路实现的LP-TX,高速低压差分驱动电路实现的HS-TX(可选支持半摆幅模式以实现节电/速率超过2.5Gbps需要2taps的去加重实现2种选择克服ISI影响),高速差分接收电路实现的HS-RX(可使能ZID阻抗),另外LP-RX电路注重低功耗,需要集成迟滞功能降低对噪声的灵敏等。

图:收发内部组成和电气实现

图:收发内部组成和电气实现

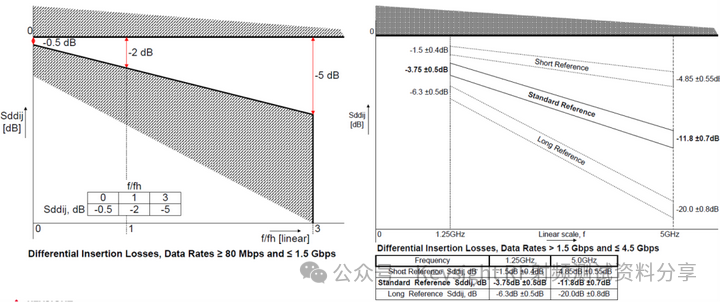

3)TLIS传输线互连架构支持不同传输“距离”,如下展示了不同速率插损模板,在1.5Gbps~4.5Gbps速率是默认支持Standard Reference channel,可选支持Long Reference Channel

图:互连插损模板

图:互连插损模板

MIPI测试是什么?

MIPI测试是针对MIPI接口的测试,主要目的是验证该接口是否符合MIPI规范,确保其电气特性、协议一致性、定时和同步机制等方面的性能符合标准。

MIPI测试的具体内容包括:

电气特性:测试电压电平、信号方案、上升/下降时间等电气参数是否符合规定标准,确保信号完整性。

协议一致性:验证接口是否正确处理数据包成帧、错误检测和纠正、控制信号处理和电源管理等操作。

定时和同步:检查接口是否在规定的定时要求内准确生成和接收控制信号、时钟信号和数据信号,确保设备间的协调和数据完整性。

错误检测和处理:验证接口的错误检测和处理能力,确保在传输过程中保持数据完整性。

电源管理:评估接口的电源管理功能,确保低功耗信令模式和省电技术的正确实现。

正是由于复杂内部组成和电气架构,因此要保证MIPI接口信号的互通性需要很复杂的测试。MIPI Alliance开发了conformace测试套件(CTS),其目的是优化基于MIPI Spec的产品的互通性。它考察的是物理层功能(不是性能)和compliance test (项目都要通过)有区别,互通性测试通过项目越多,越让开发者自信,以此表明产品可以在许多MIPI的使用环境中正常工作。

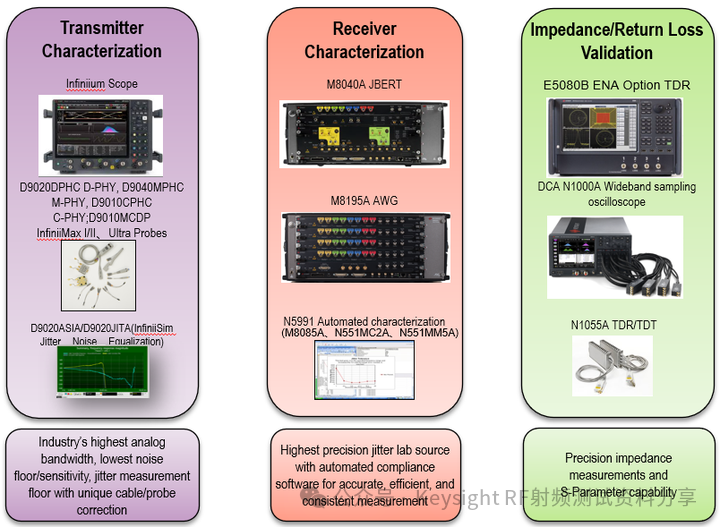

以物理层测试为例,发射机测试主要基于示波器,接收机测试基于高速任意波形发生器;而借助自动化的协议分析及解码软件,可以极大的提高debug和测试效率,下面我們会详细介绍物理层测试。

MIPI一致性测试的内容包括哪些?

MIPI一致性测试是确保产品符合MIPI标准的关键环节,涉及物理层、数据链路层和应用层测试。通过测试可以提高产品的稳定性和可靠性,降低成本,并获得MIPI联盟认证。随着移动设备和消费电子产品的快速发展,MIPI一致性测试的作用将更加重要。

在移动设备和消费电子产品的快速发展中,MIPI(Mobile Industry Processor Interface)作为一种高效、低功耗的接口标准,已经得到了广泛应用。MIPI一致性测试是确保产品符合MIPI标准,实现高性能、低功耗通信的重要环节。

MIPI一致性测试主要包括以下几个方面:

物理层测试:验证接口的物理特性,如电压、电流、阻抗等,确保设备在物理层面上满足MIPI标准。

数据链路层测试:验证数据在传输过程中的正确性和稳定性,包括数据传输速率、误码率、同步和异步通信等。

应用层测试:验证设备在应用层面上对MIPI协议的支持程度,如设备驱动程序、操作系统支持等。

MIPI D-PHY物理层

CTS测试

MIPI D-PHY物理层测试主要涉及的测试项目包括(根据mipi_D-PHY-v2-1_CTS_v1-0):

• TX Timers and Signaling

• RX Timers and Electrical Tolerances

• Interface Impedance and S-Parameters

其中,发射机测试基于示波器和自动化测试软件完成,接收机测试基于高速任意波形发生器完成,S参数涉及阻抗测试基于网络仪或TDR完成,如下图总结:

图:MIPI D-PHY物理层测试方案总结

图:MIPI D-PHY物理层测试方案总结

MIPI D-PHY发射机测试概览

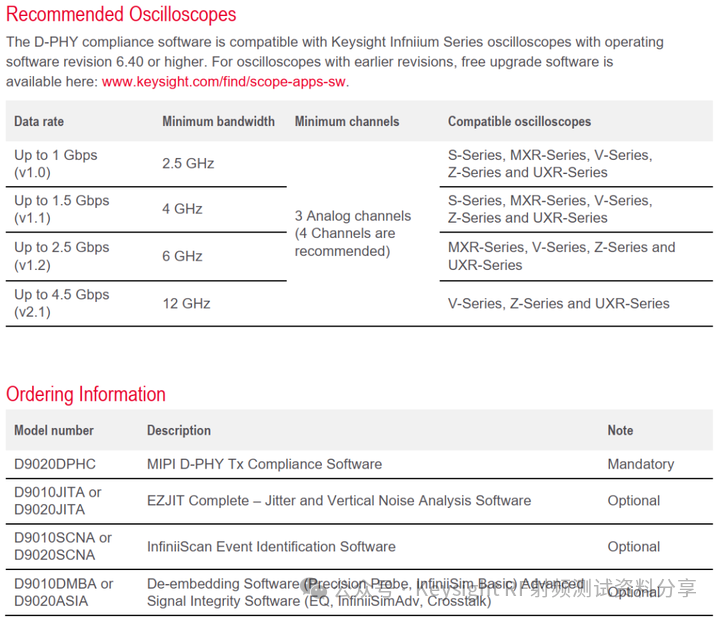

TX发射机测试主要基于示波器和自动化软件完成,根据MIPI D-PHY各版本的速率及规格参数需要选择合适带宽的示波器,按照MIPI 协会的要求,针对不同速率的MIPI版本示波器带宽及选用的自动化测试软件如下:

图:MIPI D-PHY TX发射机测试示波器带宽及软件推荐

图:MIPI D-PHY TX发射机测试示波器带宽及软件推荐

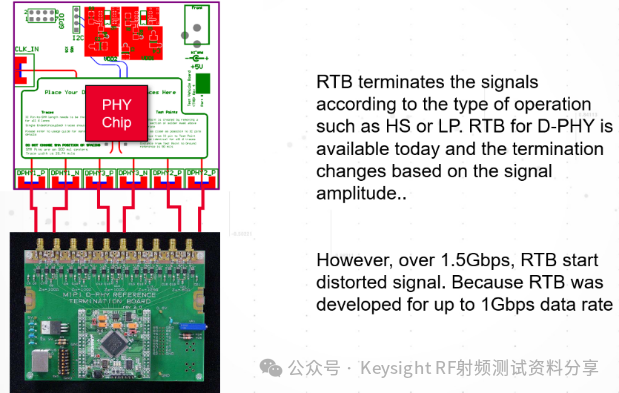

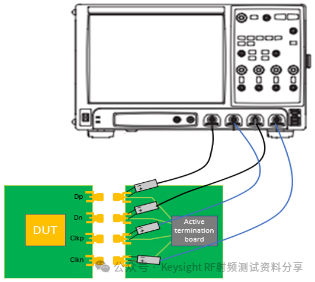

对于 MIPI 芯片或模组的测试可以根据 MIPI 协会推荐的方法设计评估板 TVB (Test Vehicle Board)把信号输出转换成标准的SMA 接口输出,并结合协会提供的 RTB (Reference Termination Board)进行信号测试。RTB 板提供标准的匹配切换以及不同的线路容性的选择,如下图:

图:基于TVB(Test Vehicle Board)的MIPI D-PHY芯片或模组测试

图:基于TVB(Test Vehicle Board)的MIPI D-PHY芯片或模组测试

而对于系统厂商如手机厂商等,由于系统设计已经完成,要进行MIPI信号测试只能使用焊接或点测探头连接PCB上的实际信号进行测试,以下是典型的连接图:

图:MIPI D-PHY板级测试连接

图:MIPI D-PHY板级测试连接

为了提高测试的效率,测试中推荐采用 4 支探头分别连接 clk+/clk- 和 data+/data- 信号进行测试,之所以每个差分对需要两个探头进行测试是因为在 D-PHY 的信号线上HS和LP两种模式并且这两种模式端接方式不同,仅仅使用一个差分探头测试无法满足DUT工作要求。对于有多条数据 Lane 的情况,可以每条 Lane 分别测试。

测试系统的核心是D9020DPHC MIPI 一致性测试软件平台,这个软件采用图形化的界面指导用户完成测试参数的设置和连接,并自动完成信号质量的测试和测试报告的生成,对用户非常的友好,能够极大的提高测试效率。

MIPI D-PHY测试复杂,需要了解它的工作原理,涉及LP模式的测试序列、HS模式的测试序列、HS进入、HS退出、电压参数、时间参数等,如下内容:

Section1 Tx信号包括:

扫描二维码推荐应用指南:如何测试多通道 MIPI M-PHY发射机?

“选择带有 M-PHY多通道协议解码器的示波器可以快速调试协议错误并加快 MIPI MPHY 设计的测试速度。”

下面针对其中测试参数简单举例进行说明:

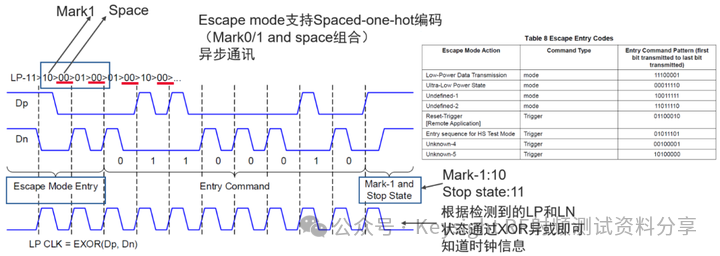

1)数据信号LP-TX的VOH/VOL电平测试需要DUT数据lane0~lane3分别连到50pF电容负载板进行测试,DUT要产生ULPS序列。如何产生该序列,序列有什么特点,参考如下,DUT需要工作在LP-Escape Mode并使能ULPS命令(‘00011110’),该模式是异步模式,采用Space-one-hot编码,对端的时钟信号是通过EXOR(Dp,Dn)获取。

图:Escape mode的LP序列

图:Escape mode的LP序列

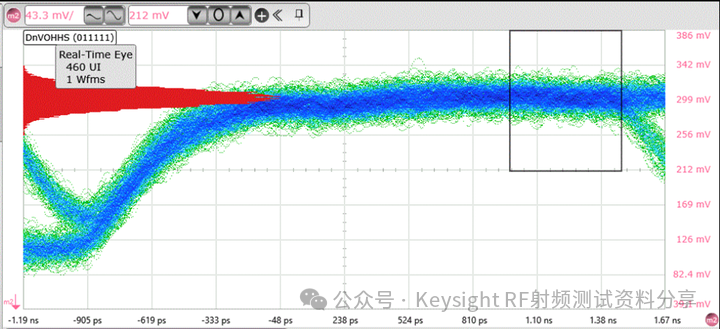

2)高速数据信号HS-TX差分电压VOD(0)、VOD(1)是非常重要的,关系到测量时间参数的电平标准。这里选择基于脉冲的测量方法并使用平均的数据处理算法。HS序列并没有使用常用的编码方式实现直流平衡,为保证测量一致性、重复性和数据内容易获取,这里选择两种参考码型(‘011111’/’100000’)作为数据源先对齐再平均处理,这种连1和连0在内容中相对典型也可以考虑电容效应和阻抗适配效应。测试时考虑时钟和数据同时测量,需要对探头进行deskew,为保证电压测量准确,需要示波器符合仪器校准要求。如果是芯片测试,那么要求lane0~3要遍历RTB的不同负载(80/125/100)。

图:VOD(1)测量波形

图:VOD(1)测量波形

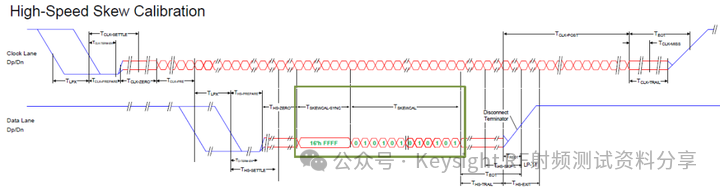

3)高速时钟与数据时序参数Tskewcal-sync/Tskewcal。DUT工作速率超过1.5Gbps,需要支持clock/data的deskew。

这要求DUT要产生HS Burst Sequence,这个序列要包括LP-11/LP-01/LP-00/HS-0/同步码/校准码/HS-TRAIL/HS-EXIT,具体序列波形如下,其中同步码要求是16个连1,校准码要求是4096个UI(0/1交替实现)。

图:HS-TX SkewCal同步和校准序列

图:HS-TX SkewCal同步和校准序列

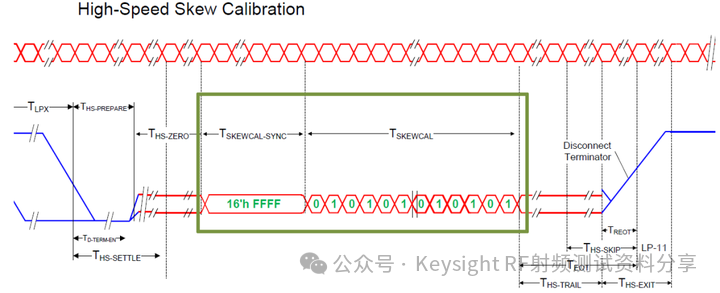

如下展示了利用示波器针对该序列(速率约2Gbps)进行时间参数测量,其中Tskewcal-sync明显没有满足典型16个1的时间要求,Tskewcal明显没有满足典型4096个UI的时间要求。

图:HS-TX Tskewcal测量

图:HS-TX Tskewcal测量

4)芯片测试有专门的测试板TVB和RTB可以辅助用户按照标准进行conformance。如果是移动终端产品,那么测量会相对复杂,会面临空间狭小、电磁环境复杂、负载参数与标准相比有差异等,测量参数和结果可以作为参考,全面测量通过挑战很大。

MIPI D-PHY 接收机测试概览

Rx接收机测试基于高速任意波形发生器配合自动化测试软件完成,用M8190/95A生成特定的波形信号模拟MIPI D-PHY的Tx信号,信号经过示波器校准后,输入DUT的Rx,在DUT内完成测试,测试结果可以通过读取DUT的Error Counter或通过PPI接口读取DUT内部数据或者观察图像信息等,尤其是LP-RX这取决于DUT的能力。系统测试框图如下:

图:MIPI D-PHY 接收机测试框图

图:MIPI D-PHY 接收机测试框图

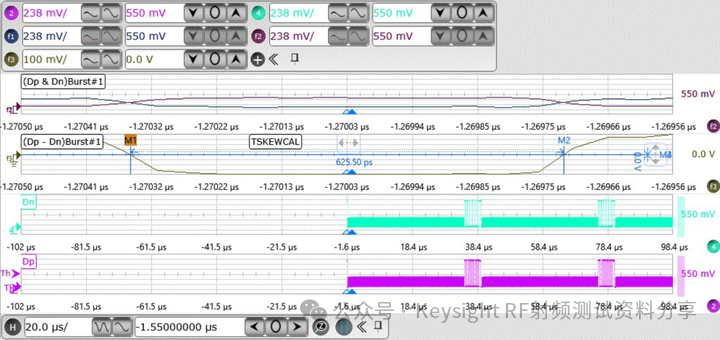

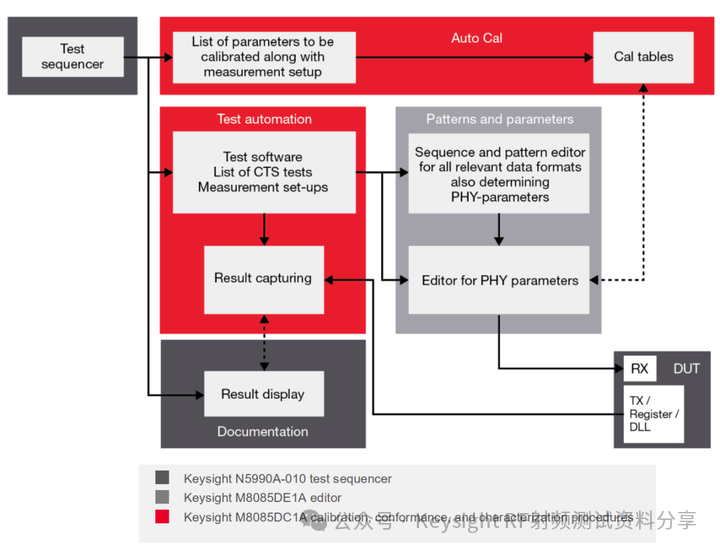

前文中提到,由于MIPI D-PHY信号包括高速HS和低功率LP模式,具有不同的信号振幅、数据率和格式,HS和LP的接收机测试模式需要在不同的信号电平、数据率和格式之间进行无缝切换。而MIPI的D-PHY CTS (Conformance Test Suite)定义了一系列不同的信号设置和校准规范,用M8085DC1A可以完成自助地完成上述的校准,信号生成及测试的过程,可以让用户在不需要深入学习CTS规范的前提下完成快速设置与测试,可极大的节省学习周期及测试时间。

M8085A软件可以支持Debug和Conformance测试。

支持LP-RX电压/时序涉及输入电压高低、迟滞、最小脉宽响应、干扰容限、竞争监控阈值;

LP-Rx行为要求涉及初始化时间、唤醒时间、无效/终止序列、忽略Post-Trigger-Command Extra bits命令的Escape Mode序列、暂未支持命令的Escape Mode序列;

HS-RX电压/建立-保持时间要求涉及共模电压容限、差分输入高电平阈值、单端输入高电平/低电平阈值、正弦共模干扰容忍度、建立-保持时间&抖动容忍度;

HS-RX时间参数要求等,上述这些测试项目通常是使用经过校准的电压、时序等参数实现的测试序列HS或LP给到DUT,通过观察DUT是否有接收错误为判定标准(可以是图像是否正常或者数据是否正确)。

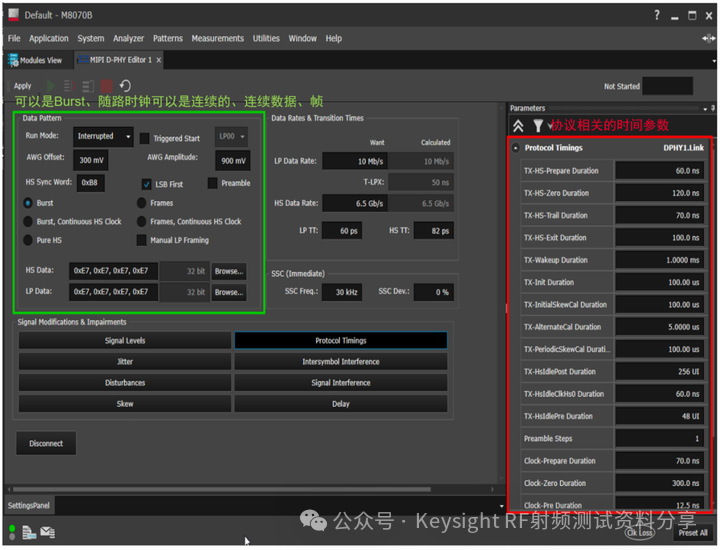

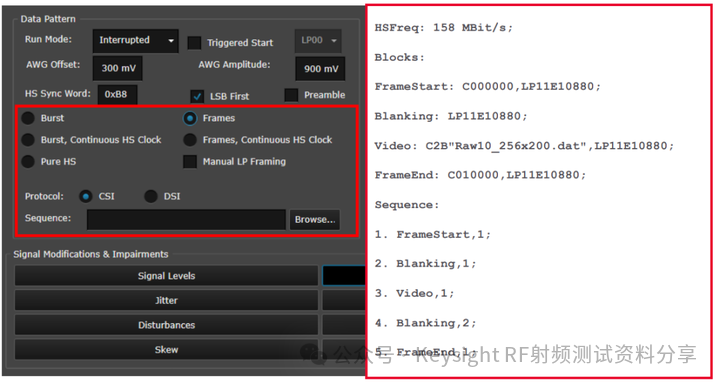

图:M8085A可编辑生成HS Burst等多种格式的数据序列

图:M8085A可编辑生成HS Burst等多种格式的数据序列

图:M8085A可产生CSI/DSI格式的帧

图:M8085A可产生CSI/DSI格式的帧

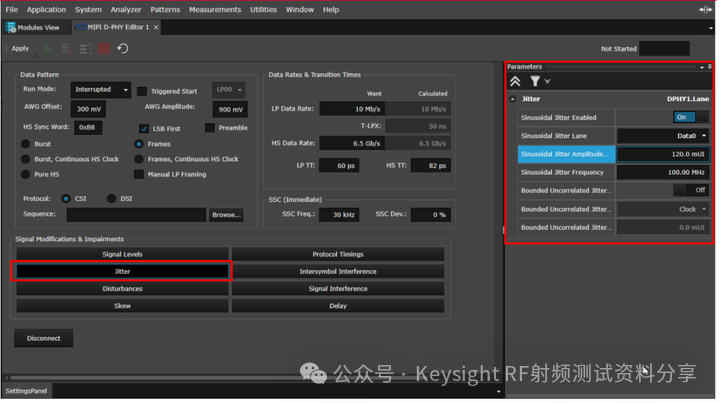

图:M8085A可生成信号电平/抖动/干扰/通道时延/时间参数/ISI/延时等可调序列

图:M8085A可生成信号电平/抖动/干扰/通道时延/时间参数/ISI/延时等可调序列

MIPI A-PHY与车载Serdes芯片技术与测试

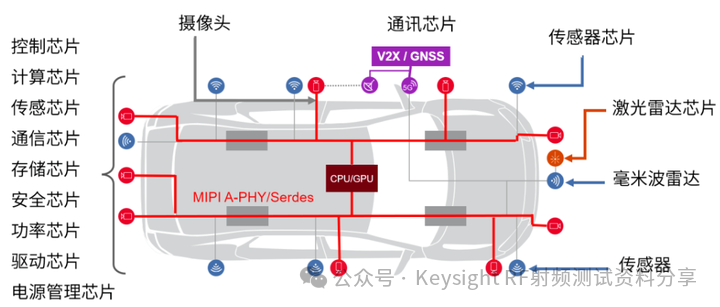

车载Serdes芯片的重要性

汽车智能驾驶时代,特别是辅助驾驶/自动驾驶的普及,环境感知已成为汽车行业中一个新兴的关键技术领域,车载摄像头的数量、分辨率快速增加;大量数据需要高速率、高宽带的传输,使得高性能车载Serdes芯片成为核心零部件之一,如下图是自动驾驶架构框图,Serdes/MIPI A-PHY承担了自动驾驶ADAS芯片与摄像头之间的高速数据互联。

图:ADAS系统与摄像头互联示意图

图:ADAS系统与摄像头互联示意图

目前,从车载摄像头到车载显示器、ADAS域控制器、座舱域控制器等都在使用车载通信Serdes芯片,以实现视频信号和实时数据传输。

车载Serdes主流技术标准概况

目前车载Serdes的标准众多,私有协议包括TI德州仪器的FPD-Link标准,ADI(美信)的GMSL,Inova Semiconductors的APIX,以及罗姆的Clockless Link等。

公开标准目前主要是3个,MIPI A-PHY和ASA,以及中国的HSMT标准。

MIPI A-PHY的阵营的参与者包括宝马、丰田、博世、电装、采埃孚、英特尔、微软、松下、高通等。2018年,MIPI AWG(Automotive Working Group)成立,旨在引入名为MASS(MIPI Automotive SERDES Standard)的通用通信框架铺平道路。2021年,MIPI联盟最近发布了MIPI A-PHY v1.0,这是第一个汽车长距离串行器/解串器(Serdes)物理层接口规范。

目前MIPI A-PHY的最新标准版本是MIPI A-PHY v1.1.1 (2023 5月)。

MIPI A-PHY CTS V1.0标准解读

高级驾驶辅助系统(ADAS)的首要目标,是确保车内驾乘人员和周边行人的安全。只有在接收机以合格的比特误码率运行时,子系统才能正常工作。值得注意的是,接收机测试已经纳入MIPI A-PHY所涉各种相关规范的合规性测试规范(CTS)。在测试Serdes物理层(PHY)信号时,了解它以什么方式发送消息,然后在另一端以什么方式接收消息至关重要。基于最新的CTS v1.0,我们可以涵盖整个物理层测试一致性测试,首先是信号完整性测试,目的是消除来自其他源头的失真、反射、衰减和/或耦合噪声。其次,要在更高层级验证被测器件(DUT)的功能以 及 PHY与 ECU之间的信号传输,了解信号传输是否划分了正确的优先级。最后,您需要将DUT放到一系列压力环境中,并识别它在哪个阶段发生故障,这对整个系统的测试都至关重要。

Serdes/A-PHY测试概览与关键

Serdes芯片的测试,一般可以归纳为:发射机测试,接收机测试与链路测试3类,下面我们分别就几类测试与关键的测试点,做一个详细的介绍。

支持的标准包括:

•MIPI A-PHY 1.0 CTS version 0.9

•ASA 1.1 CTS version 0.2

•GMSL2

Serdes/A-PHY发射机测试

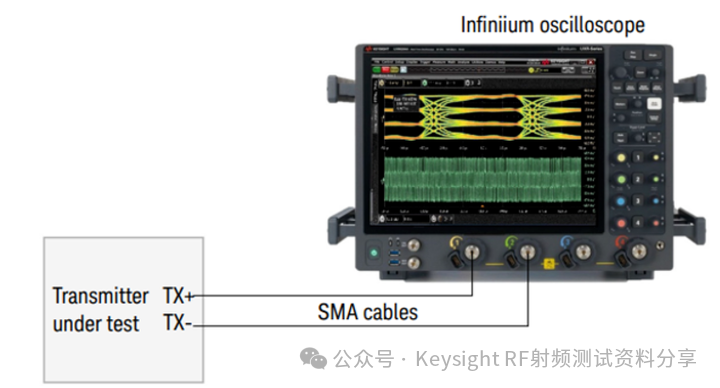

Serdes/A-PHY的发射机Tx测试,主要利用示波器配合是德科技的专有软件完成,如下图是一个典型的差分SMA连接的发射机测试框图。

图:差分连接的TX发射机测试框图

图:差分连接的TX发射机测试框图

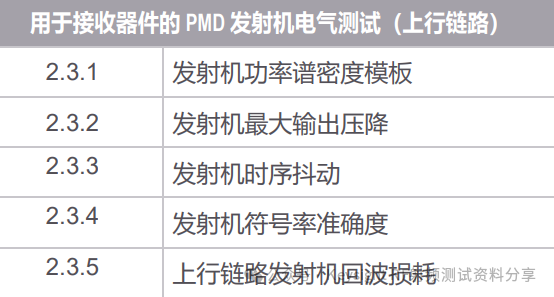

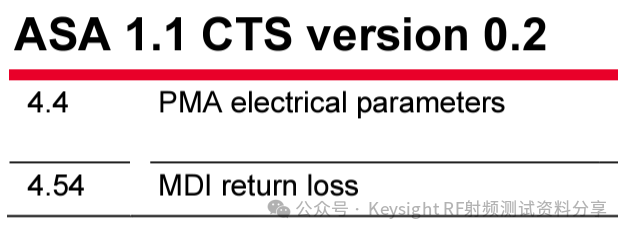

采用是德科技UXR系列示波器作为信号接收,以得到优异的底噪和抖动性能,配合Keysight AE2010T 汽车 Serdes 发射机测试应用软件,测试时能够自动配置示波器,并提供详尽的测试结果,其中包含裕量和统计分析结果,一般的测试项如下:

图:ASA 1.1 CTS 第0.2版测试项

图:ASA 1.1 CTS 第0.2版测试项

图:GMSL2测试项

发射机测试关键测试点包括:

可以执行基于Serdes协议(含 MIPI A-PHY和 ASA)的验证测试,以及如下的测试项

• 频率

• 失真

• 抖动

• 压降

• MDI回波损耗

Serdes/A-PHY接收机测试

Serdes/A-PHY的接收机Rx测试,相对比较复杂,需要借助高速任意波形发生器来完成,测试项也相对较多,如下是一个典型的Rx测试框图,借助M8195A任意波形发生器,产生带压力的信号,通过AE2090B夹具加噪声,控制软件AE2010R单独在PC上运行。

图:RX接收机测试框图

图:RX接收机测试框图

接收机关键测试点包括:

接收机负责解码通过链路发送的数据,然后将其传送给 ECU 或显示设备做进一步处理。接收机一旦出现误码,会导致来自安全关键型传感器(如摄像头、雷达和激光雷达)的数据丢失或损坏。

传统的接收机功能越来越不适应 PAM-4 等复杂的调制方案,特别是通过长信道传输信号、受到多种噪声源同时干扰的情况。为了表征接收机的性能,工程师必须测量其在受到多个噪声源干扰时的误码水平,包括:

• 窄带干扰

• 大电流注入

• 在线瞬变

• 线外串扰

测量系统可以包括噪声源、放大器和耦合电路,以便向有源 Serdes 链路注入精确的噪声电平。接收机必须在受到噪声干扰的情况下也能正确解释符号。接收机测试的重点在于,确保接收机在受到干扰时仍能保持较低的比特误码率(BER)。

Serdes/A-PHY链路测试

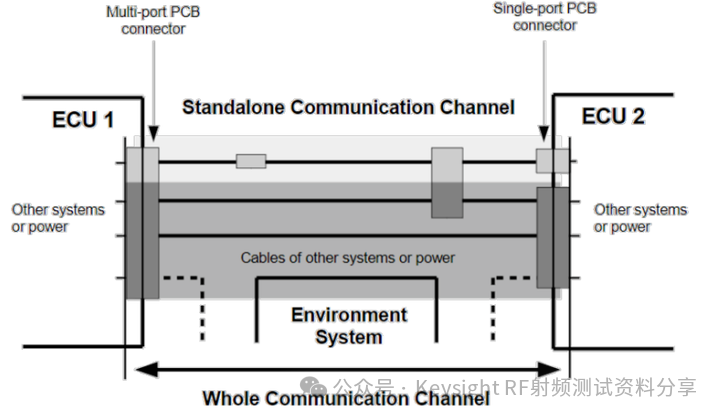

Serdes的链路测试包括了连接器,电缆,转接头等的测试,通常是用网络分析仪配合一系列的转接头等来完成,下图是典型的Serdes传输通道示意图:

图:Serdes/MIPI A-PHY传输通道示意图

图:Serdes/MIPI A-PHY传输通道示意图

可以看到,不同的ECU之间,通过高速的电缆连接,而不同厂家可以采用不同的转接和电缆的标准,链路测试需要全面的评测端到端的链路性能,符合Serdes/MIPI A-PHY的标准要求。

链路测试,可以采用AE2000L链路一致性测试系统来完成,可以根据需求来需求来选择不同类型的网络仪,包括高性能的ENA系列,多端口的PXI模块以及高性价比的USB网络分析仪组建测试系统,配合AE2010L自动化测试软件,能够很容易的完成链路测试从校准到报告输出的过程。

Serdes链路关键测试点包括:

Serdes链路的通道表征包括时域和频域分析。工程师需要查看线缆连接系统、MDI、夹具和测试系统要求。目前还没有针对 MDI 连接器的统一标准,但已经出台了一些严格的规范,这有助于减少 MDI 和电缆之间的相互作用。

• 阻抗失配

• 信号失真或缺陷

• 电缆之间的串扰

需要MIPI接口更多信息,您可联系是德科技:www.keysight.com.cn