近日,国内连城数控、天域半导体、中电科46所三家企业公布了其在8英寸碳化硅晶锭生长、衬底制备及外延生长的最新突破,有望在量产应用中进一步降低缺陷密度、提高晶体质量:

连城数控:

8吋晶锭厚度超30mm

11月28日,连科数控宣布旗下子公司连科半导体的8英寸碳化硅电阻式长晶炉在客户现场完成批量验收,标志着其八吋电阻炉量产进入国内第一梯队。

据悉,连科半导体的电阻炉通过石墨电阻发热,由热辐射传导石墨坩埚进行加热,可调整石墨加热器的结构,有效的进行分区功率控制和温场的控制,更适合生长大尺寸的碳化硅晶体。

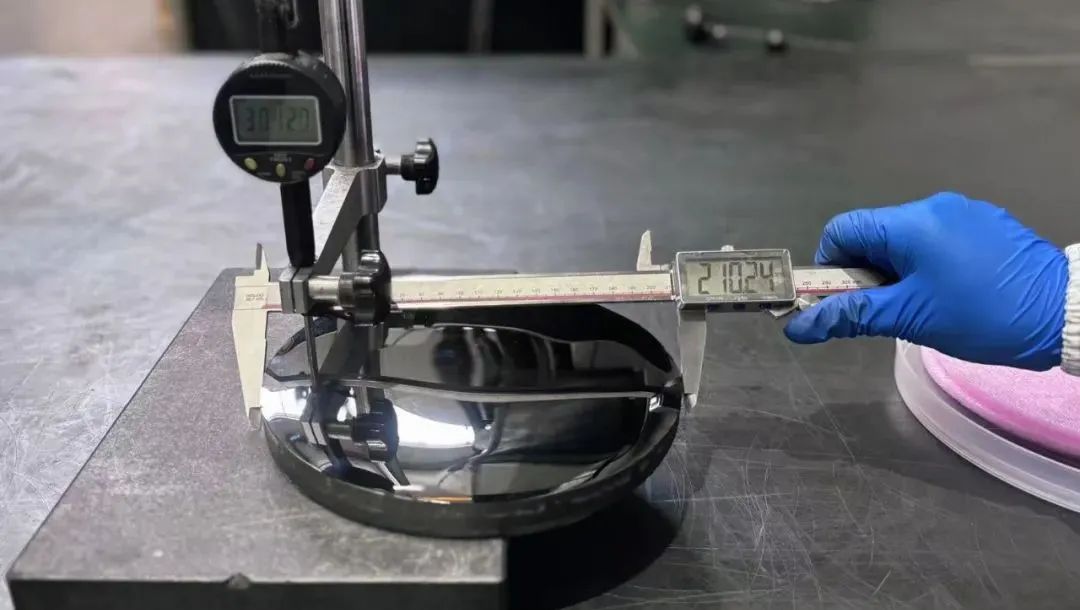

此外,其具有成熟的热场设计,有利于缺陷控制,并可配备多个加热器并独立控制,便于调整温度梯度,目前已成功制备直径超210毫米,厚度30毫米的8吋导电型SiC晶体,晶体表面光滑无缺陷。

天域半导体:

8吋外延质量优于国外数据

近日,《人工晶体学报》刊登了题为《8英寸SiC晶圆制备与外延应用》的研究论文,由天域半导体丁雄杰博士团队联合南砂晶圆、清纯半导体、芯三代共同发表。

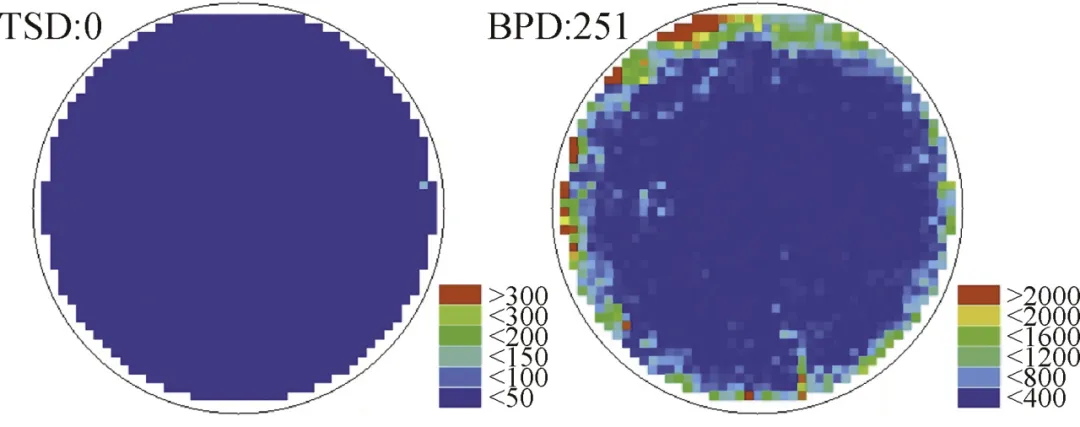

据了解,该研究团队由南砂晶圆采用PVT法制备了厚度为500 μm的8英寸导电型4H-SiC衬底晶圆,其平均基平面位错(BPD)密度低至251cm-2,平均螺位错(TSD)密度小于1 cm-2,实现了近“零TSD”和低BPD密度的8英寸导电型4H-SiC衬底晶圆的制备,可以满足生产需要。

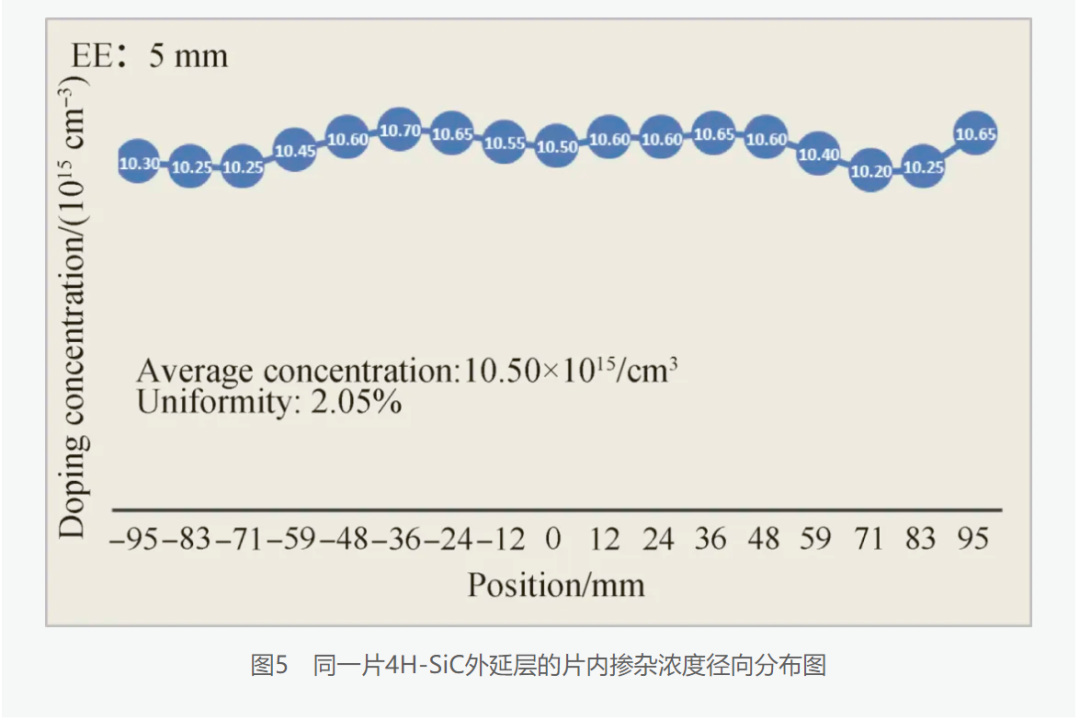

在此基础上,研究团队采用国产8英寸外延设备和开发工艺包,在8英寸晶圆上实现了速率为68.66 μm/h的快速外延生长,获得的外延层厚度的平均值为11.44 μm,标准偏差为0.10 μm,不均匀性为0.89%,掺杂不均匀性为2.05%,该指标已经达到了优良6英寸外延膜的水平,完全可以满足生产需要。与国外已发布的8英寸外延结果对比,厚度和掺杂均匀性均优于国外数据,而缺陷密度只有国外数据的1/4。

为了进一步考察8英寸晶圆上外延生长的重复性和稳定性,研究团队采用同一个工艺菜单,进行了另外2次外延生长,完成了重复性实验,结果表明,此次研发的8英寸外延片重复性良好,具有良好的稳定性,可以进行大批量试生产和进一步量产研究优化。

加入碳化硅大佬群,请加微信:hangjiashuo999

中电科46所:

8吋BPD密度降至704 cm-2

近期,由中电科46所、哈尔滨工业大学联合发表了一篇题为《降低8 英寸碳化硅单晶 BPD 密度的数值模拟和实验研究》的论文,其中透露,他们通过各种创新工艺,可以将BPD 密度降低到 704 cm-2。

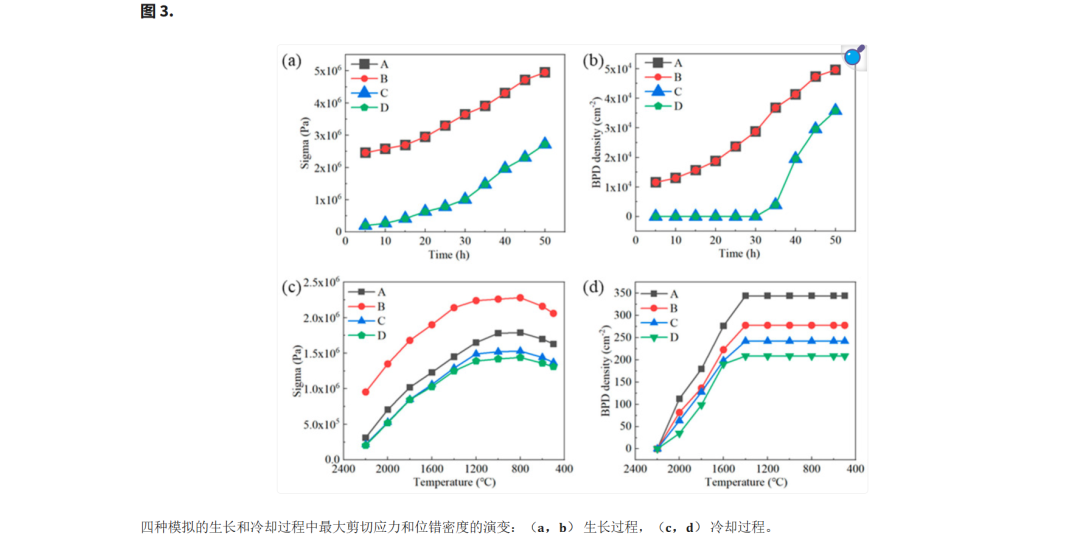

据悉,该研究团队首先采用 STR-VR 软件 模拟了 8 英寸 SiC 单晶的生长和冷却过程,并分析了不同因素对 SiC 晶体应力和 BPD 密度的影响,他们发现:

在生长过程中,随着 SiC 晶体厚度增加,剪切应力和位错密度也随之增加,在冷却过程中,剪切应力会相应增加,然而,位错密度在初始冷却阶段也会增加,但在后期冷却阶段却保持相对稳定。

细分来看,在冷却过程中,较高的冷却速率导致更大的剪切应力和更小的位错密度。这是因为,在快速冷却情况下温度迅速降低,位错迁移速率急剧下降,位错传播减少。此外,通过优化籽晶黏接方法、石墨坩埚材料也可以帮助减少BPD 密度。

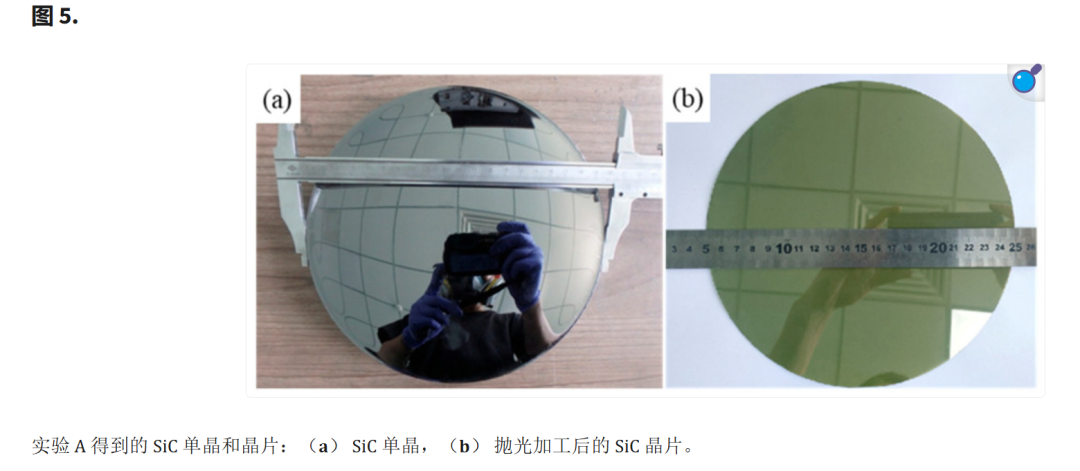

据此,研究团队通过提高冷却速率、优化籽晶黏接方法以及采用与 SiC 单晶热膨胀系数相似的石墨坩埚来进行实验,结果表明:高冷却速率将BPD密度从4689cm-2降低到 2925 cm-2 ;优化籽晶黏接方法的将 BPD 密度降低到 1560 cm-2;通过采用热膨胀系数较小的石墨坩埚,BPD 密度进一步降低到 704 cm-2。

值得关注的是,截至目前,全球8英寸碳化硅衬底玩家已超30家,其中不少企业已实现量产应用。但是,与6吋工艺相比,8吋在成本、效率上还有极大的优化空间,下游器件厂商及终端应用也希望8吋能进一步降本增效,开拓更加广阔应用市场。

那么,8英寸碳化硅技术有哪些最新进展?头部厂商对其有哪些判断?针对业界聚焦的核心问题,在12月11日-12日举办的“2024行家说三代半年会”中,将设置8英寸SiC单晶生长&衬底加工技术、8英寸SiC外延与芯片制造关键技术两大专场报告,由烁科晶体 、合盛新材料、同光股份、中电化合物 、三安半导体、中车半导体、恒普技术、致领半导体、创锐光谱、思锐智能等8英寸玩家带来重磅演讲。

此外,本届大会得到了碳化硅产业链上下游企业的高度关注,除了以上企业,还有安世半导体、士兰微、意法半导体、平湖实验室、罗姆、悉智科技、英飞凌、纳微半导体、晶能微电子、快克芯装备以及芯联集成等企业将出席【行家说三代半年会】,共带来近30场主题演讲,报名请扫描海报尾部二维码!

转发,点赞,在看,安排一下