人工智能(AI)近年来已广泛应用,并迅速成为一项具有变革性的技术。AI依托于机器学习(ML)算法,而这些算法需要强大的计算能力。传统上,开发者们依赖图形处理器(GPU)来运行这些ML算法。GPU最初为图形渲染而设计,但已证明在执行人工智能所需的矩阵和向量运算方面非常有效。然而,AI硬件领域的格局正在经历巨大变革。计算需求的日益复杂和对能效提升的需求促使一些专注于特定领域AI处理器的初创公司涌现。这些公司开发的AI处理器针对ML算法进行了架构优化,与通用GPU相比,它们的性能功耗比显著提高。

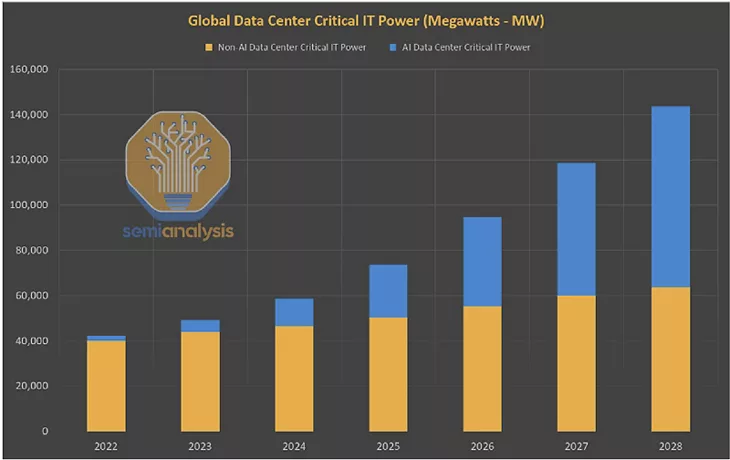

随着AI技术的不断发展,对更强计算能力和更高能效的需求将持续上升。根据Semianalysis的分析,预计到2028年,AI数据中心的电力需求将超过非AI数据中心,占全球数据中心总电力消耗的一半以上,而目前这一比例还不到20%。

▲图1AI数据中心和非AI数据中心的电力需求

数据中心行业正在努力减轻电力负荷,逐步摒弃传统的空气冷却方式,转而采用成本较高但效果显著的液冷技术。然而,单靠外部冷却技术的进步远远不够。为了应对不断攀升的电力需求,人工智能硬件开发商还需在系统设计层面进行创新,深入挖掘全面的电力优化策略。

新思科技Foundation IP如何推动低功耗开发

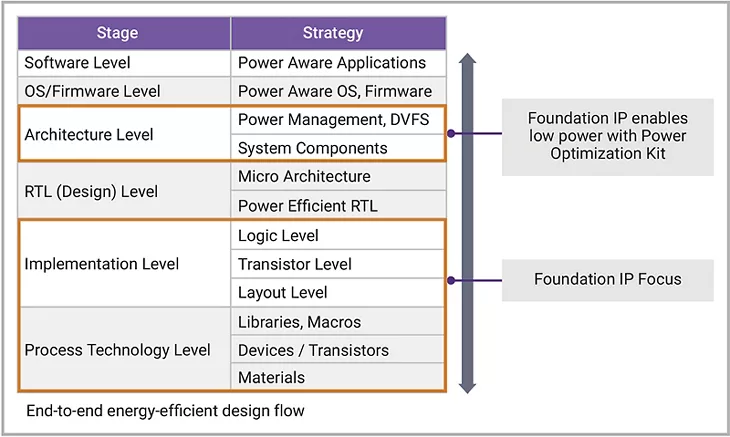

在设计系统级芯片(SoC)时,开发者可以在设计的不同阶段,包括架构层次、实现层次以及底层技术层次,进行功耗优化。新思科技Foundation IP能够助力开发者针对这些关键领域进行优化。SoC的功耗主要源于电路切换引起的动态功耗以及漏电(或称静态)功耗。动态功耗在处理器执行指令任务时产生,与CV²f成正比,这里的C代表开关电容,V为工作电压,f是电路时钟频率。无论处理器处于空闲还是活跃状态,漏电功耗都会发生,并且随阈值电压、晶体管尺寸和温度而变化。在架构层面,通过采用电源门控、动态电压频率调整(DVFS)等电源管理技术来降低整体功耗。在实现和工艺技术层面,通过设计优化以及对逻辑单元和嵌入式存储器操作条件的精细管理,直接影响功耗。让逻辑单元和存储器在维持所需性能的前提下尽可能在更低电压下工作,同时通过专门设计的单元减少活跃节点上的电容,这些都能显著促进功耗的降低。

新思科技凭借多代Foundation IP优化积累的深厚经验和强大能力,在AI SoC的功耗优化中扮演着关键角色。新思科技Foundation IP提供的先进解决方案包括经过硅验证的高度优化的逻辑库、通用输入输出(GPIO)及嵌入式存储器。新思科技的逻辑库和IO与新思科技的电子设计自动化(EDA)工具协同优化,充分利用工艺技术的优势,以实现功耗、性能和面积(PPA)的最佳平衡。新思科技的存储器集成了针对机器学习算法的关键特性,为AI芯片带来了显著的面积及功耗节省。

▲ 图2端到端的能效设计流程

让我们深入探讨新思科技Foundation IP如何帮助降低功耗,特别是针对AI处理器。

针对AI处理器的专用逻辑单元与新思科技存储器的间距匹配

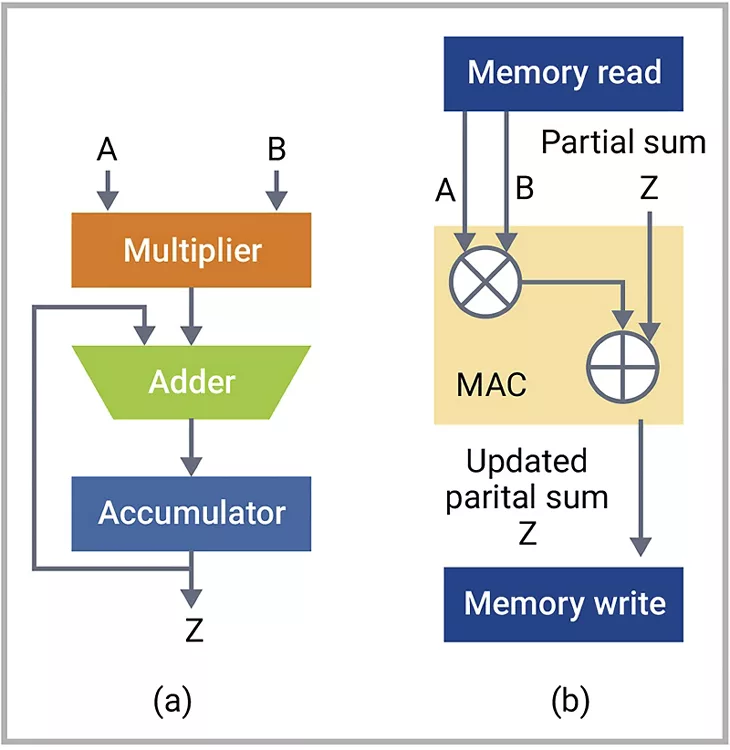

在AI处理器中,无论是训练还是推理任务,大量的计算活动(70-90%或更多)都致力于乘累加(MAC)操作,这是矩阵乘法和卷积的基础。新思科技提供的逻辑库包含了专为AI处理器设计的复杂逻辑,支持MAC功能。这些单元具备如融合乘加能力等特性,有助于减少设计的净长度和整体电容,从而显著降低动态功耗。对于AI芯片而言,集成高效能存储器同样重要。在机器学习模型中,特别是在推理任务中,参数权重存储在存储器中,并频繁被MAC单元访问以进行计算(见图3)。新思科技提供了与MAC单元间距匹配的嵌入式存储器。这意味着存储器和逻辑单元的物理布局在尺寸和间距上进行了协同优化。这种集成设计策略带来了更短的互连,某些应用中已证明能减少33%的功耗。

▲ 图3(a)MAC单元框图(b)MAC单元的存储器读写

可定制的超低电压库

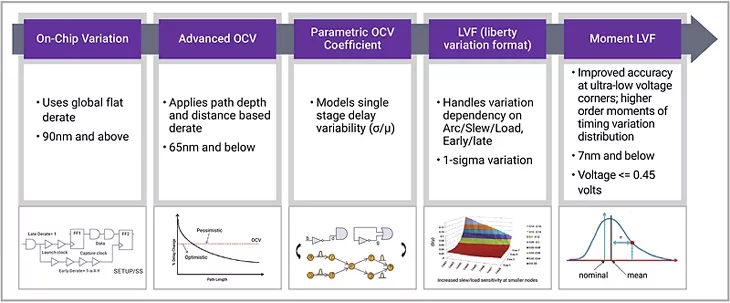

在先进技术中,设计在超低供电电压下运行的芯片,特别是在0.5V以下,极具挑战性,需要非常细致的设计和验证。然而,使用低供电电压的功耗效益可能是巨大的,因为降低电压会对动态功耗产生二次方减少效应。AI处理器通常依赖于巨大的并行性来提高性能,不需要在高频下运行。它们特别可以从使用超低电压库中受益。新思科技通过其可定制的超低电压逻辑库支持低功耗芯片设计。这些库基于高质量和详尽的验证,采用先进的表征技术,在广泛的工艺、电压和温度(PVT)条件下进行测试。低电压带来的挑战包括降低的噪声裕度和对制造变异的敏感性增加。随着供电电压的降低,信号改变电路下一阶段状态的能力减弱。这可能导致信号更像脉冲,通过电路传播的时间更长。这种延迟可能会影响电路的关键时序方面,包括建立时间和保持时间。为了解决这个问题,开发者应考虑额外的因素,如轨到轨脉冲检查、针对芯片内变异(OCV)的额外时序裕度、保持时序的高西格玛要求以及时钟偏斜建议。新思科技Foundation IP的开发者在开发单元时会考虑到这些变异,单元会经过高西格玛蒙特卡罗模拟以进行稳健性验证,而谨慎使用基于矩的库变异格式(LVF)允许对制造变异的概率特性进行精确和详细的建模

▲ 图4低供电电压导致的片上变异复杂性提升

具有分数驱动强度的逻辑单元

具有更高驱动强度的逻辑单元消耗更多功耗,并且由于其更大的晶体管而倾向于有更高的漏电。对于非关键路径,已经通过使用高阈值电压(VT)单元进行了功耗优化,可以通过使用具有分数驱动强度的单元来进一步降低功耗。新思科技逻辑库组合包括一系列这样的分数驱动强度单元,包括驱动强度小于一的单元。

功耗优化套件

为了增强功耗节省,新思科技在其标准单元平台中提供了功率优化套件(POK)。该套件包括各种专用逻辑单元,旨在实现先进的电源管理技术。这包括帮助减少静态功耗的电源开关和隔离单元,通过在不需要时启用块关闭。该套件还包括电平转换器,通过允许不同块根据其性能要求在不同的电压下运行,协助动态功耗降低。此外,POK还具有多比特版本的隔离单元、保持触发器和电平转换器,有助于减少净长度和整体单元面积。

超低漏电IO

在具有AI芯片的SoC中,虽然片上组件在低电压下运行,但这些需要连接到在更高电压下运行的片外组件。设计支持如此电压范围的GPIO极具挑战性,大多数公司转而使用电平转换器,给设计增加了不必要的面积和功耗。新思科技提供了一套全面的超低漏电IO,支持低至0.5V的电压。这些相同的IO还支持1.8V IO供电,提高整体系统可靠性。具有AI芯片的SoC也更大,需要严格的静电放电(ESD)保护标准。新思科技提供的IO解决方案包括强大的ESD保护,能够处理高达CDM 7A的电流。这转化为更高效、可靠和具有成本效益的AI SoC设计。

非易失性存储器和基于锁存的存储器

新思科技提供了一系列先进的内存解决方案,包括嵌入式磁阻随机存取存储器(MRAM)和电阻随机存取存储器(RRAM),它们提供的密度显著高于传统的SRAM。对于以读取为主的应用,例如存储训练数据,用MRAM或RRAM替换SRAM或片外DRAM可以显著提高系统级PPA。这些非易失性存储器(NVM)减少了硅面积和所需组件的数量。此外,由于它们不需要恒定功率来维持其数据状态──与DRAM不同──它们消除了频繁刷新周期的需要,从而降低了静态功耗并减少了漏电流。新思科技还提供基于锁存的存储器,为较小的内存实例节省了大量面积。这些对于特定的AI功能特别有用,如激活和池化,这些功能需要许多小的内存实例。此外,新思科技提供了专门的多端口存储器,能够同时处理多个内存访问请求,有助于缓解内存瓶颈并提高整体性能。

存储器中的稀疏性和转置支持

在许多机器学习模型中,要计算的数据中有相当一部分是零值字,可以在读/写操作期间跳过以节省功率。为了利用这种数据稀疏性,新思科技在其存储器中引入了一项名为WAZ(Word All Zero)的创新功能。该功能通过检测并跳过零值,可以将功耗降低高达60%。此外,新思科技开发了一种在存储器中以转置格式存储数据的方法。这意味着矩阵元素在存储器中对齐,以匹配其在计算期间的访问模式。结果,矩阵操作执行更快,节省了能源,提高了整体效率。

总结

随着应用需求与AI技术的持续演进,开发具备强大计算能力且高效节能的AI处理器已成为普遍需求。传统的基于GPU架构以及新兴的优化AI架构正将能效推向极致。传统上为CPU及早期GPU优化的库和存储器方案,已难以满足当下AI SoC设计严苛且特定的需求。作为基础IP领域的佼佼者,新思科技凭借二十余年的创新历程,始终致力于最优PPA的研发,持续推出专业解决方案,以满足半导体行业不断变化且极具挑战的设计需求。在强大的研发团队与技艺精湛的应用工程师共同支持下,新思科技发挥其在逻辑库、IO及嵌入式存储器领域的深厚专长,提供独具特色的可调解决方案,全面提升AI芯片的性能范畴。