20世纪最伟大的发明是什么,你可能会得到一个答案——晶体管。

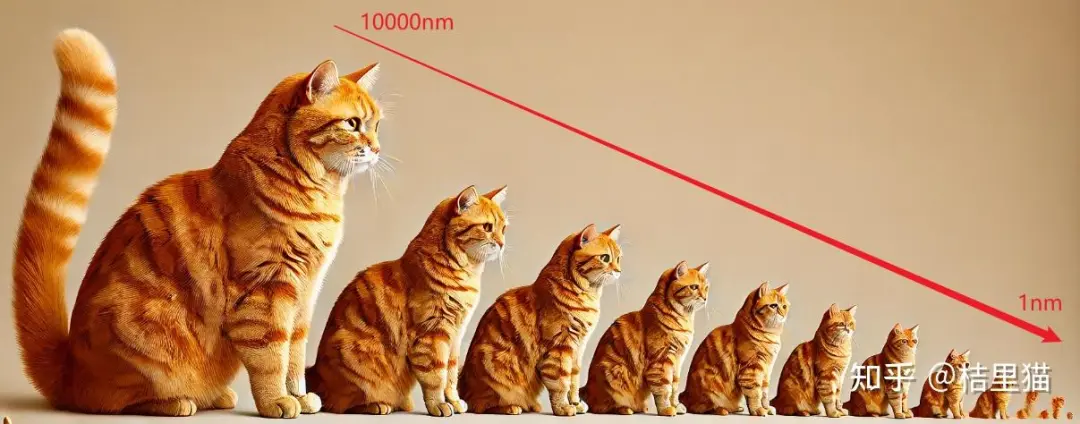

这篇文章带大家重走晶体管从发明、从20000nm制程到1nm制程、点燃科技革命的长征路。

此处需要注意的是,广义上的晶体管种类挺多,此处我们着重讲讲,用于大规模集成电路中的晶体管。同时,这篇文章既讲故事,也讲原理,如果原理看不懂可以跳过当故事看。

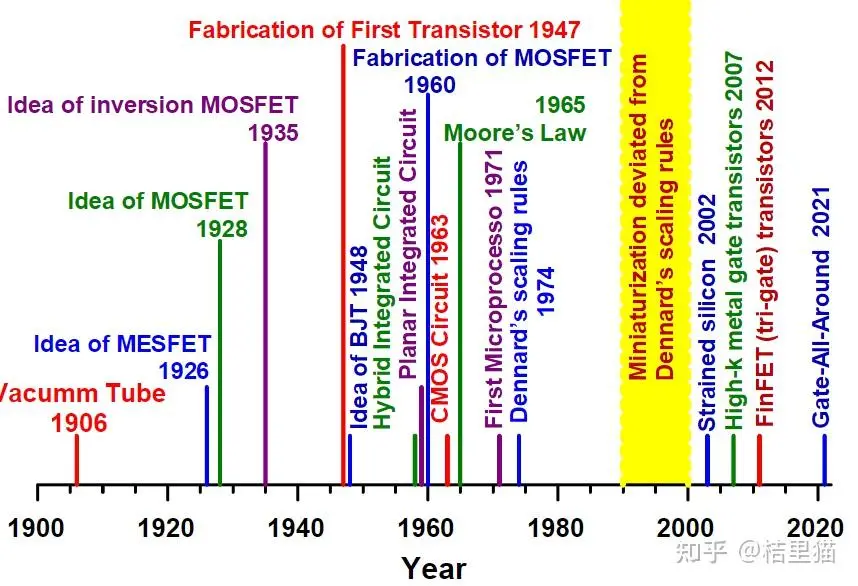

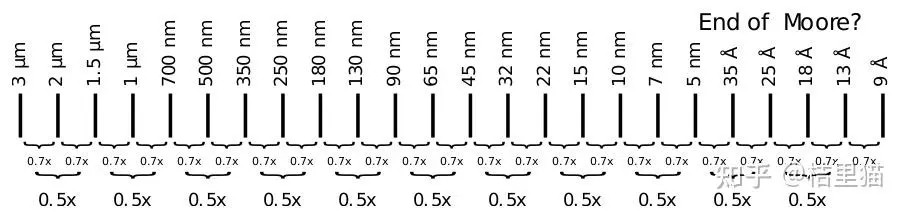

上面这张图标出来了晶体管发展的历史。如果你不是专业选手,现在看不懂没关系,等你读完这篇文章,再回过来看。

一定看的懂这每一步的意义。当然,如果你对晶体管比较熟悉,通过这张图你应该就比较明白我打算在这篇文章里讲点什么。

我们的故事,还是要从Wiliam Shockley讲起,看过我芯片简史的小伙伴应该记得,这哥们,靠着徒子徒孙(仙童,intel, etc)曾经占据半导体行业半壁江山。

1936年,年轻的肖克利拿到了博士学位,找了个贝尔实验室的工作养家糊口。其实晶体管的想法他早就有,提出了场效应理论。然后他并没有深入下去,我们按下不表。

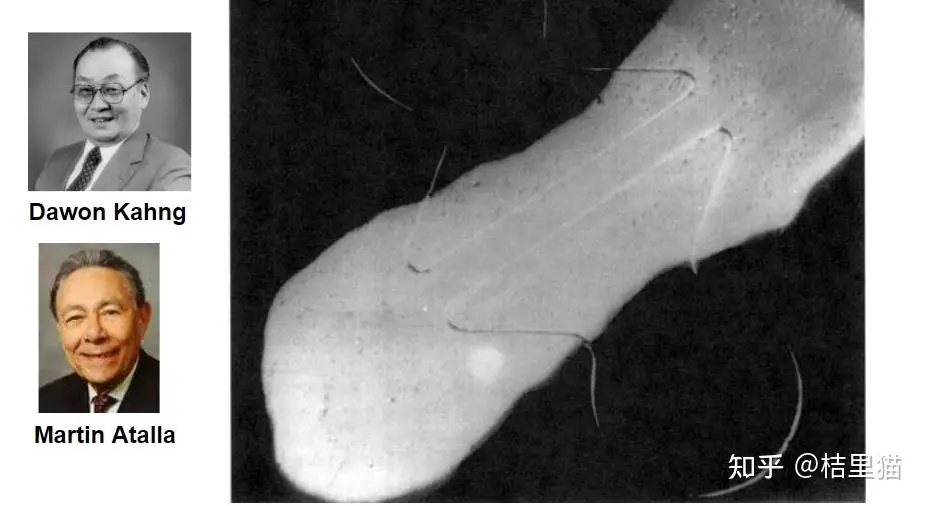

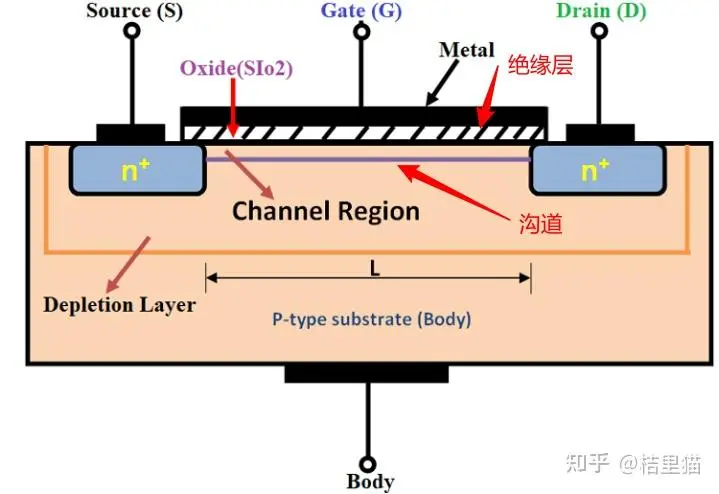

二十多年后的60年,科恩(Dawon.Kahng)和马丁.阿塔拉(M.M.Atalla)根据shockley的理论搞出来了东西叫做绝缘栅场效应晶体管(Field Effect Transistor,FET)。

他两发现,在由金属(Metal栅)、氧化物(Oxide绝缘)和硅(Silicon半导体)组成的三明治中,在硅和其氧化物之间的界面处,电特性可以改变,因此将其命名为MOSFET,也就是今天我们常说的MOS,记住它的大名:金属氧化物硅基场效应晶体管。。

可惜的是,这个时候的MOS速度贼慢,通道长20微米(20000nm),比当时较火的双极型晶体管慢100倍。。。所以并没有很受重视。贝尔实验室申请了个专利(US 3102230)后就搁哪儿。。

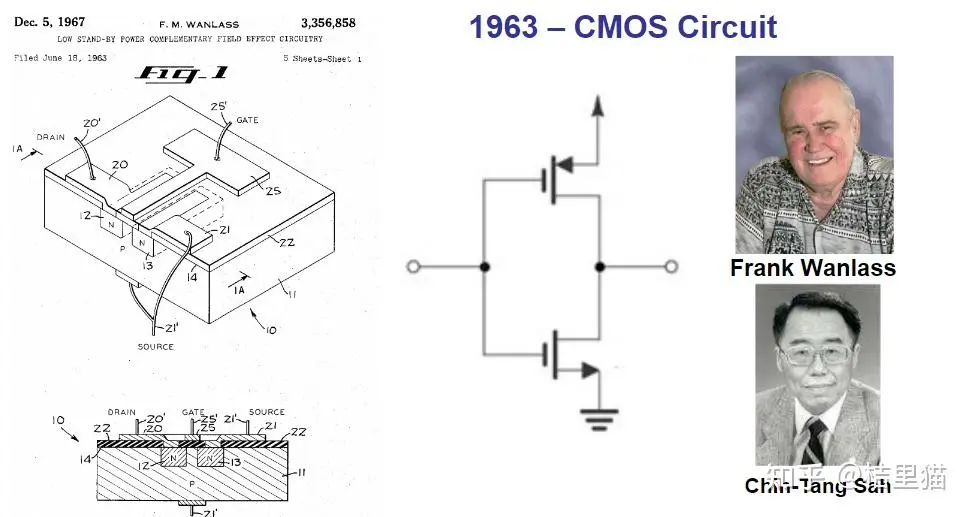

时间来到了1962年,仙童半导体来了一个叫Frank Wanlass的哥们,对MOS晶体管非常痴迷。63年后他在ISSSCC上发文章,在同一集成电路上放上PMOS和NMOS, 这就是我们说的CMOS。。。

由于自己感觉在仙童不太受重视,他跳槽到了GME(通用微电子公司), 并在64年造出了第一个CMOS IC的demo, 一个20位的移位寄存器。然后这哥们拿着这个demo 芯片到处炫,最后被NASA看上了。NASA看上它的原因主要是:CMOS表现出的的功耗。在CMOS之前大家普遍使用NMOS器件,NMOS工艺简单,但有个问题,电路不动的时候也有静态功耗。

后来的后来,GME因为没钱倒闭了。Frank是个狂热的MOS爱好者以及传道者,intel创立以后moore试图挖来frank, 由于frank有其他公司的合同在身,人没挖成功,但是frank详细的介绍了MOS的工作,玩了一把生在曹营,心在汉。

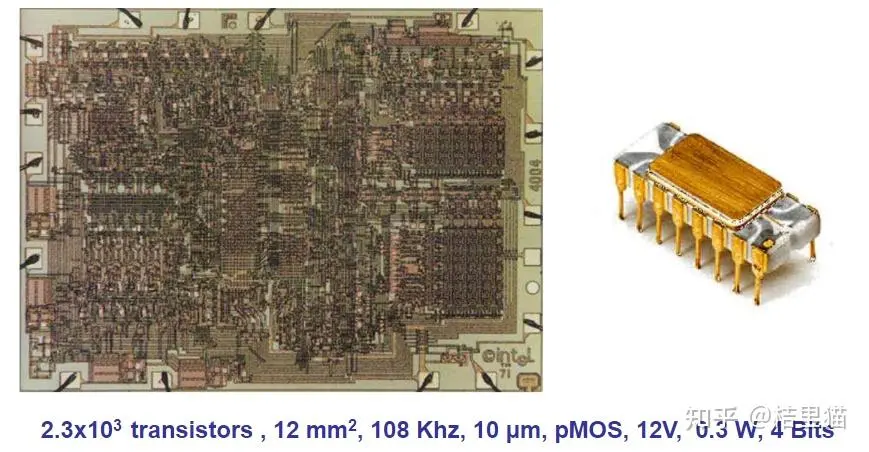

1971年,intel第一个用晶体管造的处理器发表在了当年的ISSCC上。10000nm工艺(滑稽表情)。

后面的故事我们也知道,摩尔提出一个著名的定律:摩尔定律。在1980年左右,随着晶体管数目不断上升, NMOS导致的静态功耗再也没把发接受。intel用CMOS开创了一个半导体的新时代!

讲完了故事,我们来讲讲,上面提到的MOSFET到底是一个什么样的工作原理。

MOSFET实际上是个三极管,要讲清楚原理,我们先从半导体PN结原理讲起。首先我们来看如何通过掺杂造出半导体。

我们先从硅的电子结构讲起,硅实际上有14个电子。其中内层电子它比较稳定,最外层4个电子,容易丢失或者获得其他电子,形成共价键,8个电子才是稳定态。一般来讲,我们画的时候只画最外层4个。

本来硅原子堆在一起,会形成如下中间硅原子一样的结果,和周边的硅原子形成共价键,周边恰好8个电子,这个时候Si是不导电的。没有掺杂的Si, 我们叫本征半导体。

那假如,我们在Si里掺杂一点五个电子的Sb, 由于周边都是Si,只需要4个电子,此时Sb还是倾向于形成8电子的稳定结构,此时多出来的一个电子就成了自由电子。同理,掺入3价的B,此时少一个电子,就形成了一个电子空穴。

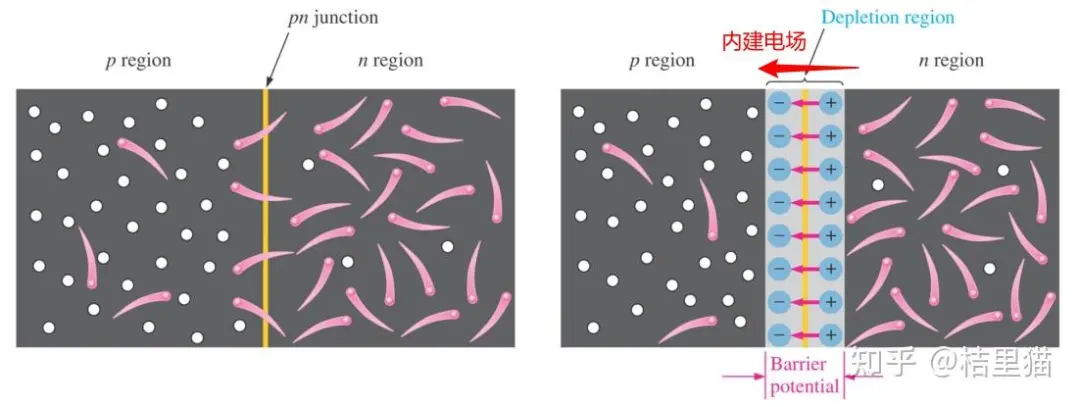

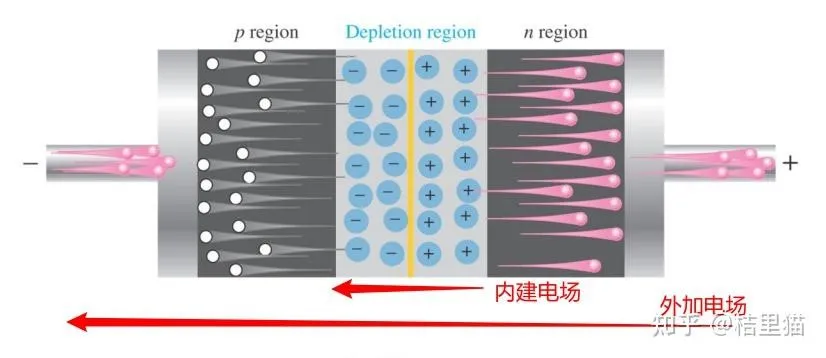

有了自由电子和空穴,此时的材料就能。。导电了。我们把有空穴的叫positive region, 有电子的叫negative region, 把两种材料怼在一起。如下图所示的一样,电子和空穴会相互扩散然后中和。

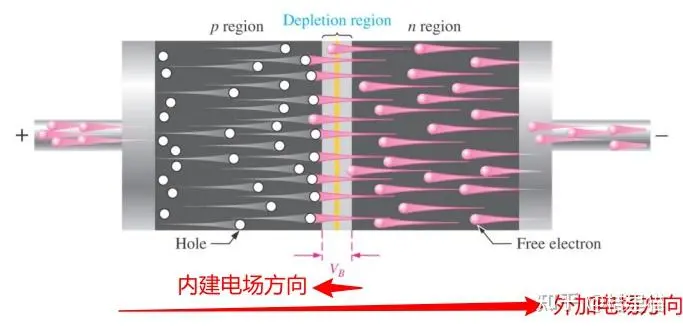

相互中和了会发生什么?原来电子和原子核数是相等的。n区电子被空穴中和后,电子少了,形成一个正电区域。同理,p区形成一个负电区域,此时PN节处就有了一个内建电场。这个内建电场阻止了电子继续往p区移动。

此时我们要是在P区和N区加一个大于内建电场Vth的电压,此时外面加的电场足够大,可以克服内建电场的影响,那么自由电子成功被吸引到正极,PN节就导通了。

由此,我们得到了一个可以单向导通的PN结,这个是所有晶体管的基础。

有了PN节以后,我们继续往下看。此时我们就要介绍我们的晶体管原理了。

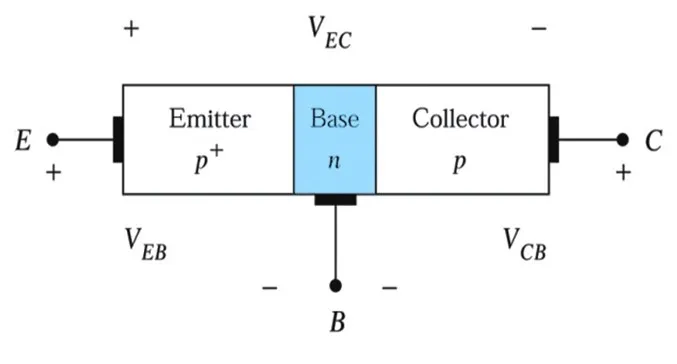

下图为p‒n‒p双极型晶体管,具有三段不同掺杂浓度的区域,形成两个p‒n结。浓度最高的p+区称为发射区(emitter,以E表示);中间较窄的n型区域,其杂质浓度中等,称为基区(base,用B表示),基区的宽度需远小于少数载流子的扩散长度;浓度最小的p型区域称为集电区(collector,用C表示)。各区域内的浓度假设均匀分布,p‒n结的概念可直接应用在晶体管内的结上。

下图为p‒n‒p双极型晶体管的透视图,其制造过程是以p型半导体为衬底,利用热扩散的原理在p型衬底上形成一n型区,再在此n型区上以热扩散形成一高浓度的p+型区,接着以金属覆盖p+、n以及下方的p型区形成欧姆接触。

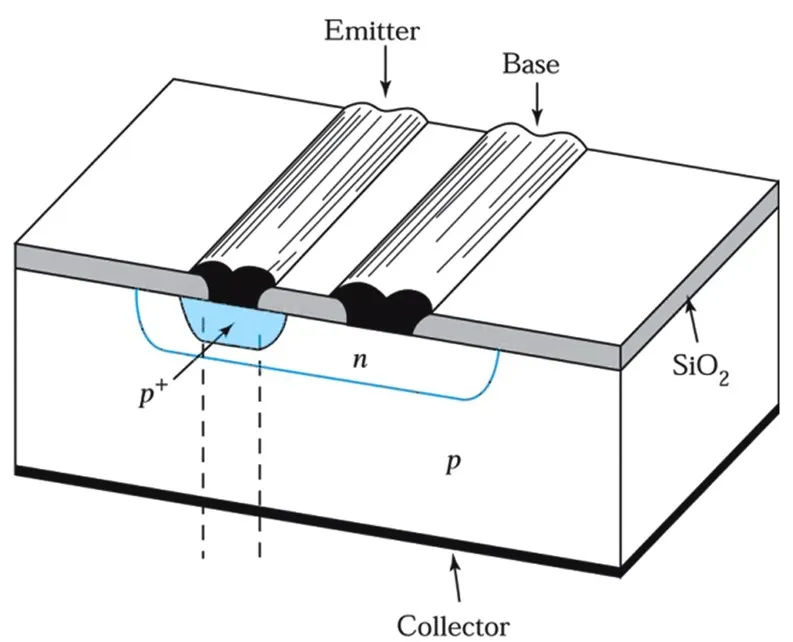

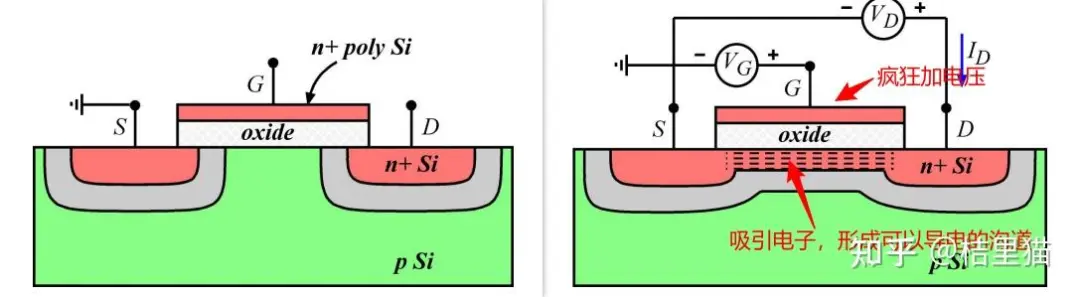

下面这个图,我们在P衬底上挖出两个n+区域,相当于形成了两个背靠背的PN结。

两个n分别连接源极和漏极。同时中间有个gate端,实际上和下面的衬底中间有绝缘层。这就是我们晶体管的基本原型。

下面我们来讲工作原理。首先我们在G端加一个电压,当这个电压足够大时,大于阈值电压(参考上面的PN节阈值)由于场效应的的存在,吸引足够多的电子,两个n会被连起来,形成一个沟道。

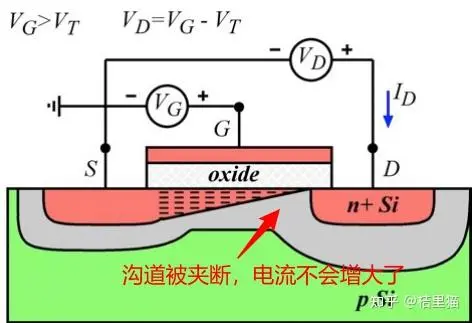

当Vg>Vth, 且Vg-Vd > Vth,此时我们的晶体管处于线性区。沟道和S和D都联通,电流可以在D和S之间流动。

当我们继续加大Vd, S和D之间的电流不断增大。

但Vd足够大后,此时会导致Vd-Vd

最终,SD之间的电流ID,和VD, VG之间的关系如下图。

所以mosfet通过Vg来控制有没有电流。Vg>Vth有电流,反之没有。

此处留一个小问题供大家思考(实际上是一个常用的面试题),我们常说的数字电路中,晶体管工作在线性区还是饱和区?为什么?

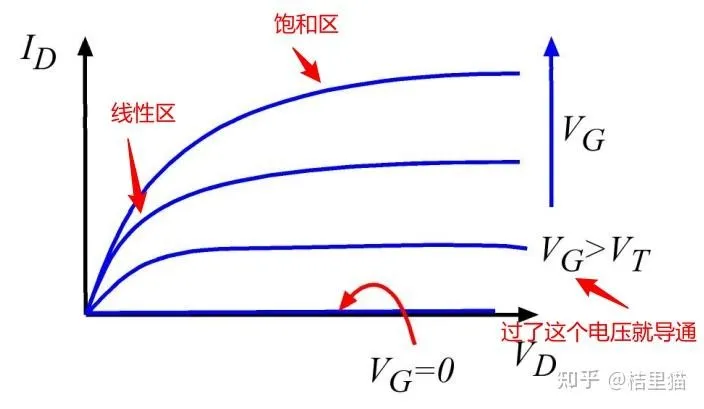

你可能注意到,gate端,第一张图画的是金属铝,后来几张图已经换成了多晶硅Poly。多晶硅替代铝主要是两个原因。

第一,制造MOS的过程中先掺杂制作下层,然后,使用稍后形成铝金属栅极的栅极氧化物区域的栅极掩模。这么搞有一个问题。。有可能对不准,会产生寄生电容。。

第二,用铝做栅极,阈值电压比较高。早期晶体管大,阈值电压高,自然没问题,随着晶体管越来越小,铝搞不定低的阈值电压,多晶硅确可以通过掺杂的方式搞定。

至此,Mosfet的原理我们就讲清楚了,我们继续开始讲故事。

我们的故事继续从摩尔定律讲起。摩尔搞了个定律,实际上不是定律,就是他的一个判断。集成电路中晶体管数量每两年翻一番。怎么翻一番?如果晶体管大小不变,仅仅把晶体管数量做上去显然不成。你总不能指望拿到手的芯片面积每两年增大一倍?

所以践行moore定律的唯一一条路:缩小晶体管尺寸。

晶体管尺寸不断缩小,好处肯定不少。通道变短,会更容易实现晶体管的通断。毕竟沟道变短了,电流从D到S跑路的距离就会变短。第二点,晶体管变小了,相应的,寄生电容就小了,晶体管能实现更快的切换。

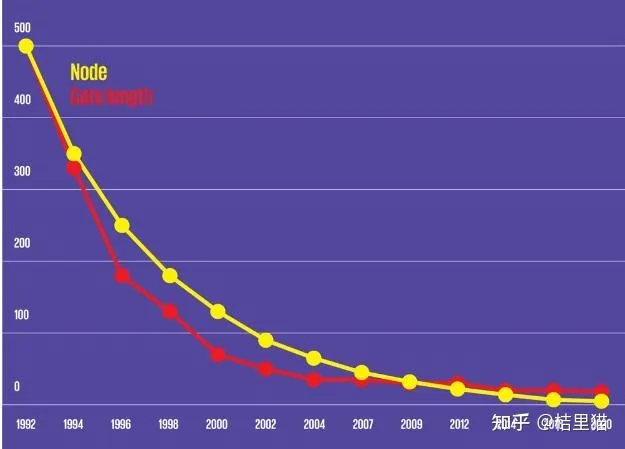

于是,人们把面积减少一半作为目标,栅极长度作为技术节点,(标准定义应该是gate长度,你理解成沟道长度也没什么不妥,反正后面就没意义了)不断演进。180nm, 130nm,90nm、65nm、45nm到28nm,再到14nm、10nm、7nm乃至5nm。

你可能会问,工艺节点是怎么定的?实际上就是一个moore定律倒果为因的结果。因为我们想让面积缩小一半,*0.5, 那么沟道作为长度,是面积的开方,所以沟道长度要缩短为原来的0.7倍(0.7*0.7=0.5)。所以每个工艺节点都是上一个工艺阶段乘以0.7的结果。

言归正传,既然缩小晶体管这么重要,那就干呗!

在缩小晶体管这条道路上,人类一路披荆斩棘。130nm以上手段比较单一,直接做小就可以,130nm以下,需要有其他技术。在90nm搞出应变硅技术,在65/45nm搞出高K介电质。这个阶段主要是平面晶体管。当然,再往后,肯定还有招,我们后面再讲。

我们可以看到,hi-k材料+metal的组合代替多晶硅后,似乎好造一些。

至此,我们现有的技术可以把晶体管缩小到32nm制程,再往下呢?难搞了。

说SOI和Finfet相爱相杀,实际行也不准确。他两中finfet明显统治力更强。

但这两个给moore定理续命的技术方案,实际上是同一个人提出来的。

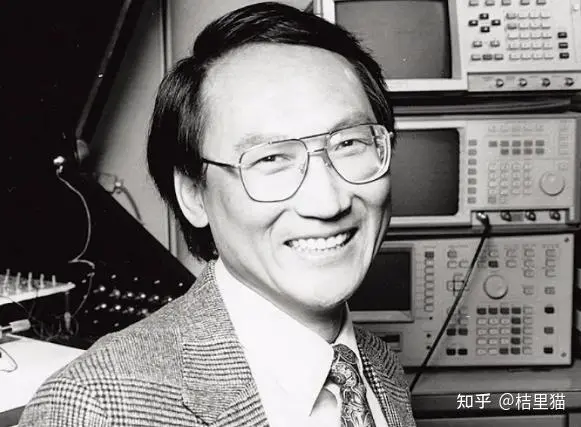

这又是一个传奇的名字——胡正明。

美国有个牛逼的存在——DARPA, 美国国防高级研究计划局。会经常掏钱,给美国规划科技的路子。

DARPA早在1995年就很敏锐的觉得,晶体管发展到25nm以下可能有问题,所以提出一个计划交“25nm计划”,要钱给钱,要人给人,等着有牛人来揭榜。

而胡正明正好做了好多关于晶体管的理论研究,是这方面的专家。但实际上由于信息差,DARPA这消息到他耳朵里的时候还剩1周时间deadline, 不过好在艺高人胆大,用一周时间画了个草图交给了DARPA。DARPA还就真给钱了。直接给了4年研究经费。

实际上类似于FinFET概念以前就有人提过,只是大家觉得做不出来。胡正明带着他的学生们真的做出来了这个器件。

2000年,DARPA资助结束,该掏出成果了。胡正明把自己的两个方案都发了文章,立刻引起了轰动。但实际上并没有被工业界立即用起来。为什么呢?

因为DARPA眼光实在是太超前。。。这个时候工业界还在玩150nm的工艺。根本不需要这种25nm的玩意儿。

等到10年后,FinFET在28nm开创了一个时代。同时,胡正明提出的另一个方案SOI也大放光彩。

总之,FinFET和SOI两种全新的晶体管,让工艺制程直接苟到了5nm, 甚至台积电的3nm也还在用FinFET。需要注意的是这两个方向不是一个淘汰另一个的关系,目前两种方案都还在用。

另外,看到这个地方的人应该不多,所以我偷偷插句题外话,大家总关心国产芯片,国产芯片能造到什么制程?目前看起来应该会卡在5nm, 而且5nm的良率在一段时间内还提不上去。主要原因我在原理部分讲。

实际上,继续把晶体管造小的思路是非常明确的—— 增强栅极对沟道的控制能力,克服短沟道效应。

那么思路也有两个:第一个方向,我们想办法把沟道做的薄,这样好控制。第二个方向,我们想办法把栅极控制面积做大,增强对沟道的控制力。

这两个方向就产生了28nm以下的两种著名的晶体管技术。第一个方向叫全耗尽型绝缘体上硅 (FDSOI, Fully Depleted Silicon-on-insulator)。第二个方向叫FinFET。

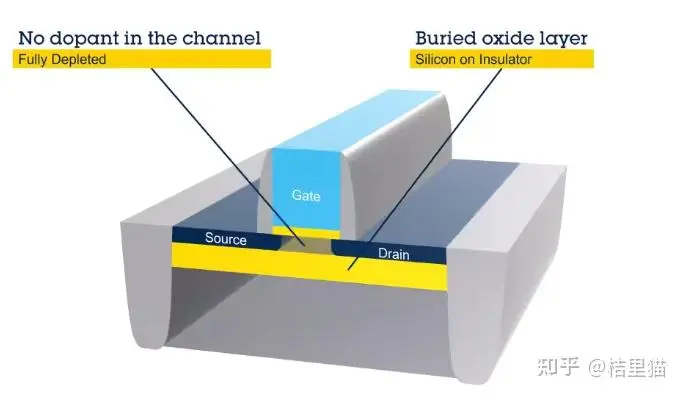

我们先来讲第一个方案。SOI。这个方案原理比较好懂。先来个SOI的3D结构图。

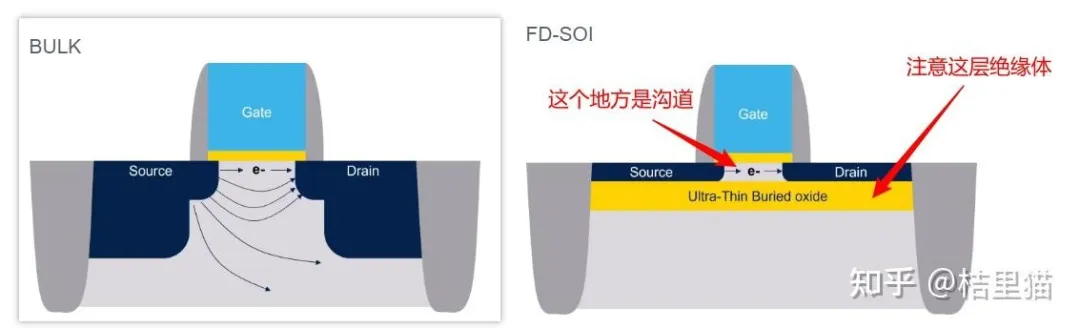

看上面这张图,左侧是原始的MOSFET。右侧是新的SOI结果。左侧gate对沟道控制力弱很大的一个方面是漏电流会从沟道下面漏过去,我们直接在下面搞一层绝缘体,杜绝这一部分漏电流,我们就可以把沟道做的更短。主要原理是源级和漏级除了沟道,不再有半导体连接了。

所以称之为绝缘体上硅。这种搞法的好处之一是制造简单,工艺和原来的平面晶体管似乎也没有太大区别。SOI的劣势在哪儿呢?到底还是平面的,晶体管继续缩小就有点乏力。

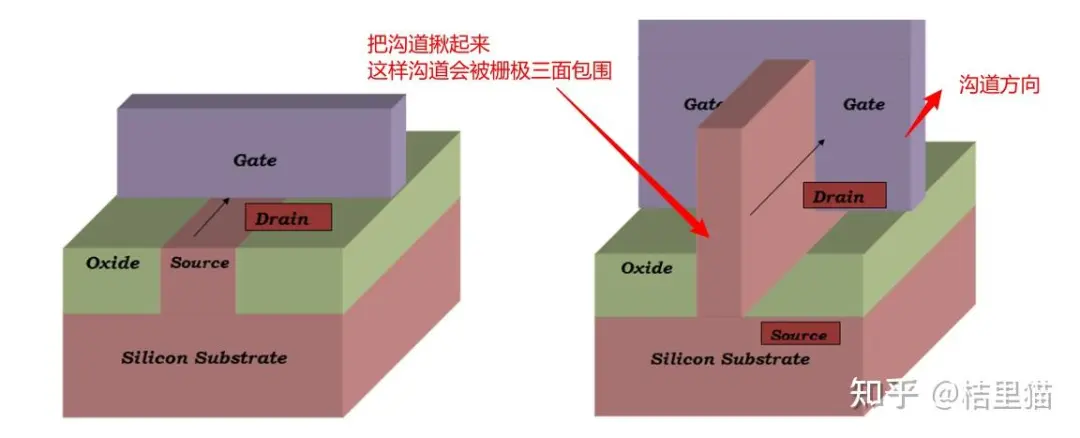

我们再来讲第二个方向,FinFET。

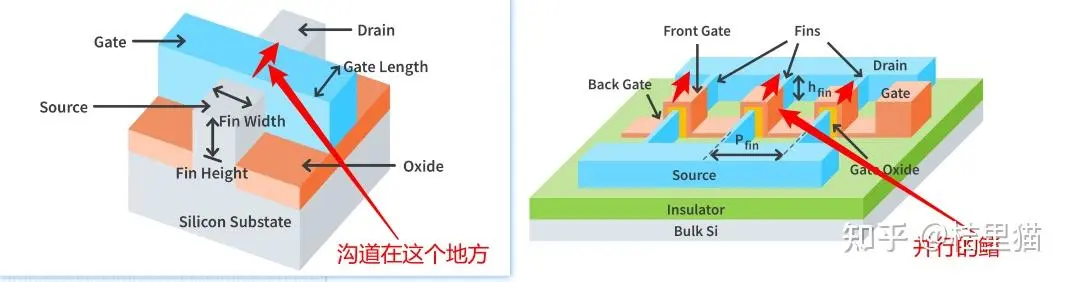

FinFET的思路比较简单。我们把沟道揪起来,让栅极三面包围住沟道,这样栅极对沟道的控制能力自然就加强了。

如上图,直观上讲,左侧是原始的MOSFET, 右侧是新的FinFET。沟道从三面被栅包围,栅的控制力显然会比左侧栅放在沟道上面对沟道控制力强。

如果上面那个图你还理解,我们用下面这个图再讲讲。我在图上画出了沟道的方向。左侧这个沟道只有一个鳍,实际上我们为了进一步增强栅极对沟道的控制力,把沟道揪起三个鳍,进一步增加栅和沟道接触的表面积。

电子显微镜照出来是这样的。

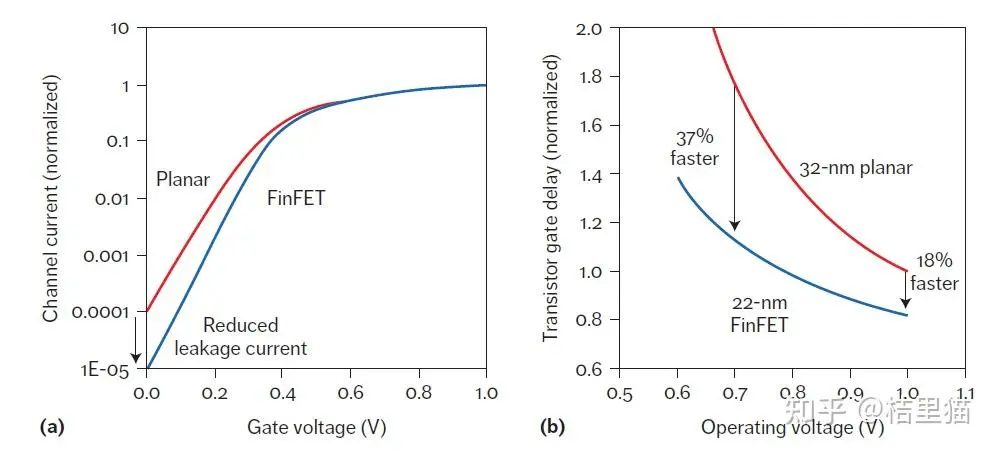

看看实验结果,FinFET在漏电流和速度上均比原来的平面晶体管好。

恩,然后填个坑,为什么说我国自主生产的芯片容易停在5nm,且良率提升比较难。

主要原因是我们搞不来EUV,只能DUV。光刻精度实际上有个著名的公式:

其中,分母取决与透镜,我们先不谈。λ是波长,n是光浸润的折射率。我们只有DUV, 没有EUV,λ天然劣势。

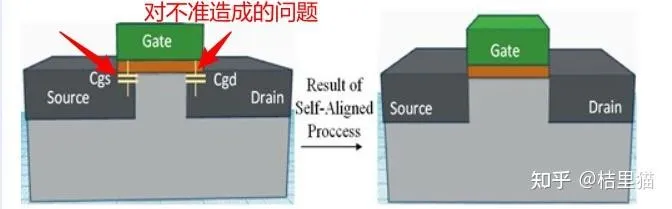

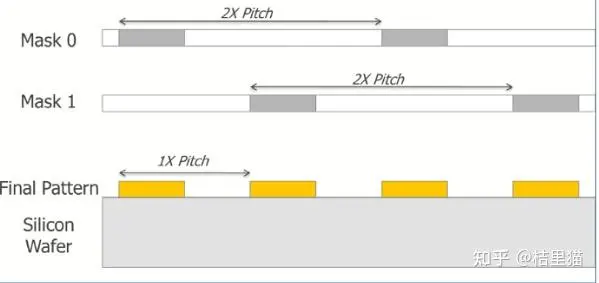

只能减少k。目前采用的方式是多重曝光。

原理很简单,如上图,既然一层曝光搞不定精度了,那我们多做一张掩膜,分多次来光刻芯片。实际上多次曝光对齐是非常困难的事儿。一方面,生产时间变大一倍,一旦对不准,还非常容易影响良率。毕竟,上面讲了是两层光刻。实际以上要高出5nm来,需要的曝光层数可能有七八层。。

(END)

文章来源:半导体全解公众号