本文编撰:Koen Noldus,流程与平台架构师

功耗、性能和面积(Power、Performance、Area,PPA)是表征晶圆工艺技术能力的三个关键指标:

功耗是指集成电路消耗的功率。它由供电电压和电流消耗决定。

性能指的是电路的带宽或工作频率。性能也可以指精度或分辨率,或者高压器件的导通电阻。

面积是指集成电路占用的硅片面积。

采用特定工艺技术设计电路的竞争力体现在低功耗、高性能(或最小分辨率,以 mV/LSB 表示)和小硅片面积这几个特征。在电路设计过程中,这三个变量构成了一个基本的权衡关系。例如,当性能提高时,可能会以增加功耗和晶粒尺寸为代价,或者当晶粒尺寸减小时,可能会导致性能降低。根据不同的电路,存在不同的权衡,从而导致不同的电路优化结果。

不同技术节点之间,其工艺技术的功耗、性能和面积特性及其最优组合也各不相同。在较小的工艺节点上设计的电路通常能够实现更优的总体PPA得分,即在更小的面积和更低的功耗下实现更高的性能。

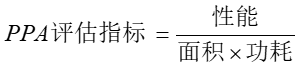

传统上,PPA的评估指标由以下方程表示:

随着性能的提高,面积和功耗的降低,PPA 的总得分也越高。

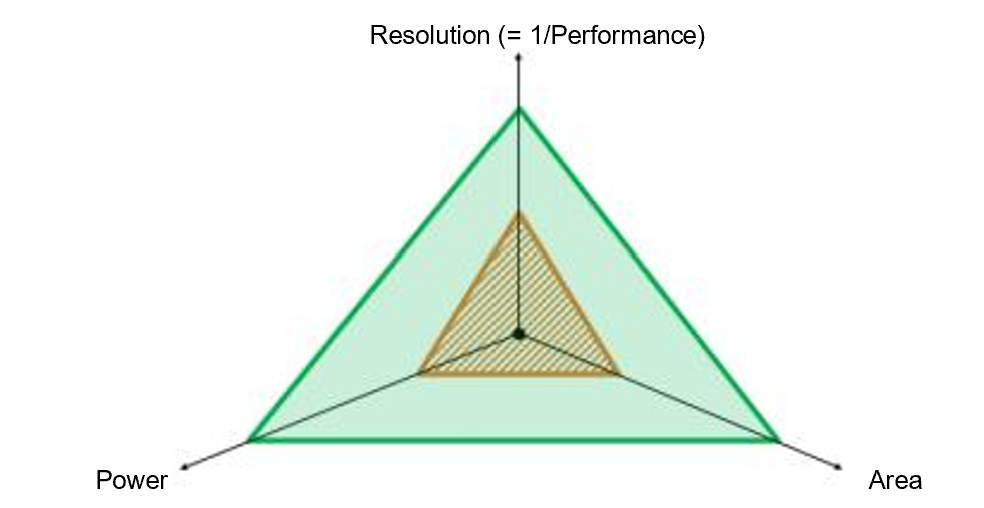

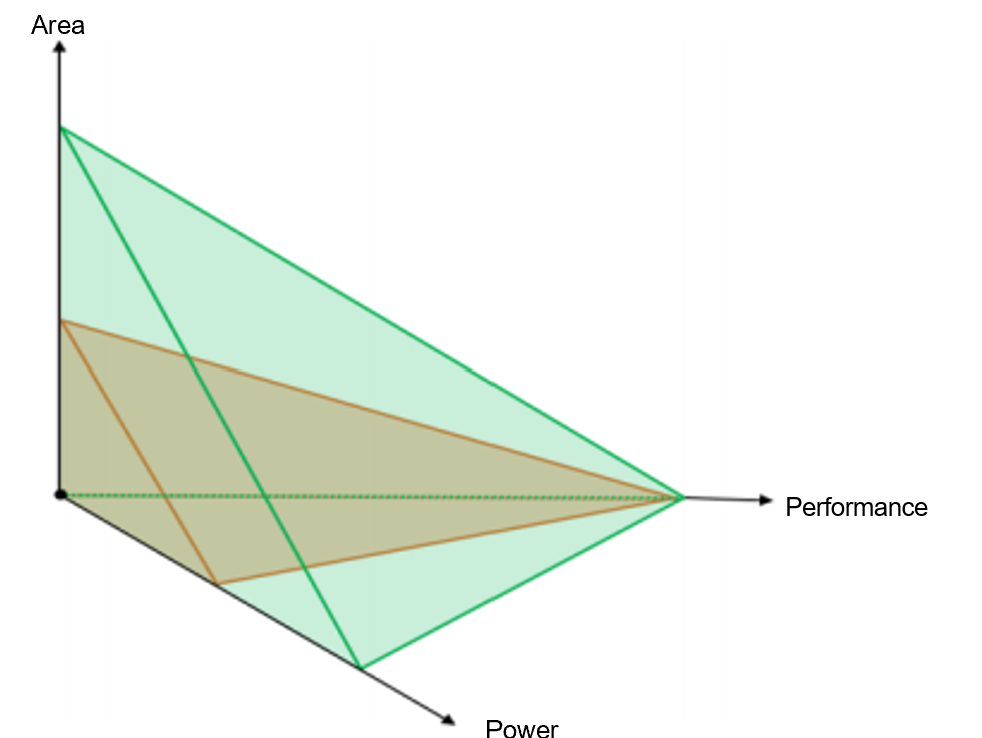

另一种以直观方式表示各代技术之间相互的方法是三角形(2D)或金字塔(3D)。在图 1 中,整体性能用 3 个坐标轴来表示。

图1. PPA三角形作为工艺技术评估指标示意图

一个轴代表分辨率,其中理想电路指尽可能高的分辨率(零分辨率对应于无限精确的系统)。第二个轴代表硅片面积,其中理想电路以无限小的面积提供相应功能。第三个轴代表功耗,其中理想电路以无限小的功耗实现相应功能。然而,在现实中,每个电路都需要一定的硅片面积和功耗,并且实现大于零的有限分辨率。

如图 1 中的三维图所示,由原点和 PPA 三角形定义的金字塔体积表示工艺技术的竞争力。在比较不同电路和技术节点之间的 PPA 时,PPA 三角形的顶点越靠近中心,电路的 PPA 分数就越高。终极工艺技术具有无限小的功耗、硅片面积和无限精确的分辨率。

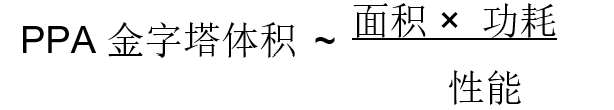

在这种表示方法中,整体性能由金字塔的体积决定:

金字塔图是估算实现特定性能所需资源数量的直观方法。

本文采用 PPA 作为评估指标,对安森美 Treo 平台,采用65 nm BCD 工艺技术(BCD65 - 2.5 V)和以前的工艺节点(180 nm - 3.3 V / 5 V)进行了比较。通过比较技术参数和特性,阐明了所选工艺技术对功耗、性能和面积的影响,并讨论了 BCD65 相较于之前工艺节点的改进之处。已经使用BCD65设计或从180nm工艺迁移到65nm工艺的模拟IP,为PPA得分的提高提供了真实可靠的证据。本文还讨论并比较了实际电路示例。

安森美Treo平台还提供工作电压范围在5V - 90V的高压器件。低Rsp(比导通电阻,单位为mΩ*mm²)的DMOS器件可以与65nm 低压模拟和数字电路在同一晶粒上集成。这种结合了低、中、高压能力的特点,在65nm BCD技术中是非常独特的。

本文以 PPA 作为评价指标,表明从 180 nm - 3.3 V / 5 V 迁移到 65 nm - 2.5 V,模拟电路平均至少达到了5倍的整体改进。基于此,安森美在 BCD 应用领域处于领先地位,实现了功耗、性能和面积的完美结合。

以下各节将分别阐述这三项关键指标。

👉功耗

工艺改进包括栅极氧化层厚度的缩小。更薄的栅极氧化层需要更低的工作电压。对于 BCD65,典型的模拟低压电源为 2.5 V,而在较早的 BCD 技术节点(如 110 nm / 130 nm 或 160 nm / 180 nm)中通常使用 3.3 V 或 5 V。这种低压电源意味着电路功耗可降低 25% 至 50%(电流消耗相同),这已经是提高 PPA 分数的一个重要因素。由于晶体管阈值电压 (VTH) 通常也会降低,因此以前的电路拓扑结构不一定需要改变,一般仍可重复使用。

在65nm 节点上,模拟电路的电流消耗通常也较低,但性能却相差无几。在保持相同带宽和增益的情况下,可以使用更低的偏置电流:相对寄生电容显著减少,在更低的电流下可以获得相同的跨导。这一点通过将IP从180nm –3.3V迁移到65nm –2.5V,并在相同性能水平上得到验证。

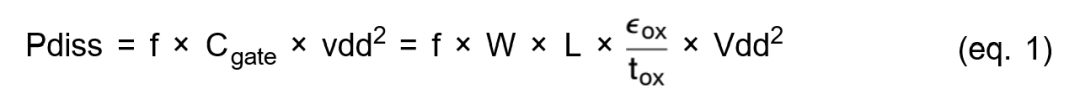

数字电路的标称电压为 2.5 V(厚栅极工艺)或 1.2 V(薄栅极工艺)。在 180 nm 节点上,标称电压分别为 3.3 V 和 1.8 V。下式表明,当 W、L、tox和 Vdd缩减时,数字功耗可以大大降低。(注意,调节tox具有相反的效果,但可通过调节尺寸和供电电压得到补偿)。特别是在 1.2 V 工艺流程中,Wmin和 Lmin显著缩小。因此,工作频率也有提高的空间。

👉硅片面积

从 180 nm 节点迁移到 65 nm 节点,每个功能(模拟、数字、高压电源)的硅片面积都有显著缩减。

对于模拟低压电路,这一点通过将一组通用电路迁移到BCD65(厚栅极氧化层工艺)并保持相似性能来证明。为了使比较有效,使用了相同数量的金属层和相同的标准器件集。结果是采用BCD65的模拟低压电路的面积减少了大约50%。

图2展示了180nm-3.3V与BCD65-2.5V比较器电路之间存在45%的尺寸差距。

图 2. 不同工艺节点间比较器电路的布局尺寸变化

这种在相似精度下的模拟(及混合信号)低压电路尺寸缩小不仅能降低晶粒成本,还允许在一个更小的封装尺寸中集成更多功能。之所以能实现这些模拟和混合信号电路尺寸缩小,主要得益于以下因素:

在半导体工艺中,较小的工艺节点通常能改善晶体管阈值电压(Vth)的匹配。因此,与工艺相关的失配系数会降低。根据Pelgrom定律,在失配程度相同的情况下,匹配晶体管的栅极面积会减小。对 180 nm - 5 V 工艺和 65 nm BCD - 2.5 V 工艺的阈值电压失配系数进行比较后发现,匹配晶体管结构的栅极面积至少缩小了两倍。而在180 nm -3.3V与65 nm-2.5 V之间,改善程度较为有限。

BCD65标准多晶硅电阻相比于安森美采用180 nm BCD技术的标准多晶硅电阻和高电阻多晶硅电阻,具有更低的失配系数。加之单元间的间距更小,匹配电阻阵列的面积减少了超过40%。

与安森美的180 nm BCD技术相比,Poly-Nwell电容在相同绝对值下具有更小的面积。这是由于BCD65技术(厚栅极工艺)中,栅极氧化层电容密度与氧化层厚度成反比,其电容密度高出30%。

除了多晶硅面积缩小之外,BCD65设计规则允许器件之间的间距更小,从而进一步提高了器件密度。晶体管的源极、漏极和栅极连接所占用的面积更小,触点面积几乎缩小了6倍。

双极型晶体管体积更小,并且表现出优异的匹配性。

BCD65 可显著减少器件互连和信号布线所占面积。后端设计规则允许更小的间距(更小的金属线宽和间距)以及更小(近 7 倍)的过孔。这并不一定会导致互连阻抗的增加:BCD65的金属层采用的是铜镶嵌工艺,其电阻比铝低35%。布线距离通常更短。

BCD65 提供了一种锥形金属化结构,使得在较低的金属层中可以实现窄且高密度的互连线路,而在较高的金属层中则逐渐变宽变厚,以支持大电流能力、电源布线和功率传输。此外,布线密度仅受限于在较高电压下某些线间间距规则。

与 180 nm - 5 V 技术相比,另一个显著的区别是器件隔离(BCD65 低压电路采用结隔离)所占用的面积。

数字库提供了更小的数字标准单元,从而实现了数字电路尺寸的显著缩小。这使得数字栅极密度提高了 3 倍(与厚栅极氧化层工艺相比)和 6 倍(与薄栅极氧化层工艺相比)。在集成电路中可以轻松添加更多的数字功能。

静电放电(ESD)保护只会轻微的减少尺寸,因为其尺寸主要由所需承受的能量决定。

在 BCD65 中,高压器件的 Rsp 值显著提高。与安森美之前的 BCD 技术相比,45 V DMOS 器件的 Rsp 值提高了 40%。

所有这些因素的结合,就会在产品层面产生显著尺寸缩小。这一点通过将产品从180 nm BCD节点迁移到安森美的Treo平台上的65 nm BCD节点得到了证明。

👉性能

前几节详细介绍了 BCD65 在电路性能与安森美之前的 180 nm BCD 节点类似的情况下,降低功耗和减少硅片面积的情况。反之亦然,在相同的功耗和面积下,基于安森美Treo 平台开发的电路在精度和带宽方面表现更佳。

更匹配的晶体管、电阻和双极型晶体管可转化为更高的精度。对于相同的电流消耗,电路可以在更高的增益带宽乘积下工作。锥形金属化结构在最低层的铜金属层上采用窄迹线,并结合更短的布线距离,减少了互连寄生效应,这对高带宽电路同样有益。

由于寄生耦合和串扰噪声较低,金属叠层下部的低 K(低介电常数)材料可实现高速运行。无论如何,低 K 材料都是持续改进工艺技术和高速运行所必需的。等式 1 中已经显示了提高数字电路时钟速度的潜力,这有助于性能的提升。

通过在1.2V薄栅极工艺流程中使用BCD65双栅极选项进行模拟设计,可以获得另一个重要的带宽提升。在薄栅极工艺流程中,晶体管的匹配度再次得到改善。1.2 V 下的模拟设计对于直接连接数字信号的模块(如 A/D 和 D/A 转换器或比较器)尤为重要。在更高频率下运行可使模数转换器 (ADC) 以更高的采样率进行时钟运算,从而实现多输入通道的多路复用或达到更高的过采样率 (OSR),从而获得更高的分辨率。

在相同的硅片面积内集成了更多功能和更先进的电路。数字电路尺寸显著缩小,可轻松增加包括MCU在内的数字功能。数字功能可用于增强模拟电路性能,并对模拟电路不完善之处进行修正。

前文解释了为什么 Treo平台 65 nm BCD技术在功耗、性能和面积方面优于 180 nm - 3.3 V / 5 V 技术。列举了许多关于不同影响因素的定性说明。本节将根据实际电路示例说明 PPA 的具体改进。

示例 1

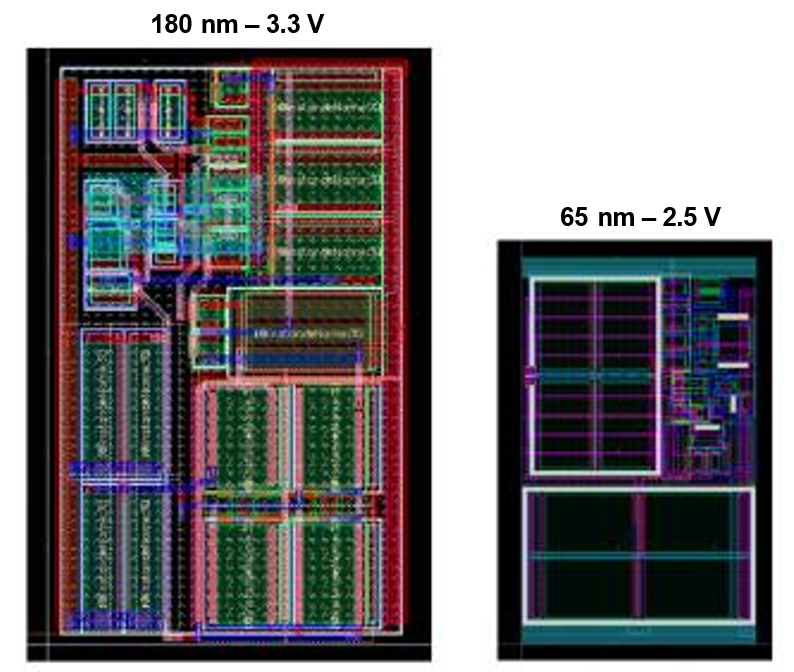

此运算放大器的设计已从安森美的 180 nm - 3.3 V BCD 技术迁移到 BCD65技术。该拓扑结构是一种广泛使用的两级放大器,称为米勒运算放大器。迁移后的电路在偏移、带宽、相对输入共模范围等方面具有相同性能。实际制造后的电路特性分析表明,与采用3.3 V 电压供电的原电路相比,迁移后的电路电流消耗减少了40%(采用2.5 V 电压供电)。原始设计和迁移后设计的布局如图 3 所示(两个电路布局的比例相同)。

图 3. 运算放大器的布局比较

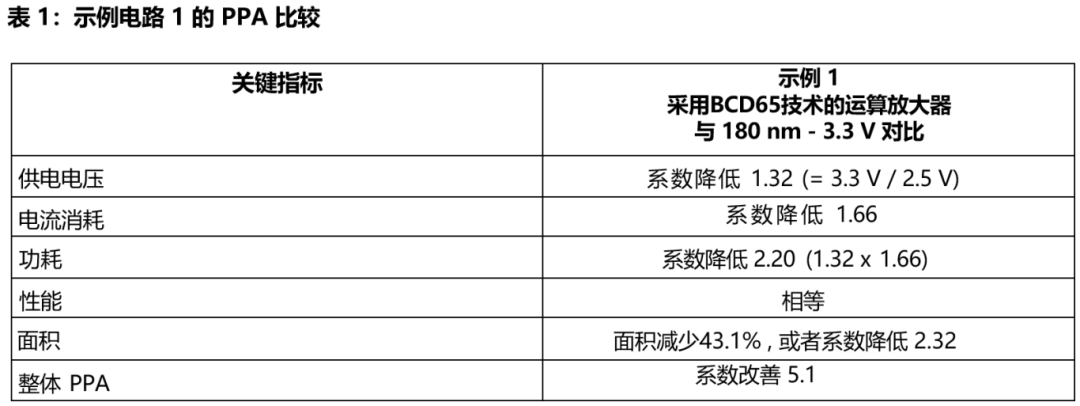

下表汇总了关键指标和整体PPA的比较:

对于这个运算放大器设计,采用 65 nm工艺技术可将整体 PPA 得分提高 5.1倍 。图 4 所示电路的 PPA 三角形是显示改进的另一种方法。绿色部分代表 180 nm - 3.3 V 设计,橙色部分代表 BCD65 设计,其性能相同,但功耗和硅片面积得到改善。

图 4. 运算放大器的 PPA 三角形

180 nm - 3.3 V(绿色)和 65 nm - 2.5 V(橙色)

示例 2

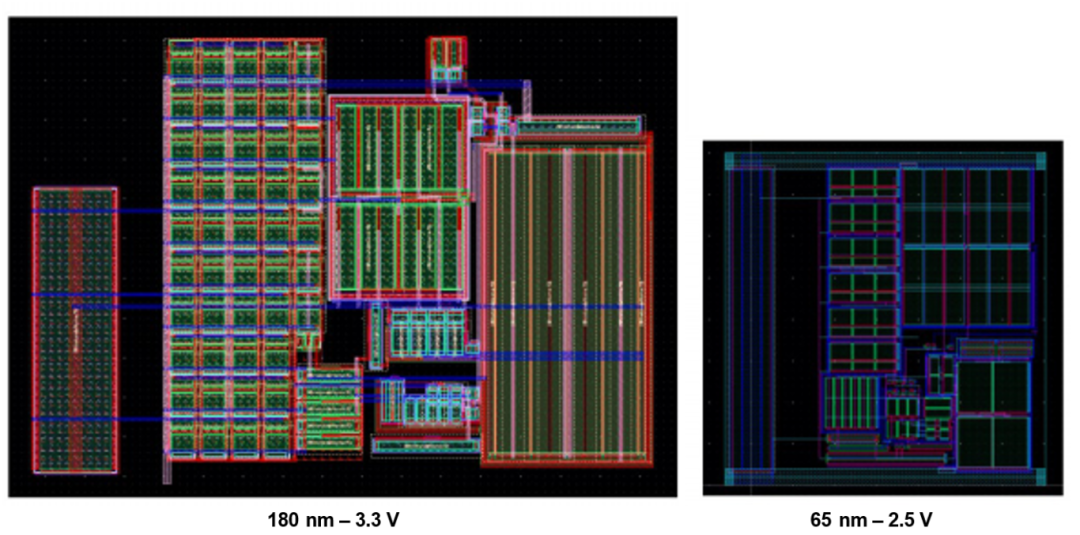

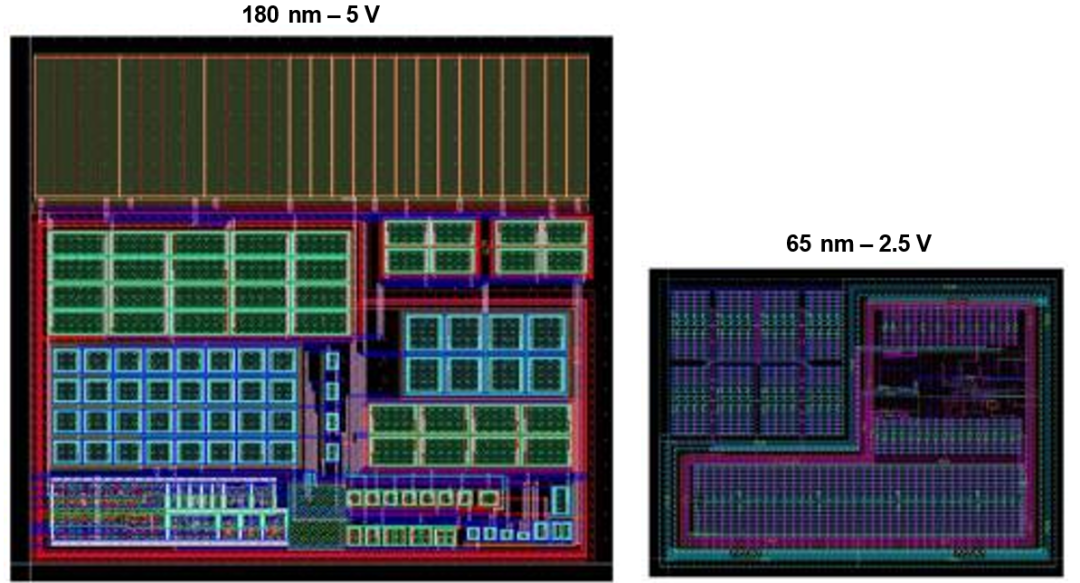

比较器设计已从安森美的 180 nm - 5 V BCD 技术迁移到 BCD65技术,在偏移、传输延迟和相对输入共模范围方面具有相同的性能。实际制造后的电路特性分析表明,与采用5V 电压供电的原电路相比,迁移后的电路电流消耗减少了31%(采用2.5 V 电压供电)。两种版本的布局面积如图 5 所示(两种电路布局的比例相同)。

图 5. 180 nm和 65 nm比较器电路布局图

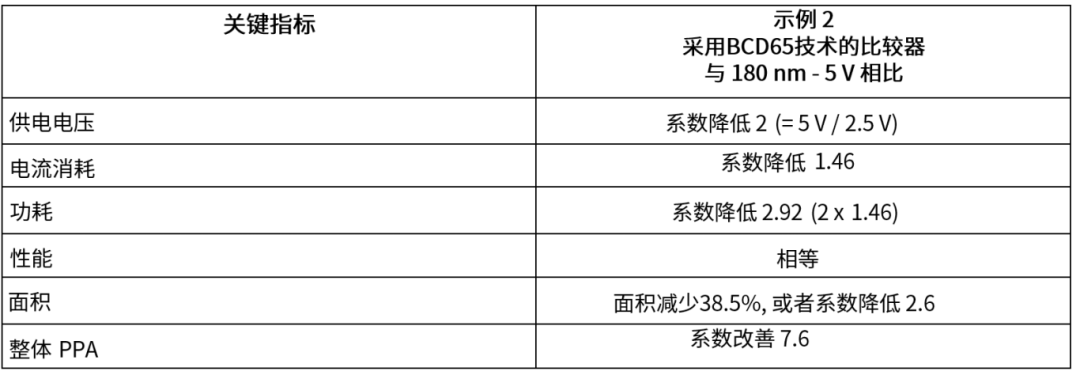

表 2:示例电路 2 的 PPA 比较

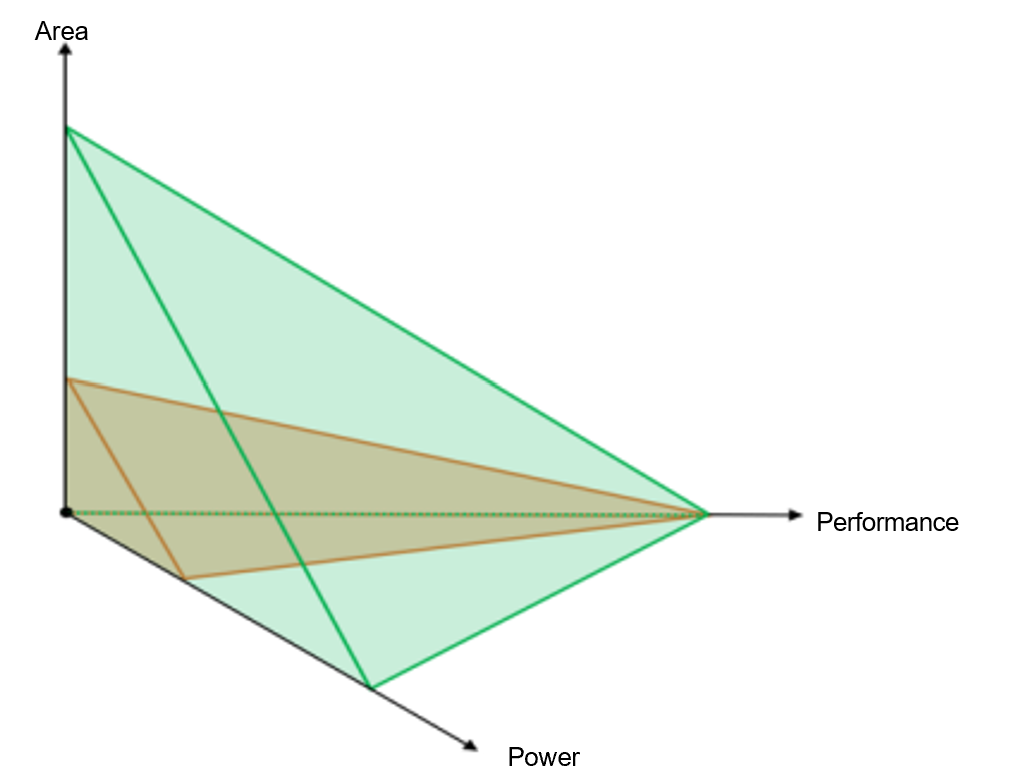

对于该比较器电路,改用 BCD65 可将整体 PPA 得分提高 7.6 倍。图 6 所示电路的 PPA 三角形是显示改进的另一种方法。同样,绿色部分代表 180 nm - 5 V 设计,橙色部分代表 BCD65 设计,性能相同,但功耗和硅片面积得到改善。

图 6. 比较器电路设计的 PPA 三角形

180 nm - 5 V(绿色)和 65 nm - 2.5 V(橙色)

根据电路类型的不同,可达到的整体 PPA 改进得分也不同。一些设计比其他设计更难缩小尺寸,或者一些设计仅在硅片面积或电流消耗方面显示出有限的优化。但平均而言,从 180 nm - 3.3 V 迁移到 BCD65技术,整体 PPA 得分可提高 5 倍以上。从 180 nm - 5 V 升级到 BCD65 时,改进幅度更大,因为降低更多的供电电压带来了更多的好处。

本文描述了三个关键指标——功耗、性能和面积,它们之间存在的权衡关系,以及如何使用PPA作为衡量标准来比较不同工艺技术下的模拟性能。以PPA作为评价指标,显示了从180 nm-3.3V /5 V BCD技术迁移到安森美 Treo平台,至少实现了平均5倍的整体改进。加上高压器件,密集的模拟低压和数字电路,使得安森美Treo平台在BCD应用中具有强大的竞争力。

安森美Treo平台在PPA方面的改进不仅限于理论层面,还得到了已经完成迁移及制造的模拟IP实践验证。工艺的改进允许更高的集成密度,在更小的尺寸内能够集成更多功能,这对于现代高性能模拟和BCD应用至关重要。

总体而言,通过向市场推出性能卓越、功耗更低、硅片面积更小的产品,安森美 Treo 平台使安森美在模拟、混合信号和高压解决方案领域处于领先地位,成为先进模拟电路设计极具竞争力的选择。

⭐点个星标,茫茫人海也能一眼看到我⭐