先进逻辑制造作为半导体工业技术的明珠,直接带动全球半导体技术发展和产业增长。在半导体技术的演进中,功耗约束下的器件微缩和集成度提升这一小一大目标始终是集成电路发展的核心。然而传统的二维平面集成方式正面临物理极限和工艺极限的瓶颈,如何实现更高密度、更低功耗、更高能效的芯片设计与制造成为半导体产业亟待解决的课题。

为此,晶体管级三维集成技术开始受到广泛的关注。这种集成方式通过在垂直方向上堆叠器件和互连,将传统的单面布局扩展至多面空间,在掩模版尺寸受限的条件下为单芯片提供了突破集成密度上限的可能。全面走向三维集成路线已经成为当前产业界的共识,但是具体的技术方案尚未统一,正处于各国技术竞争的前沿焦点。

在这样的背景下,北京大学黄如院士团队创新地提出了FFET(Flip FET)[1]技术,跳出了现有晶体管级三维集成技术专注于器件结构与工艺的常规思路,是一种全新的器件集成理念,而并非简单的器件结构技术。FFET集成方案通过创新的多面有源区和多面互连设计,可以有效支持从FinFET到GAA的不同器件堆叠需求和适配不同电源网络与信号网络的绕线需求,从根本上超越了单纯的器件结构创新,赋予集成电路制造前所未有的技术自由度和设计空间。

先进逻辑节点的演进:器件结构迈入三维

在高性能计算(HPC)、人工智能服务器和智能消费设备等领域,对芯片运算能力的需求持续高涨。这些领域需要极高的计算性能,因此往往优先采用最先进的制程工艺。市场需求的推动下,7纳米及以下的先进制程出货量快速增长,预计2022至2026年间的年复合增长率将达到27%,并将在2025年占据晶圆代工产能的64%。AI GPU和ASIC的出货量在未来几年预计年复合增长率为42%,进一步印证了市场对AI和高性能运算需求的强劲增长。由此可见,先进逻辑制程已成为半导体产业的“兵家必争之地”,推动了整个科技领域的快速发展。

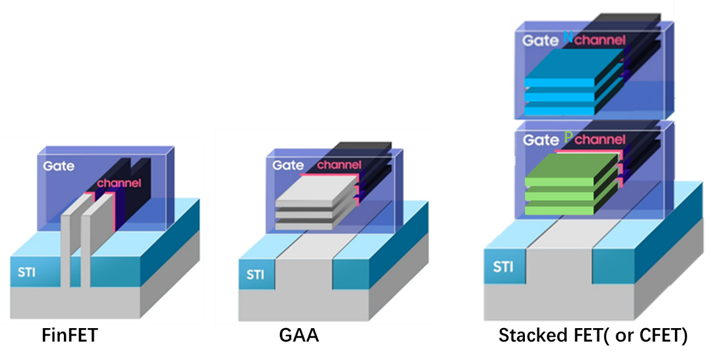

图一:先进逻辑晶体管的技术演进

先进逻辑制造技术的发展历程充满了革新与挑战。从早期的平面MOSFET到三维结构的FinFET[2],每一代器件架构的出现都代表了集成电路在性能、密度和功耗方面的新突破。FinFET技术作为传统平面器件的延续,以其三维鳍状结构有效提高了栅极对电流的控制能力,降低了漏电流并增强了开关速度。然而,随着节点的演进,FinFET进一步微缩的难度也在日益增大。为应对这一挑战,GAA技术应运而生[3]。在GAA技术中,沟道被栅极四面包裹,这种围栅设计进一步增强了对电流的控制,显著减少了短沟道效应,因而能够适应更小的制程节点。台积电等主要厂商计划在2纳米节点引入GAA技术,并预计将于2025年量产,标志着行业正式进入GAA时代。

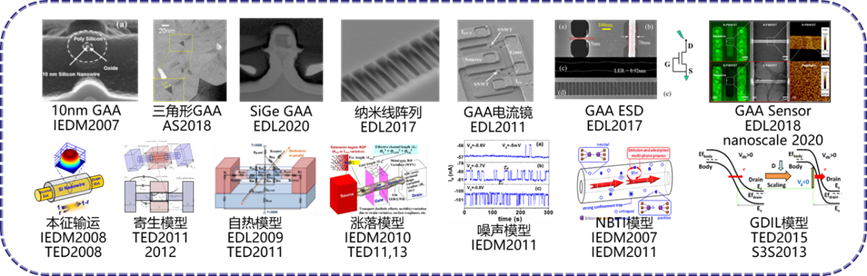

在国内进展方面,北京大学在这一领域的研究起步早、布局深, 2007年北大在IEDM上发表国内第1篇(全球第4篇)GAA器件论文[4],在后续十多年里持续进步并与产业机构开展了广泛合作,率先在国内建立了从基础研究到器件设计的完整技术链。

图二:北京大学在GAA器件领域的技术贡献

先进逻辑节点的未来:呼唤新型三维集成方法

值得指出的是,即使采用了GAA等先进的三维器件结构,基于平面的集成方法仍然难以突破物理瓶颈的限制。为追求更高的集成度和性能,晶体管级三维集成成为逻辑技术节点升级的必然技术路线。

目前,在传统的系统级三维封装集成路线之外,单芯片上的晶体管三维堆叠集成正在成为主流技术趋势,这不仅是在晶体管结构上作出改变,更是通过堆叠晶体管来高效利用空间和降低寄生效应,从而大幅提升器件密度和性能。更为重要的是,这种集成思路可以依赖现有光刻技术和设计能力将集成电路的集成度持续提升,实现真正意义上的三维等效微缩。这一技术思路上的转变从2016年前后国际半导体技术路线图从传统的ITRS升级为IRDS即可窥见端倪。然而,直至今日,真正意义上的单芯片三维集成的技术方案尚未得到真正确立,面临着从材料、器件、工艺到设计各层次的全面挑战。这一时期,正是集成电路领域在后摩尔时代前所未有的第二次技术革命机遇。

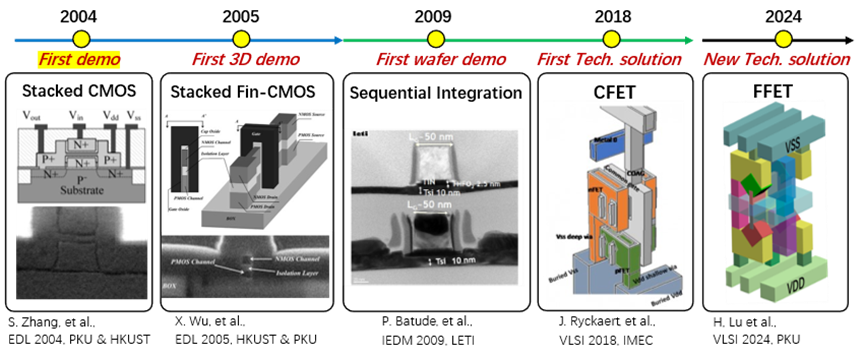

图三:晶体管级三维集成的发展历程

晶体管级三维集成的研究至少可以追溯到2004年,当时,北京大学和香港科技大学的研究团队首次在实验中成功验证了堆叠晶体管的可行性,并命名为“Stacked CMOS”[5], [6]。随后,2009年,法国的CEA-Leti研究团队通过晶圆键合技术实现了晶圆级的器件堆叠[7]。到2018年,欧洲微电子研究中心IMEC进一步发展了晶体管堆叠技术,提出了可大规模集成的原型技术即CFET[8]。这一方案采用了单片堆叠路径,具备更高的实用性,也展示了在未来半导体技术中应用的潜力。这一系列成果使三维堆叠晶体管从实验室走向了规模实践,前后耗费14年时间,但其制造复杂性和互连限制仍未完全解决。尽管IMEC、台积电将晶体管三维集成称为CFET,但英特尔、三星、IBM一直延用3D stacked FET这一名称。然而,当前CFET器件技术受制于高深宽比(AR)工艺和复杂制造流程,实际应用面临很大挑战。

与此同时,在传统互连架构中,电源和信号需要共用正面布线资源,带来了布线拥塞和高RC延迟,因此以背部供电网络(Backside Power Delivery Network, BSPDN)技术为代表的晶圆背部互连技术[9]开始在英特尔、三星、台积电等公司进入实质性的研发阶段,可以认为是一种互连的三维堆叠。BSPDN方案将电源传输放置在芯片背面,从而降低了正面互连布线的面积开销,减轻了功耗与延时的负担。然而,BSPDN在制造流程中存在很大的技术挑战,包括需要衬底的极致减薄和双面精准光刻对准等。不过,随着台积电今年宣布将在A16节点上大规模量产晶圆背部供电技术,说明相关工艺问题已经攻克。

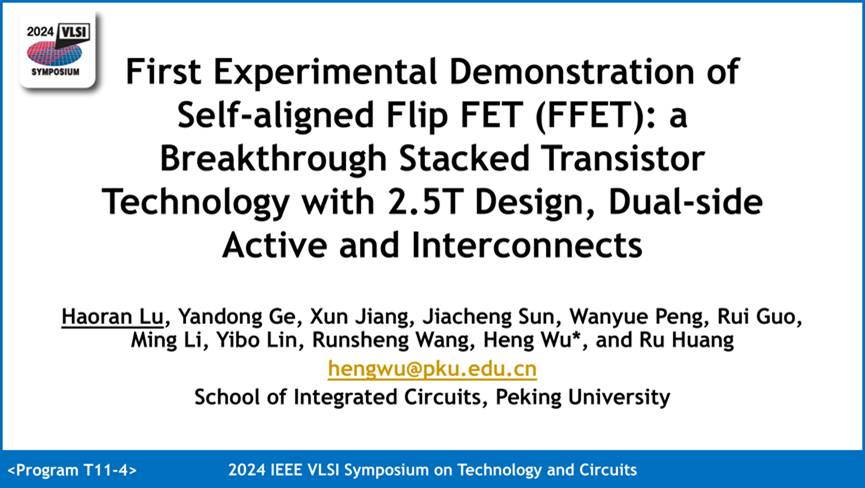

不同于上述正面晶体管堆叠和背部互连的三维集成架构,北京大学黄如院士团队提出了全新的倒装堆叠晶体管[1](Flip FET,FFET)技术,开创性地提出了双面有源区(Dual-side Active)和双面互连(Dual-side Interconnects)的概念,为单芯片三维集成开辟了全新的技术路线。该研究成果发表于2024年6月召开的集成电路顶级会议VLSI2024。

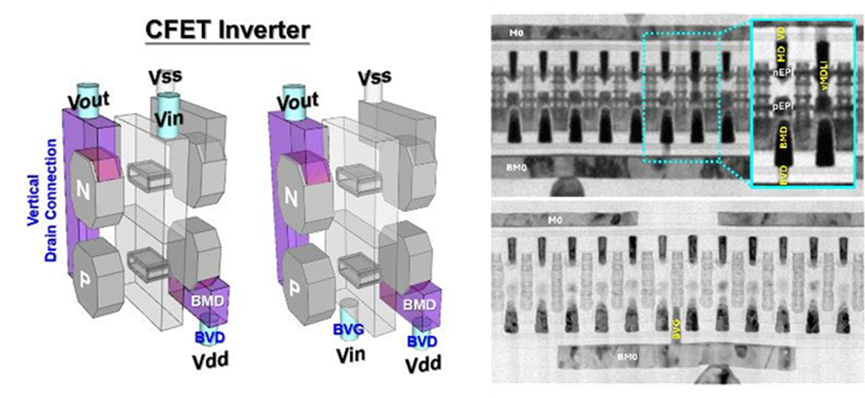

无独有偶,在此后的IEDM2024 Press Kit的中《Paper 2.5, TSMC’s Fully Functional Monolithic CFET Inverter at 48nm Gate Pitch》[10]可以看到,台积电在最新的CFET进展中也几乎同时引入了双面供电与双面信号互连的布局概念(如图五),并实验展示了晶圆键合和翻转(Bonding + Flipping)技术的可行性,也证明了FFET技术涉及的极致晶圆减薄和双面光刻技术的可行性。

图五:台积电将于2024年12月IEDM大会上公布的CFET结构图

图五:台积电将于2024年12月IEDM大会上公布的CFET结构图

但是从技术思路来看,二者存在根本上的差异,现有的正面CFET加背部互连的方式仍然延续了晶圆键合的传统三维集成方式,而FFET更倾向于等效利用晶圆的双面集成空间,从而拓展了器件与互连集成布局的适用范围,理论上具备了与平面集成方式一样的技术迭代能力,等同于三维版的等比例缩小法则。

为此,芯思想特别联系了北京大学集成电路学院黄如院士团队该工作的负责人吴恒博士,对该工作进行详细解读。

FFET工艺:化繁为简,从“倒装”到“自对准”

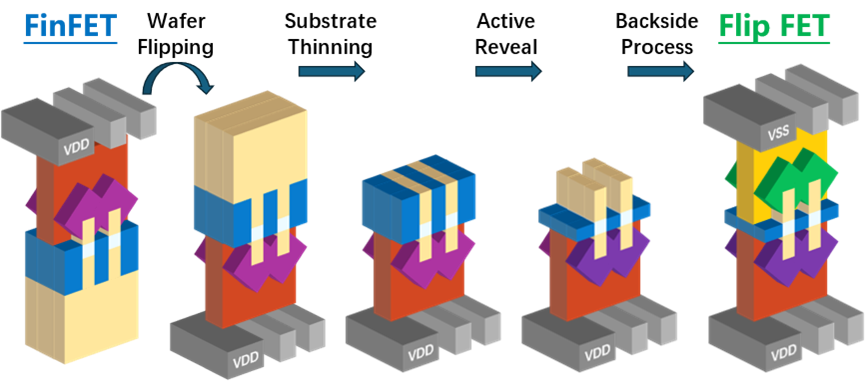

图六:FFET技术工艺流程一览

图六:FFET技术工艺流程一览

FFET技术的最大亮点之一在于其独特的“双面有源区 + 倒装 + 背靠背自对准”设计。不同于CFET依赖复杂的晶圆正面层叠工艺,FFET通过在晶圆的正反两面分别构建N/P型晶体管,实现了双面有源区的器件设计,其在结构上具有高度的对称性和互补性。

具体而言,如图六,FFET的制造流程相对直观简洁。首先,在晶圆正面构建出FinFET器件后,将其与载片键合并翻转。接着,做衬底减薄,直至完全去除衬底。随后,通过自对准的方式对STI氧化物进行刻蚀,从而露出Fin结构的背面并构建背面的晶体管。

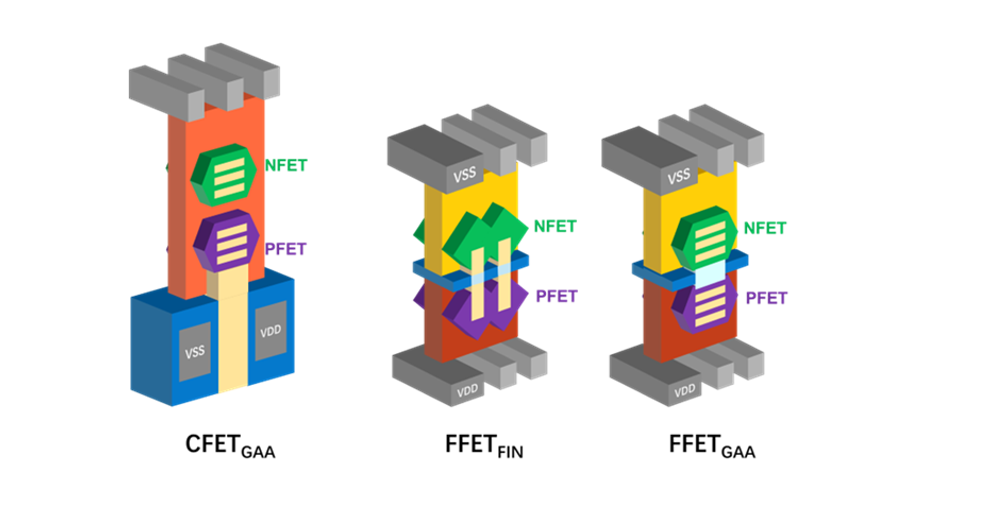

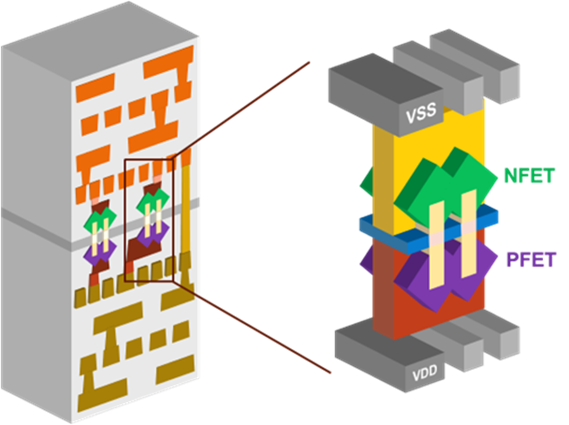

这种双面自对准堆叠的方法,可大幅降低对高精度设备的依赖,双面独立的器件制造也绕过了大深宽比工艺的开发,在保持高集成度的同时有效降低制造成本。吴恒博士也特别指出(图七),FFET并不是一种器件结构技术,而是器件三维集成的新架构。其不仅适用于Fin结构的堆叠,还适用于下一代GAA纳米片,具有很强的拓展性。

图七:CFET与FFET器件结构对比

FFET互连:首倡双面信号与供电,打破传统的互连瓶颈

FFET技术的另一大亮点是其双面互连设计,使得信号和电源布线都能在正反两面进行,从而大幅提升了电路的互连能力。作为三维集成技术的新概念,FFET不仅延续了CFET器件堆叠的密度优势,还突破了只能在单面布线的局限。不同于CFET只能在正面布置信号线、背面布置电源线的设计,FFET允许信号和电源线在正反两面灵活布局。

这种双面布局不仅提高了信号传输的效率,还为未来超大规模集成电路设计带来了新的灵活性。双面供电设计优化了电源传输路径,有效降低了寄生电容和电阻,使晶体管运行更快、更节能。

图八:FFET技术所引入的双面互连新概念

FFET集成:从平面到三维,开拓超越物理极限的微缩路径

在摩尔定律放缓的当下,业界普遍借助设计工艺协同优化(DTCO)所驱动的“超微缩”概念来推动尺寸微缩,如降低单元高度和宽度等。作为“超微缩”技术的最后一环,之前一般认为CFET可实现3T单元高度(T为track,即金属轨道)已接近微缩的尽头。

FFET的提出,为未来的微缩带来了新的方案。得益于双面有源区和双面互连设计,FFET中上下器件的集成变的更加紧凑,可推进微缩至更小的2.5T的极限高度,从而大幅提升集成度。设计数据也显示,FFET的双面器件和互连布局使得SRAM的面积更小,比CFET的SRAM减少了12%,FFET在等功耗下频率提升达21.5%。

图九:FFET提供了极致微缩的可行性方案

FFET进阶F3D:开启后摩尔时代集成芯片新路径

FFET为先进逻辑制程微缩提供了新方案,然而吴恒博士还指出,其潜力却不止如此。

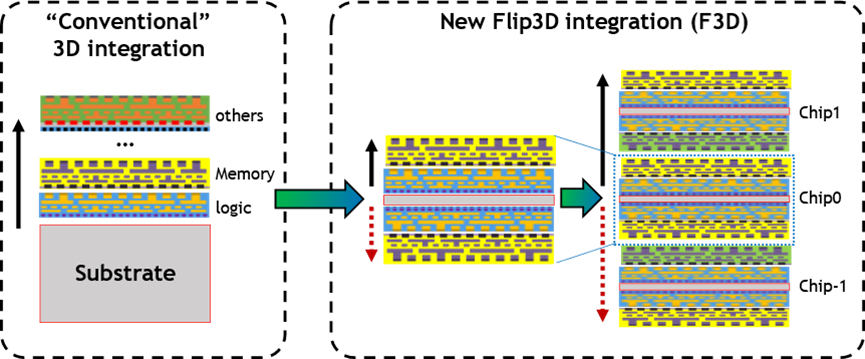

FFET的衍生技术:倒装三维集成技术——Flip 3D(F3D),则为未来多层堆叠和高性能计算提供了广阔的应用前景。F3D实现了在晶圆正反两面堆叠功能单元,可突破单片三维集成(Monolithic 3D,M3D[11])等传统单面集成的限制。继2024年6月于VLSI2024大会公布的进展之后,在2024年10月的ICSICT2024[12]会议上,北京大学黄如院士团队正式公布了F3D技术。

图十:北京大学于2024年10月ICSICT会议上公布的F3D技术[12]

传统的M3D技术通过在单一晶圆表面堆叠多个器件层,依赖晶圆级键合或薄膜转移工艺实现多功能集成。虽然M3D可以让逻辑、存储、传感器等功能层垂直互连,但随着器件缩小,M3D在高密度集成方面面临诸多挑战,如层间寄生、器件耦合、热管理和互连带宽等问题。

得益于正反面独立的制造工艺,F3D芯片的正面可以布置高性能计算单元,背面则用于高密度存储单元。这种双面电路功能设计还支持多种组合方式,如逻辑+存储、存储+存储、逻辑+逻辑等,为高性能计算芯片提供了更多的集成可能性。更进一步,因双面功能的芯片设计,F3D技术还支持双面混合键合。使得晶圆正反两面进行堆叠和互连变为可能。这可以有效缩短芯片层间信号传输路径,减少寄生电阻和电容,大幅提升数据传输速度和能效。可以看出,相比于M3D技术,F3D独特的双面布局更加灵活,可显著降低信号延迟,在高速计算场景下展现出更优的性能。

图十一:倒装三维集成技术(F3D)

以城市规划比喻集成电路的发展

吴恒博士有个形象的比喻,从某种角度看,未来半导体技术的发展堪比人类城市建设的宏伟蓝图。

图十二:未来的半导体技术发展类比城市规划[13]

如果将集成电路比作城市,早期的晶体管技术类似于传统的平面布局,所有建筑都位于同一层面。随着技术进步,GAA和FinFET等三维结构的出现犹如城市建筑向高层发展,利用垂直3D空间增加了容纳量。然而,仅依靠单个高层建筑仍不足以缓解“城市”中的“交通”压力,也无法支持更大的“人口”需求。FFET则像是“双面城市”,不仅将“建筑”布局在地上,还在地下设立了不同的功能区,形成了真正的三维结构。F3D更是将这一概念拓展到“垂直城市”,使得城市效率大幅提升。这样,有限的空间被充分利用,“城市”的整体效率得以大幅提升,为未来的发展提供了坚实基础。

在这个类比中,FFET和F3D技术为未来的集成电路提供了如同现代城市规划的“立体蓝图”,使得芯片在有限的空间内能够承载更多的功能和算力。这种从二维到三维的集成演进新方法,有望为未来超大规模集成电路提供更有力的技术支持。

结语:FFET与F3D技术引领三维集成电路新方向

在当前摩尔定律放缓的背景下,FFET技术凭借双面有源区和双面互连架构,首次提出晶圆双面集成的新概念,为半导体行业带来了的新思考和解决方案。这一技术可极大地提升芯片集成度和互连性能。FFET进一步发展出的F3D技术则通过双面多层堆叠,将三维集成的极限再次推进,具有更广阔的应用前景。

FFET和F3D的出现不仅为高性能计算和大数据处理提供了新方向,也侧面印证了集成电路从平面到三维的演进趋势。未来,随着三维集成技术的不断成熟,我们有理由期待FFET和F3D技术成为新一代集成电路的中坚力量,推动半导体产业进入更加灵活和立体的新时代。

参考文献:

[1] H. Lu et al., “First Experimental Demonstration of Self-Aligned Flip FET (FFET): A Breakthrough Stacked Transistor Technology with 2.5T Design, Dual-Side Active and Interconnects,” in 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA: IEEE, Jun. 2024, pp. 1–2. doi: 10.1109/VLSITechnologyandCir46783.2024.10631460.

[2] S.-Y. Wu et al., “A 3nm CMOS FinFlexTM Platform Technology with Enhanced Power Efficiency and Performance for Mobile SoC and High Performance Computing Applications”, in 2022 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, DOI: 10.1109/IEDM45625.2022.10019498.

[3] G. Bae et al., “3nm GAA Technology featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications,” in 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA: IEEE, Dec. 2018, p. 28.7.1-28.7.4. doi: 10.1109/IEDM.2018.8614629.

[4] Y. Tian et al., “New Self-Aligned Silicon Nanowire Transistors on Bulk Substrate Fabricated by Epi-Free Compatible CMOS Technology: Process Integration, Experimental Characterization of Carrier Transport and Low Frequency noise,” in2007 IEEE International Electron Devices Meeting, Washington, DC, USA: IEEE, 2007, pp. 895–898. doi: 10.1109/IEDM.2007.4419094.

[5] S. Zhang, R. Han, X. Lin, X. Wu, and M. Chan, “A Stacked CMOS Technology on SOI Substrate,” IEEE Electron Device Lett., vol. 25, no. 9, Art. no. 9, Sep. 2004, doi: 10.1109/LED.2004.834735.

[6] X. Wu, P. C. H. Chan, S. Zhang, C. Feng, and M. Chan, “A three-dimensional stacked fin-CMOS technology for high-density ULSI circuits”, IEEE Transactions on Electron Devices ( Volume: 52, Issue: 9, September 2005) , DOI: 10.1109/TED.2005.854267.

[7] P. Batude et al., “Advances in 3D CMOS sequential integration,” in 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA: IEEE, Dec. 2009, pp. 1–4. doi: 10.1109/IEDM.2009.5424352.

[8] J. Ryckaert et al., “The Complementary FET (CFET) for CMOS scaling beyond N3,” in 2018 IEEE Symposium on VLSI Technology, Jun. 2018, pp. 141–142. doi: 10.1109/VLSIT.2018.8510618.

[9] S. Lee et al., “Breakthrough Design Technology Co-optimization using BSPDN and Standard Cell Variants for Maximizing Block-level PPA,” in 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan: IEEE, Jun. 2023, pp. 1–2. doi: 10.23919/VLSITechnologyandCir57934.2023.10185417.

[10] S. Liao et al., “First Demonstration of Monolithic CFET Inverter at 48nm Gate Pitch Toward Future Logic Technology Scaling,” to be presented at the 2024 International Electron Devices Meeting (IEDM).

[11] M. M. S. Aly et al., “Energy-Efficient Abundant-Data Computing: The N3XT 1,000×”, in Computer ( Volume: 48, Issue: 12, December 2015), DOI: 10.1109/MC.2015.376.

[12] H. Wu et al., “Flip 3D (F3D): A Novel 3D Integration Technology with Dual-side Integration Capabilities,” 2024 IEEE 17th Int. Conf. Solid-State Integr. Circuit Technol..

[13] url: https://space.bilibili.com/3546639490878157