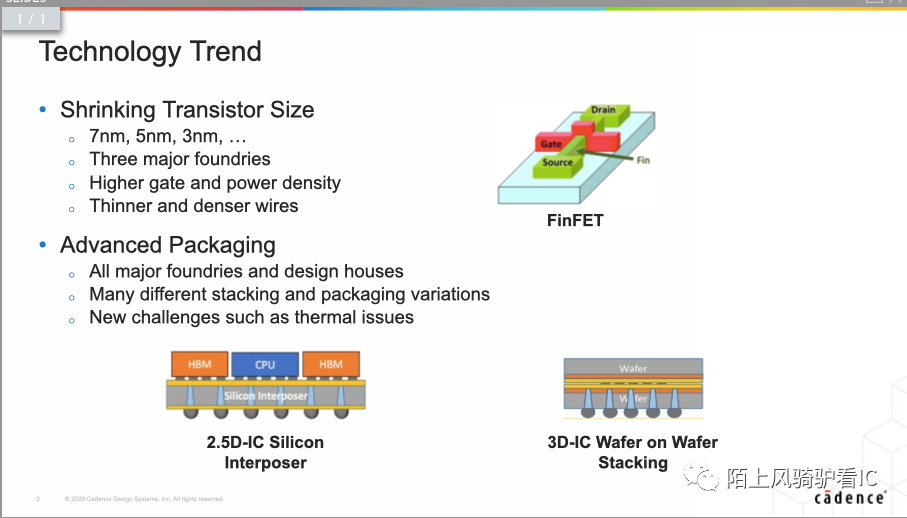

在后摩尔时代,半导体工艺已经出现了两条清晰的发展路线:一方面是大的晶圆厂商继续向物理极限缩小晶体管尺寸,以达到单晶片性能的增加和功耗的减少,而这会导致芯片上晶体管密度和功耗密度的上升,而且每一层金属导线也会变得更细,更密集;另一方面是越来越多的晶圆厂商加入到通过采用先进封装技术来实现芯片性能和集成度提升的阵营,比如越来越常见的2.5D 封装,不同种类的晶片通过中介层相互连接在一起,还有最新的3D 封装,不同种类的晶片通过TSV 堆叠在一起,虽然单晶片设计已经比较成熟,但将很多异构晶片堆叠封装在一起会带来很多新问题,例如芯片过热的问题。

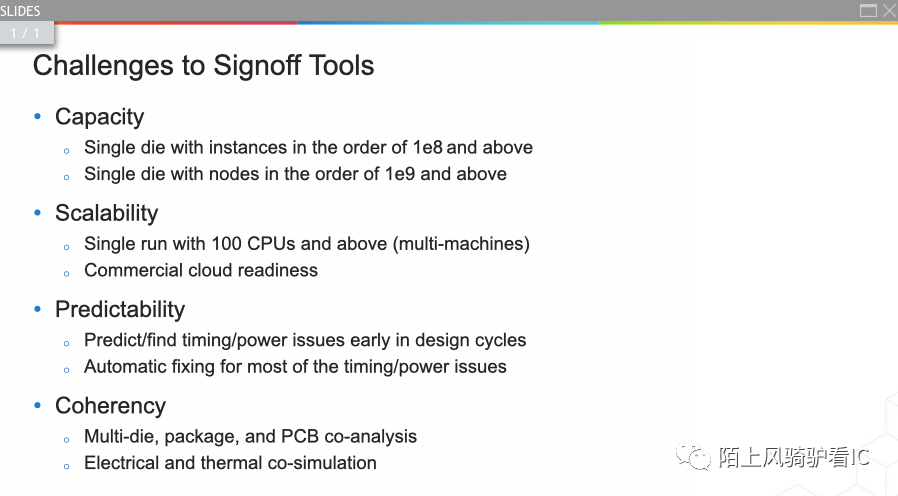

那这些技术革新对签收工具有哪些影响呢?首当其冲的就是工具的容量及可扩展性,在两三年以前,单晶片集成上千万门就称得上是大芯片了。但如今,一块芯片没有上亿门,电源网络没有上十亿节点都不好意思称之为『大』。这就要求工具不该有任何局限,不管芯片有多大,在机器资源足够的情况下,工具都能够完成分析。另一方面,随着功能的增加,芯片设计越来越复杂,签收流程和需要考虑的因素越来越多,签收也越来越困难。这就需要签收工具从『单点分析工具』升级成为『联动分析工具』,其可以帮助设计者及早预见和发现可能出现的时序和功耗问题,并且在绝大部分情况下能够完成自动修复。

同时,针对全系统设计,还需要一整套系统级分析仿真工具,能够同时考虑和优化多晶片、封装跟电路板的影响,还要能把不同物理场,如电和热,放在一起进行耦合分析。C 记电热分析全家桶,可以极好的应对这些挑战。

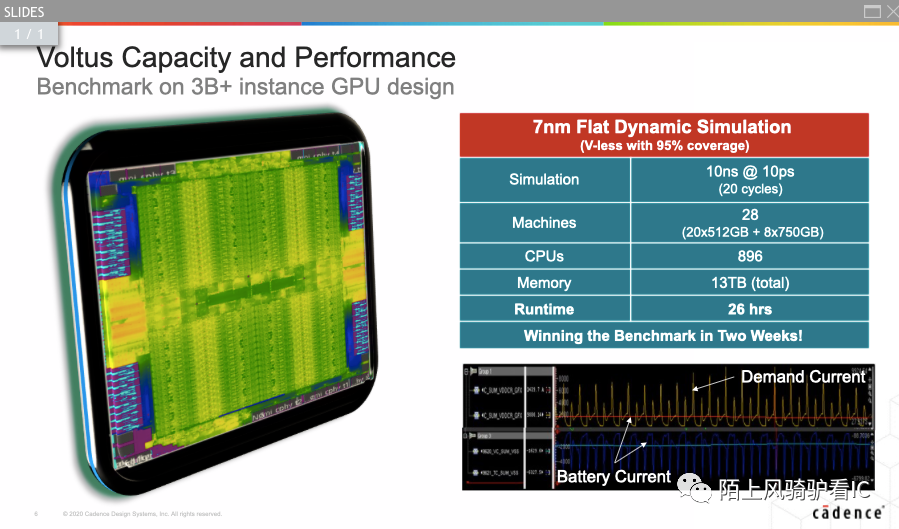

通常,在功耗签收时最常见的做法是把整个芯片放在一起进行电压降和电迁移的仿真分析。随着芯片规模剧增,对功耗签核工具提出了极大挑战,为了应对这一挑战C 记从两年以前开始就对Voltus 内核进行升级,并在去年全部完成。这次升级最重要的一个方面是无限扩展了Voltus 的仿真能力,彻底实现了无论芯片多大,只要机器资源够Voltus 就都能完成分析。一个栗子:一个30亿门级GPU芯片,Voltus 共只用了13T内存,使用近千个CPU,在一天时间完成所有仿真。

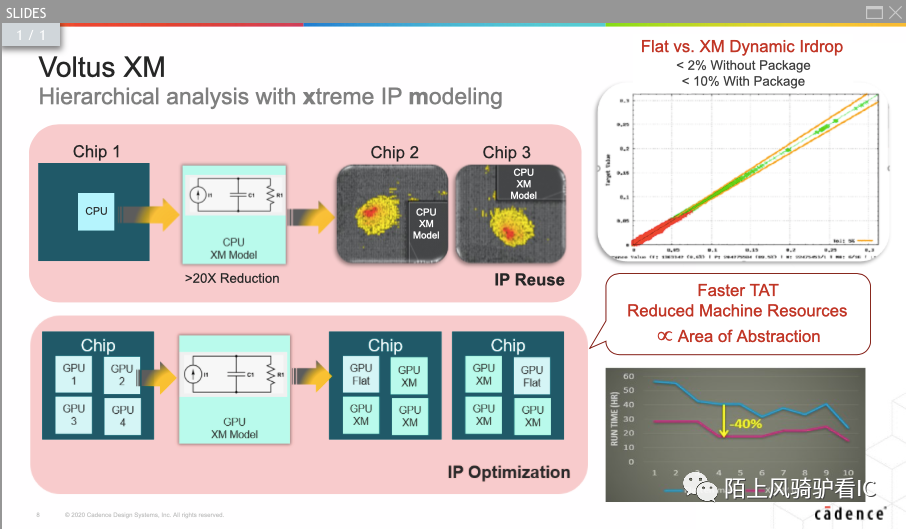

但一味提高工具容量是不能够解决所有问题的,例如机器资源紧张。芯片规模逐年成倍增长并不代表内部机器资源能成倍增长,功耗签收周期能成倍延长。所以Voltus 另辟蹊径,开发出了一套层级分析方法,通过对重复模块建模的方式来提升签收效率,减少对资源的要求。这一神器叫Voltus XM. XM 代表extreme modeling, 利用XM,用户可以对重复IP 构建模型,一方面可以减少仿真时间和机器资源,另一方面可以通过模型搭建一个完整的芯片环境来优化某些重要的模块。实测XM 可以减少40% 以上的仿真时间,同时保持2% 以内的精度。

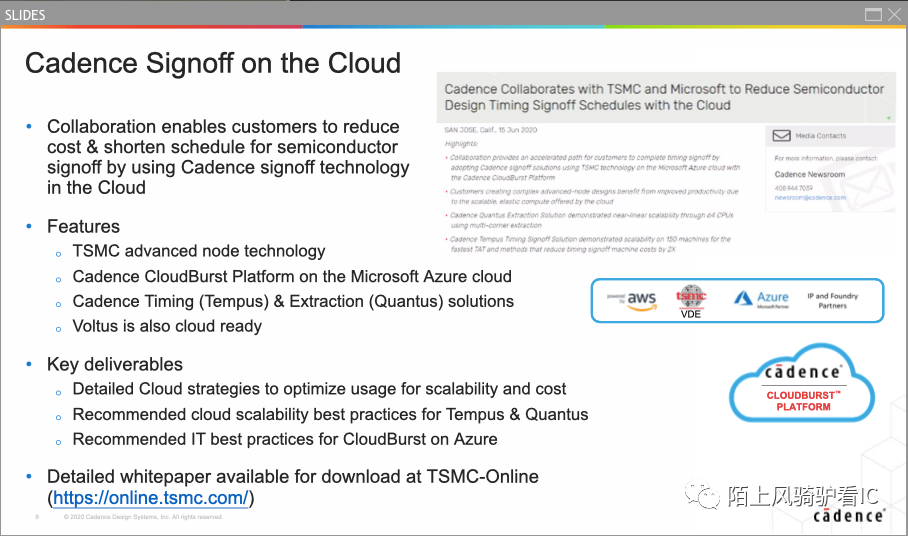

提及签收机器资源紧张的问题,就不能不提到云。虽然有一部分客户仍对云的数据安全性心存疑虑,但已有很多客户都在考虑使用云来解决内部机器资源紧张的问题,特别是对机器资源消耗特别大的签收阶段。C 记在这方面很早就已开始布局,并且在去年发布了全新一代云平台Cloudburst, 这个平台是可以架构在任何一个云服务商上如AWS和Azure。

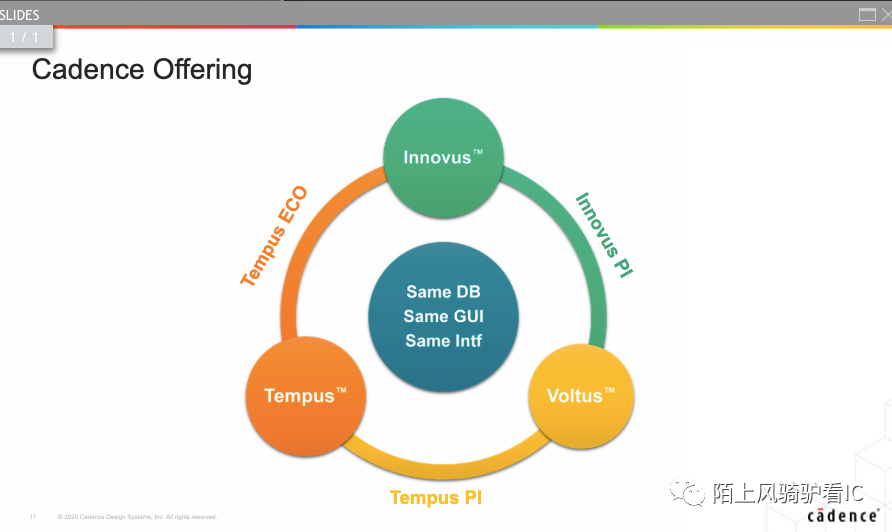

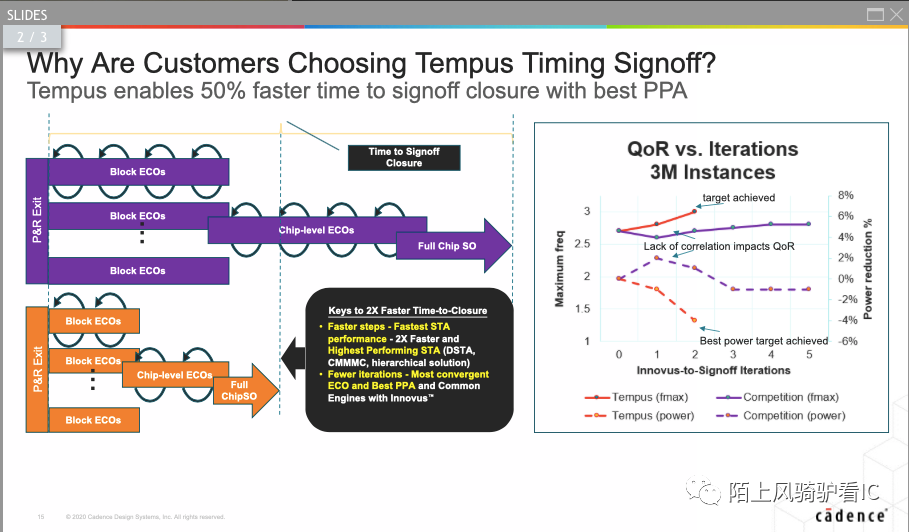

C 记拥有全套设计平台和全套分析工具,也一直致力于把所有工具整合在一起,以给客户提供统一的用户界面和丰富的解决方案,实现一加一大于二的目的。将时序和功耗签收和物理实现整合在一起,可以在设计实现过程中及时发现和修复时序和功耗问题,而不是把所有问题都推迟到签收阶段来发现和修复,这就孕育出了Innovus PI 和Tempus ECO . 另一方面,通过把时序和功耗放在一起考虑来找到那些会因为压降而造成时序违例的关键路径,这就催生了Tempus PI。

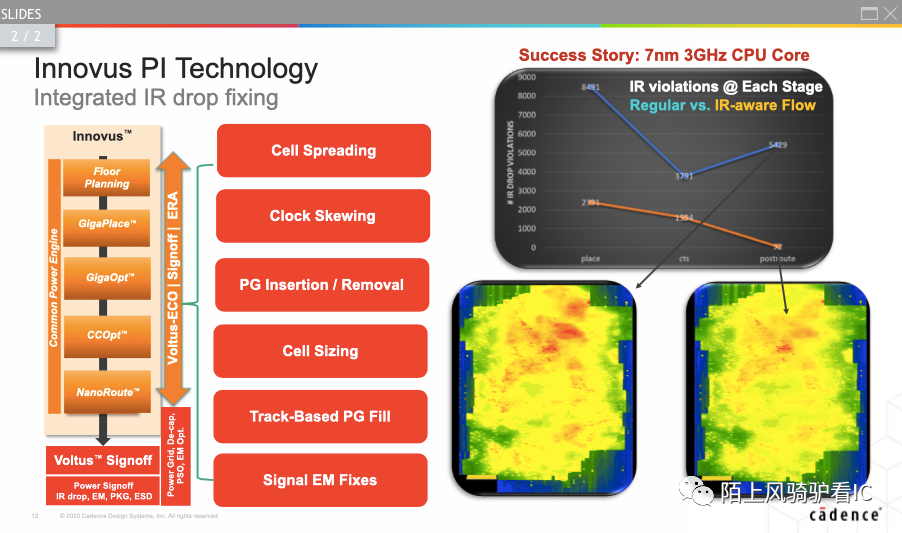

在Innovus PI 中,通过在布局和布线阶段插入Voltus 分析来及早发现设计中可能出现的电压降和电迁移方面的问题。然后利用cell spreading, cell sizing, clock skewing, PG insertion/removal, signal EM fix 来及时修复这些问题,以尽量减少最后在签收阶段违规的数量。可以通过下图右边这个例子看到,利用Innovus PI 可以把最终的电压降违例减少上百倍,而且这个流程完全自动,不需要人力介入。

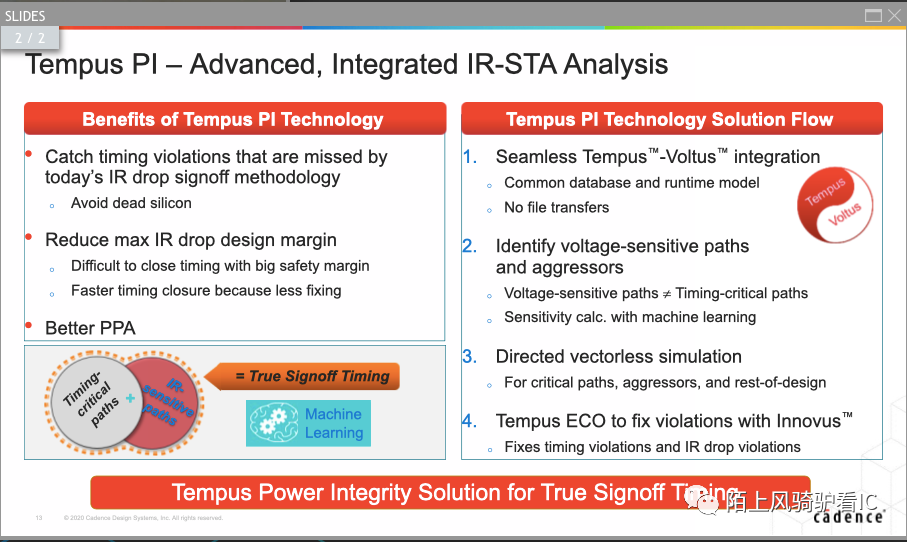

众所周知功耗会影响时序,但在传统流程里,时序和功耗总是 单独签收的。在最新工艺里,它们之间的相互影响越来越大,时序违例不能被传统流程抓到进而导致整块芯片不能正常工作。Tempus PI 通过将Tempus 和Voltus 进行整合和信息交互,来找出那些对电压降很敏感的关键路径,然后通过订制分析找出那些可能因电压降出现时序违例的路径,在找到这些路径之后,可以通过Tempus ECO 在Innovus 里面修复。通过Tempus PI 可以一方面提高时序签收的信心,另一方面也能减少为降低电压降而增加的设计冗余,从而达到提升PPA的目的。

在先进工艺中Tempus ECO 跟Innovus 的配合堪称天衣无缝,利用Tempus 快速的静态时序分析,通过快速高效的ECO 来减少迭代次数,进而实现两倍以上的时序设计收敛周期的减少和总体PPA的提升。

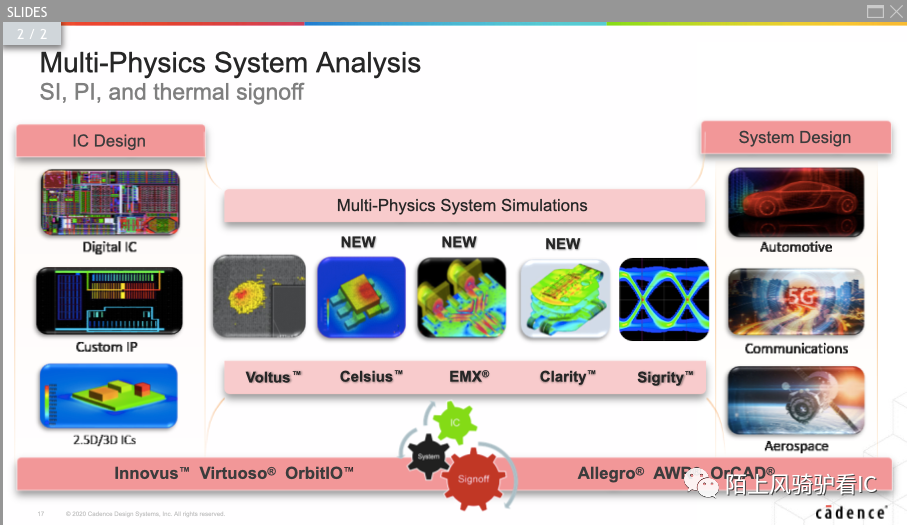

在对系统整体性能极致追求的今天,系统整体设计和优化变得越来越重要。C 记在系统方面的投入也越来越大,拥有一整套从芯片设计到系统设计的平台软件,一系列跨越电场、热场、电磁场的系统分析软件,例如Voltus 用于芯片功耗电源完整性分析,Celsius 用于系统热力分析,EMX 用于电感电容抽取,Clarity 3D 用于电磁场分析,Sigrity 工具用于封装和电路板信号完整性分析。

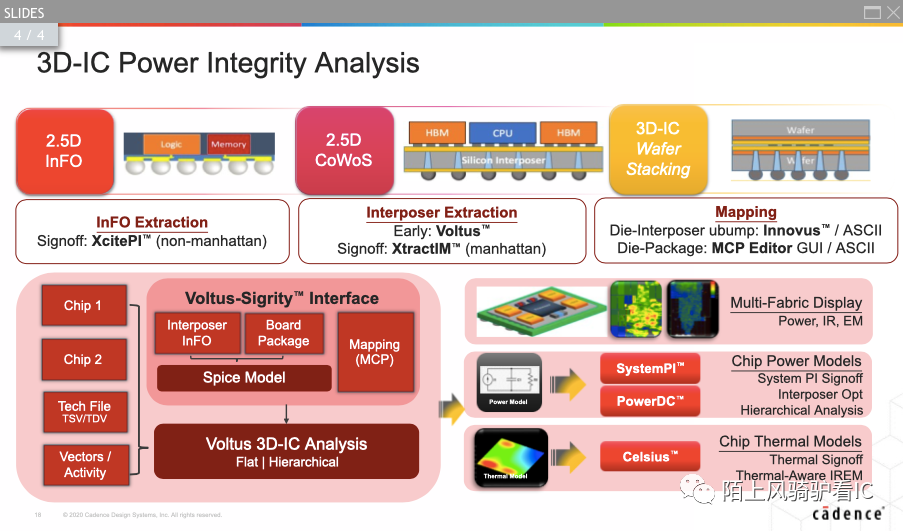

先进封装发展到现在已经演变成一个非常复杂的系统,一方面是有很多不同的堆叠的方式,例如2.5D Info, 2.5D CoWoS 以及3D WoW; 另一方面是每个封装里会有很多不同种类的晶圆采用不同平台进行设计:例如package 和Info die 是用Allegro 设计的,Logic die 是通过Innovus 设计的,Memory die 是用Virtuoso 设计的。不管是哪种堆叠,或者是用哪个平台设计出来的,都需要有一套完整的签收解决方案。C 记解决方案里面,对每个组成部分都能做详细的分析,也都能生成简化模型以供其他部分用来做全局分析。例如2.5D CoWoS 中,可以使用Sigrity 的XtractIM 来生成封装模型,然后利用Voltus 对整个芯片进行完全展平分析。其中,die2interposer 的映射是由Innovus 生成,die2package 的映射是由MCP Editor 生成。Voltus可以通过特有的层级分析方式来减小整个系统分析的机器资源消耗,另外为了处理越来越大的2.5D 和3D 设计,Voltus对矩阵求解器的性能做了很大的提升,让它能够轻松对拥有几万个bump 的系统做per bump 分析。

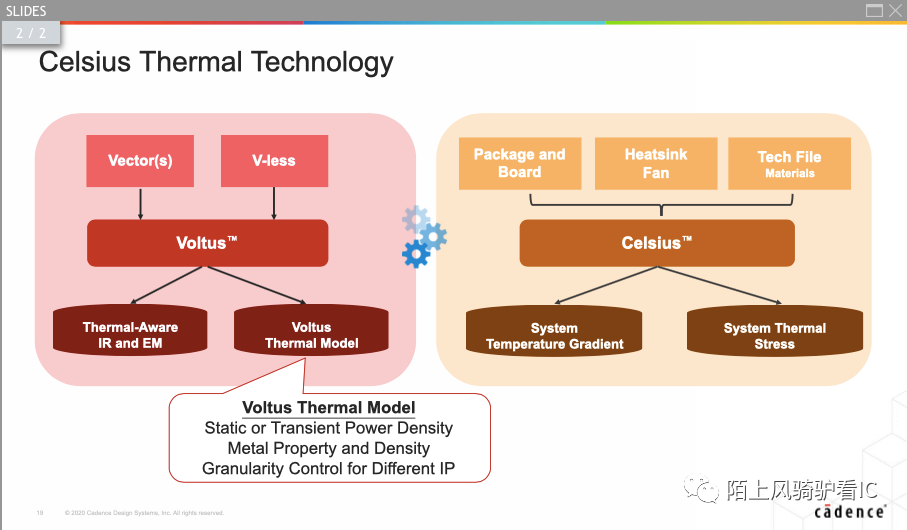

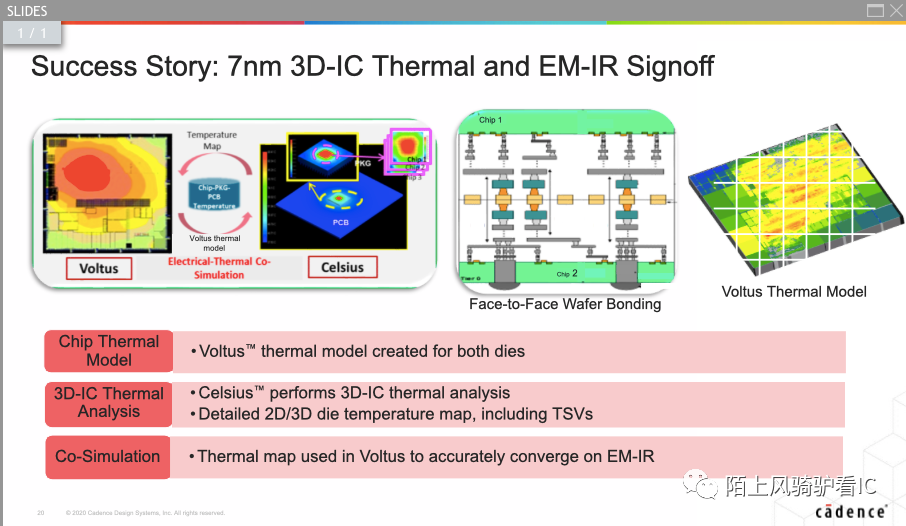

在先进封装里,众多晶片在一个非常狭小紧凑的环境里堆叠在一起,散热成了亟需解决的问题,为了把电和热放在一起进行耦合分析,C 记将Voltus 和去年新发布的热学分析工具Celsius 整合在一起,提供了一套完整的解决方案。一方面,可以通过Voltus 生成Voltus Thermal Model, 这个模型里包含了静态或者动态的功耗密度,芯片金属性质和密度,以及对某些重要模块建立的精细模型。然后Celsius 可以利用这个模型带上其他的系统组成部分,比如封装,电路板,散热片来进行精确的系统温度和热应力仿真,利用Celsius 生成的芯片温度分布,Voltus 可以做thermal-aware 的电压降和电迁移的分析。

Voltus 和Celsius 的耦合分析流程已在7nm 的3DIC 芯片上流片成功。

纵观人类科技史,任何一次科学发现跟技术革新在给人类带来巨大福泽的同时必定有挑战伴之而生,而每一次都会有人类中的佼佼者站出来冲在前面,他们披荆斩棘,带领着全人类翻过一座又一座的高山。不知人类何时才能造出《三体》中的智子,但只要我们笃定相信并足够勤勉,终有一日,积少成多必将迎来技术链爆炸。

驴说IC